# ESCUELA POLITÉCNICA NACIONAL

# **ESCUELA DE INGENIERÍA**

## DISEÑO E IMPLEMENTACIÓN DE FILTROS FIR CON PARÁMETROS VARIABLES EN TIEMPO REAL UTILIZANDO LA VENTANA DE KAISER

PROYECTO PREVIO A LA OBTENCIÓN DEL TÍTULO DE INGENIERO EN ELECTRÓNICA Y TELECOMUNICACIONES

OLEAS VILLALBA FAUSTO GERARDO

QUINTANA HERMOSA WILSON HERNÁN

DIRECTOR: ING. MARÍA SOLEDAD JIMÉNEZ CO DIRECTOR: ING. FERNANDO VÁSQUEZ

Quito, febrero de 2002

## **AGRADECIMIENTO**

A la Ing. María Soledad Jiménez por la acertada conducción del presente Proyecto de Titulación, al Ing. Fernando Vásquez por la colaboración permanente, a nuestros amigos por su voz de apoyo incondicional brindada.

## **DEDICATORIA**

A mis padres que con su infinito amor, supieron guiarme en la personificación de mi vida.

A mis hermanos Mónica, Bertha y Edgar que comprendieron el valor de este reto y estimularon cada paso dado al objetivo trazado.

Fausto

## DEDICATORIA

A Dios Todopoderoso por la vida, salud y fe que otorga a toda mi familia.

A mis padres y hermanos por el apoyo y amor incondicional.

A la Ing. María Soledad Jiménez por su acertada dirección.

Al Ing. Fernando Vásquez por su enseñanza y amistad.

A mis amigos,.... no será la última.

A todos mis compañeros que sin saber que me apoyaban,....lo hacían.

Gracias Total.

Wilson Hernán Quintana Hermosa

## PRESENTACIÓN

A principio de los años cincuenta el tratamiento de señales se hacia generalmente con sistemas analógicos que se realizaban con circuitos electrónicos o incluso con dispositivos mecánicos. Aunque los computadores digitales estaban ya disponibles el costo era alto y de capacidad limitada.

Las primeras aplicaciones del tratamiento digital de señales no se podían realizar en tiempo real: a menudo eran necesarios minutos o incluso horas de tiempo de computador para procesar solo algunos segundos de datos. El tratamiento de señales mediante computadoras digitales ofrecía tremendas ventajas de flexibilidad, el computador se utilizaba para simular un sistema de tratamiento de señales analógicas.

El descubrimiento y la posterior proliferación de los microprocesadores preparó el terreno para las realizaciones de bajo costo de los sistemas de tratamiento de señales en tiempo discreto, los primeros microprocesadores eran demasiado lentos para implementar en tiempo real la mayoría de los sistemas de procesamiento digital de señales.

A mediados de los ochenta la tecnología de circuitos integrados había avanzado hasta el nivel de permitir la realización de microcomputadores en punto fijo y en punto flotante con arquitecturas especialmente diseñadas para realizar algoritmos de tratamiento de señales en tiempo discreto.

El presente Proyecto de Titulación recoge todos los beneficios que brinda en la actualidad un procesador digital de señal para la implementación de filtros digitales en tiempo real; la utilización de estos filtros o el reemplazo por los filtros analógicos ya existentes en sistemas más complejos, ayudará a obtener como resultado un mayor rendimiento en el objetivo final de cada sistema que involucre el filtrado de señales en tiempo real.

### RESUMEN

South March 1997

San Array

La rápida evolución de los computadores y los microprocesadores digitales junto con algunos importantes desarrollos teóricos, como el algoritmo de la Transformada rápida de Fourier (FFT), fueron la causa de un importante desplazamiento hacia las tecnologías digitales naciendo así el campo del tratamiento digital de señales.

Con la llegada de los Procesadores Digitales de Señal se abre un nuevo campo para el diseñador de sistemas, ya que se puede implementar sistemas que requieren una gran capacidad de proceso con un costo mucho menor que cualquiera de las soluciones existentes.

Los métodos de diseño de filtros FIR son relativamente simples, pero no proporcionan un buen control sobre los parámetros de los mismos, por lo cual generalmente éstos son diseñados utilizando métodos de prueba y error hasta encontrar el filtro que satisfaga las características deseadas.

Un método interesante para solucionar el problema antes mencionado ha sido desarrollado por Kaiser y permite diseñar filtros FiR con características predefinidas.

## CERTIFICACIÓN

Certifico que el siguiente trabajo fue realizado por Oleas Villalba Fausto Gerardo y Quintana Hermosa Wilson Hernán, bajo mi supervisión.

MSć. Vng. María Soledad Jiménez

DIRECTOR DE PROYECTO

ng. Fernando Vásquez

CO D'IRECTOR DE PROYECTO

# **CONTENIDO**

| RESUM   | 1EN     |           |                                           | V     |

|---------|---------|-----------|-------------------------------------------|-------|

| PRESEN  | ITACIÓ  | N         |                                           | . vi  |

| LISTA I | DE FIC  | GURAS     |                                           | ×     |

| LISTA I | DE TA   | BLAS      |                                           | iiix. |

|         |         |           |                                           |       |

| CAPÍTI  | ULO 1   | . CONC    | EPTOS GENERALES                           | 1     |

| 1.1     | FILTR   | ROS DIGIT | ALES                                      | 1     |

|         | 1.1.1   | FILTRO    | OS DIGITALES vs. FILTROS ANALÓGICOS       | 3     |

|         | 1.1.2   | VENTA     | JAS DE LOS FILTROS DIGITALES              | 5     |

|         | 1.1.3   | DESVE     | NTAJAS DE LOS FILTROS DIGITALES           | 6     |

| 1.2     | MICR    | OPROCE    | SADORES DSP                               | 7     |

|         | 1.2.1   | PROCE     | ESAMIENTO DIGITAL DE SEÑALES              | 7     |

|         | 1.2.2   | PROCE     | ESADOR DIGITAL DE SEÑAL (DSP)             | 8     |

|         |         | 1.2.2.1   | Arquitectura típica de un DSP             | 11    |

|         |         | 1.2.2.2   | Áreas de desarrollo del DSP               | 12    |

|         |         | 1,2.2.3   | Familia de Microprocesadores ADSP-2100    | 13    |

| 1.3     | MODU    | JLO DE D  | ESARROLLO PARA EL ADSP 2181               | 17    |

| CAPÍTI  | TI () 2 | DISEÑ     | O DE FILTROS FIR                          | 21    |

|         |         |           | N                                         |       |

| 2.1     |         |           |                                           |       |

|         | 2.1.1   |           | TROS DE LOS FILTROS DIGITALES             |       |

|         |         | 2.1.1.1   | · ·                                       |       |

|         | 040     | 2.1.1.2   | Parámetros en el Dominio de la Frecuencia |       |

|         |         |           | DIGITALES FIR e IIR                       |       |

|         |         |           | ARIOS SOBRE LOS FILTROS FIR e IIR         |       |

| 2.2     |         |           | DISEÑO                                    | .33   |

|         | 2.2.1   |           | INACIÓN DE LAS ESPECIFICACIONES DE UN     | 0.5   |

|         | 000     |           | EN TIEMPO DISCRETO                        |       |

|         | 2.2.2   | METODO    | DE VENTANAS PARA FILTROS FIR              | 38    |

|       |        | 2.2.2.1 | Propiedades de las ventanas comúnmente                   |     |

|-------|--------|---------|----------------------------------------------------------|-----|

|       |        |         | utilizadas                                               | 42  |

|       |        | 2.2.2.2 | Incorporación de la fase lineal generalizada             | 47  |

|       |        | 2.2.2.3 | Fase lineal de un filtro pasa bajo                       | 49  |

|       |        | 2.2.2.4 | Fase lineal de un filtro pasa alto                       | 50  |

|       |        | 2.2.2.5 | Fase lineal de un filtro pasa banda                      | 51  |

|       |        | 2.2.2.6 | Fase lineal de un filtro rechaza banda                   | 51  |

| 2.3   | MÉTO   | OO DE K | AISER                                                    | 52  |

|       | 2.3.1  | RELA    | CIÓN DE UN FILTRO PASA BAJO CON LOS                      |     |

|       |        | FILTE   | ROS FUNDAMENTALES                                        | 55  |

|       | 2.3.2  | EJEM    | IPLOS DE DISEÑO DE FILTROS DIGITALES                     |     |

|       |        | MEDI    | ANTE LA VENTANA DE KAISER                                | 60  |

|       |        | 2.3.2.1 | Diseño de un filtro pasa bajo                            | 60  |

|       |        | 2.3.2.2 | Diseño de un filtro pasa alto                            | 64  |

|       |        | 2.3.2.3 | Diseño de un filtro pasa banda                           | 65  |

|       |        | 2.3.2.4 | Diseño de un filtro rechaza banda                        | 65  |

|       | 2.3.3  | RELA    | CION DE LA VENTANA DE KAISER CON                         |     |

|       |        | OTRA    | AS VENTANAS                                              | 68  |

| CAPÍT | IILO 3 | IMPLE   | MENTACION DE FILTROS FIR                                 | 70  |

|       |        |         | ONES INICIALES                                           |     |

| 3.1   | 3.1.1  |         | AS EN EL DISEÑO E IMPLEMENTACIÓN DE LO                   |     |

|       | 3.1.1  |         | OS DIGITALES                                             |     |

|       |        |         |                                                          |     |

|       |        | 3.1.1.1 | Especificación de las propiedades deseadas de<br>Sistema |     |

|       |        | 2112    | Aproximación de las propiedades mediante un              | / 4 |

|       |        | 3.1.1.2 | sistema causal en tiempo discreto                        | 96  |

|       |        | 2112    | Realización del Sistema                                  |     |

| 3.2   | EL MIC |         | CESADOR ADSP-2181                                        |     |

| 3.2   | 3.2.1  |         | RIPCIÓN GENERAL                                          |     |

|       | 3.2.1  |         | JITECTURA INTERNA                                        |     |

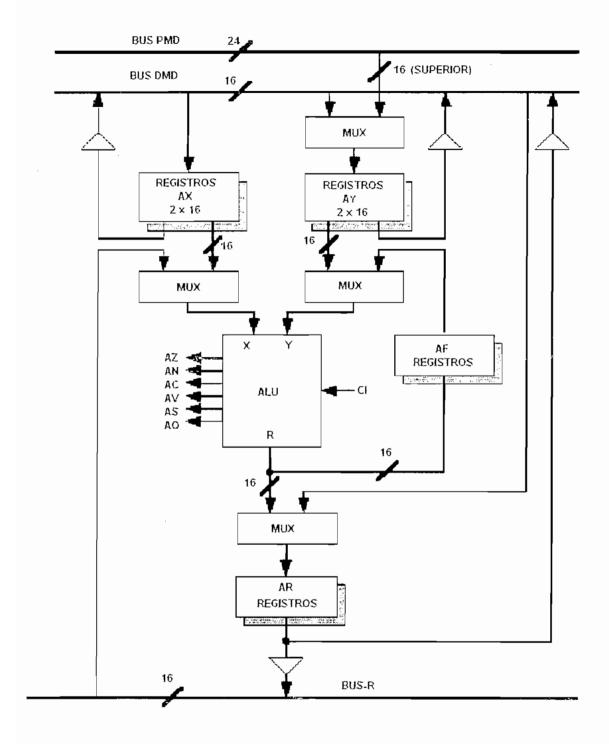

|       | 3.2.2  |         | AD ARITMÉTICA LÓGICA                                     |     |

|       | J.Z.J  | ONID    | AD ANTHRE HUA LUGIUA                                     | 99  |

.

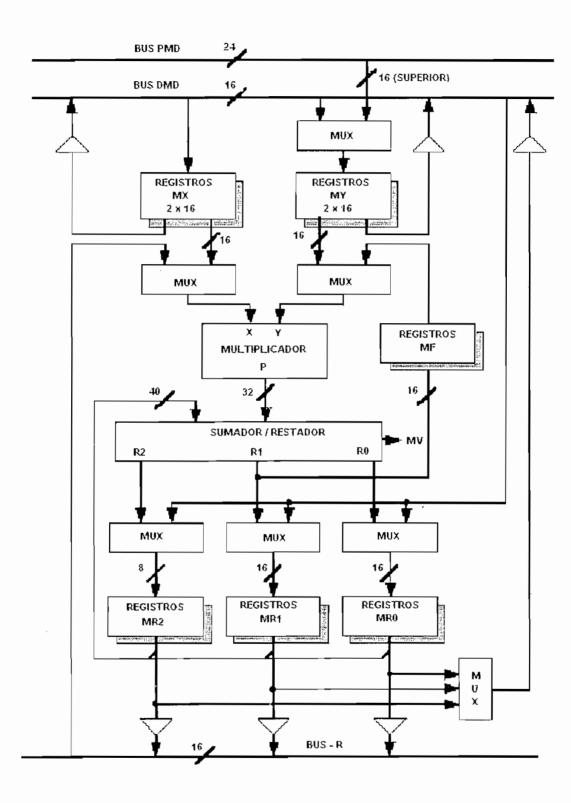

|        | 3,2.4  | MULTIPLICADOR ACUMULADOR103                    |

|--------|--------|------------------------------------------------|

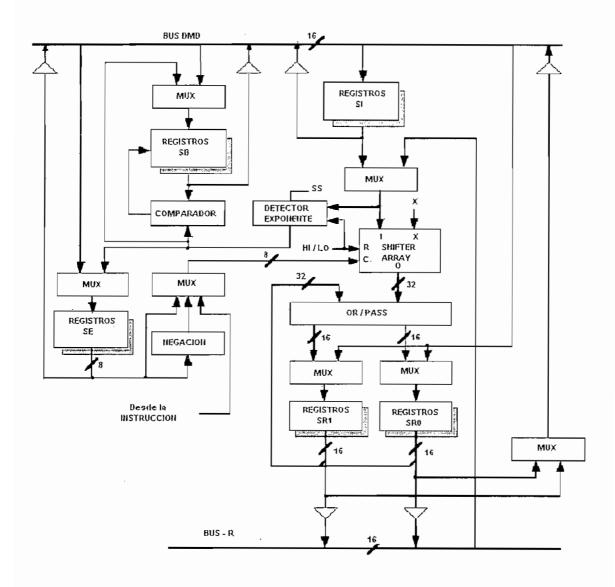

|        | 3.2.5  | UNIDAD DE DESPLAZAMIENTO106                    |

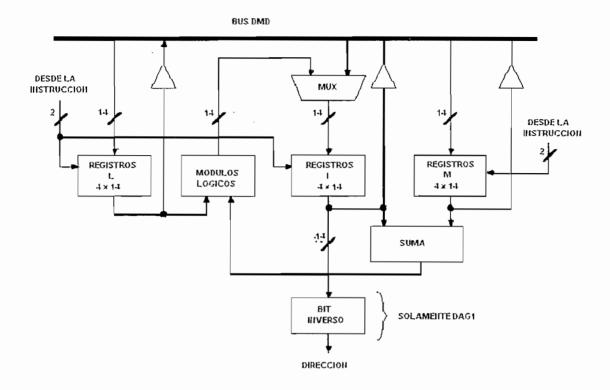

|        | 3,2.6  | GENERADORES DE DIRECCIONES DE DATOS111         |

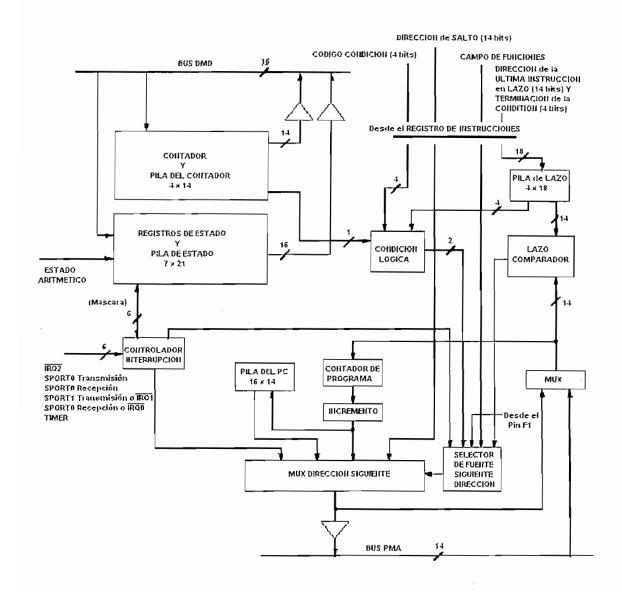

|        | 3.2.7  | SECUENCIADOR DE PROGRAMA113                    |

| 3.3    | EL EZ  | <b>– KIT LITE</b> 116                          |

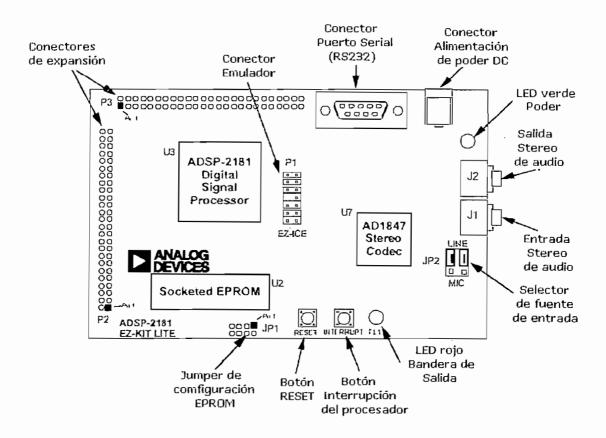

|        | 3.3.1  | DESCRIPCIÓN DEL HARDWARE EZ – KIT LITE 116     |

|        | 3.3.2  | ESPECIFICACIONES DE LA TARJETA EZ-Lab121       |

|        |        | 3.3.2.1 Conectores                             |

|        |        | 3.3.2.2 Switches123                            |

|        |        | 3,3,2,3 Indicadores                            |

|        |        | 3.3.2.4 Conectores de Expansión124             |

|        | 3.3.3  | DESCRIPCIÓN DEL SOFTWARE DEL EZ – KIT LITE 125 |

| 3.4    | PROG   | RAMAS DESARROLLADOS PARA LOS FILTROS FIR 129   |

|        |        |                                                |

| CAPÍT  | ULO 4. | RESULTADOS Y APLICACIONES135                   |

| 4.1    | EXPO   | SICION DE LOS RESULTADOS135                    |

|        | 4.1.1  | RESULTADO DEL FILTROS PASA BAJO136             |

|        | 4.1.2  | RESULTADO DEL FILTROS PASA ALTO141             |

|        | 4.1.3  | RESULTADO DEL FILTROS PASA BANDA144            |

|        | 4.1.4  | RESULTADO DEL FILTROS RECHAZA BANDA146         |

| 4.2    | ANALI  | SIS DE LOS RESULTADOS149                       |

| 4.3    | APLIC  | ACIONES153                                     |

|        |        |                                                |

| CAPÍT  | ULO 5. | CONCLUSIONES Y RECOMENDACIONES159              |

| BIBLIC | OGRAF  | IA163                                          |

| ANEX(  | OS     | 165                                            |

# LISTA DE FIGURAS

| Figura 1.1.  | Idea general de un filtro                                             | 2   |

|--------------|-----------------------------------------------------------------------|-----|

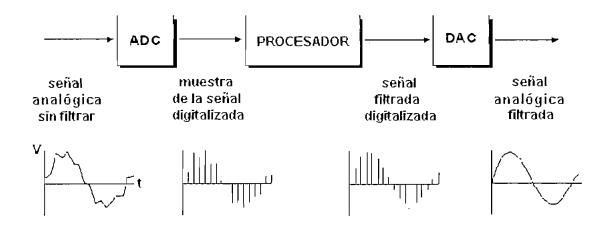

| Figura 1.2.  | Proceso de filtrado de una señal analógica                            | 3   |

| Figura 1.3.  | Arquitectura básica de los DSP                                        | 11  |

| Figura 1.4.  | Áreas de desarrollo de los DSP                                        | 13  |

| Figura 1.5.  | Áreas afines al Procesamiento Digital de Señales                      | 14  |

| Figura 1.6.  | Diagrama de bloques del ADSP-2181                                     | 18  |

| Figura 2.1.  | Parámetros de los filtros                                             | 23  |

| Figura 2.2.  | Parámetros para la evaluación de las características en el dominio de | el  |

|              | tiempo                                                                | 26  |

| Figura 2.3.  | Respuestas de frecuencia comunes                                      | 28  |

| Figura 2.4.  | Parámetros para la evaluación del desempeño en el dominio             |     |

|              | de la frecuencia                                                      | 29  |

| Figura 2.5.  | Respuesta impulsiva                                                   | 31  |

| Figura 2.6.  | Sistema básico para el filtrado en tiempo discreto de señales en tiem | ро  |

|              | continuo                                                              | 34  |

| Figura 2.7.  | Especificaciones de un filtro pasa bajo                               | 36  |

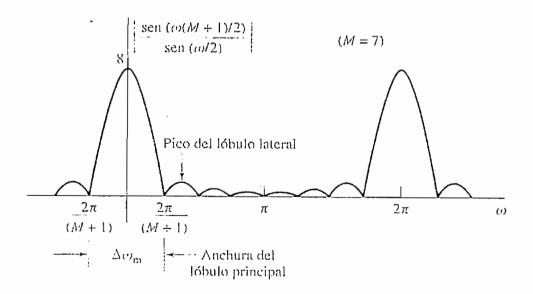

| Figura 2.8.  | Funciones típicas Hd(ejθ) y W(ej(ω-θ))                                | 40  |

| Figura 2.9.  | Módulo de la transformada de Fourier de una ventana rectangular       |     |

|              | (M=7)                                                                 | 41  |

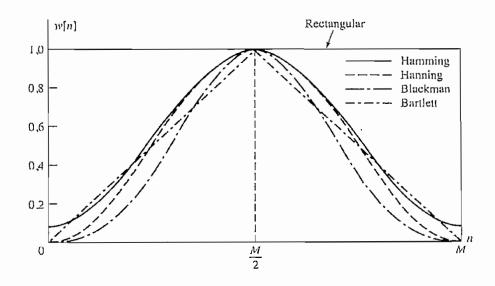

| Figura 2.10. | Ventanas comúnmente utilizadas                                        | 44  |

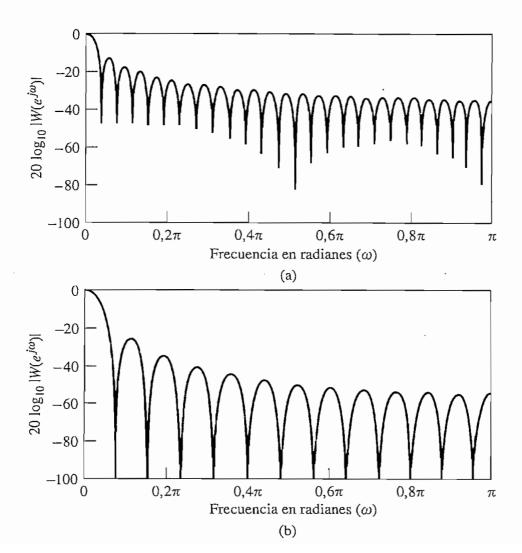

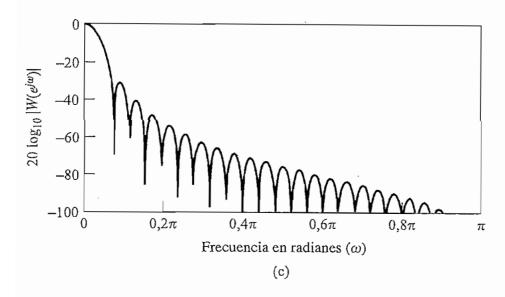

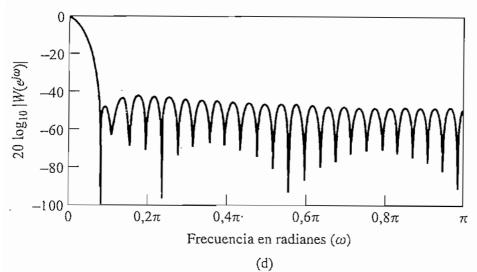

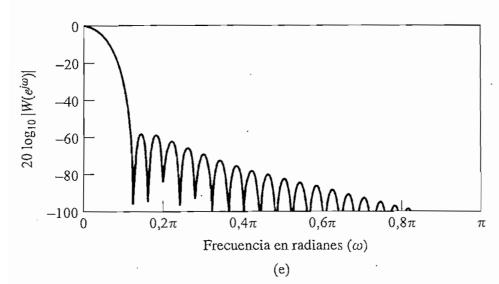

| Figura 2.11. | Transformadas de Fourier con M = 50 de las ventanas                   | 46  |

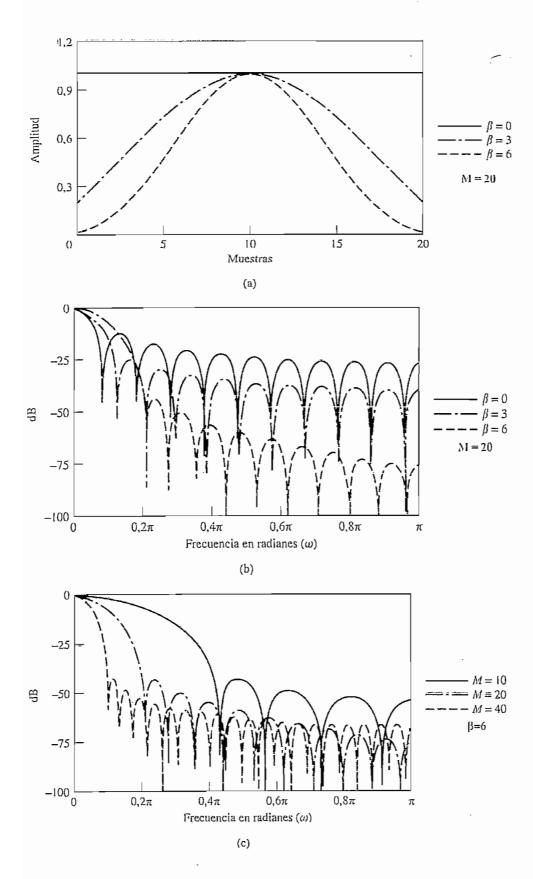

| Figura 2.12. | Ventanas de Kaiser para $\beta$ = 0, 3, 6 y M = 20                    | 53  |

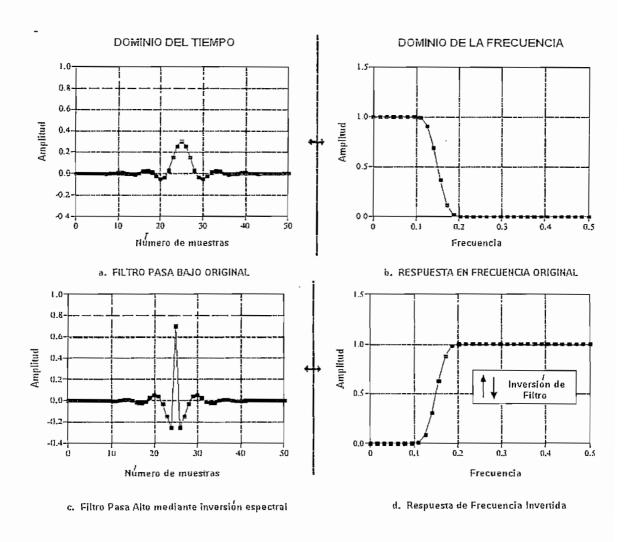

| Figura 2.13. | Transformación de un filtro pasa bajo a pasa alto                     | 56  |

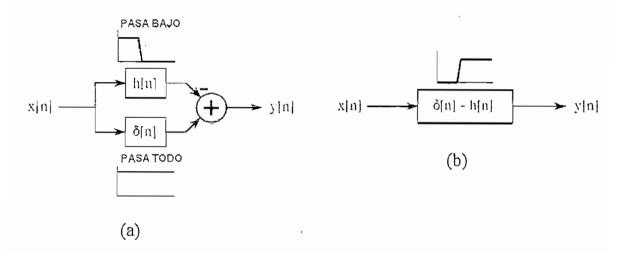

| Figura 2.14. | Diagrama de bloques de la inversión espectral                         | 57  |

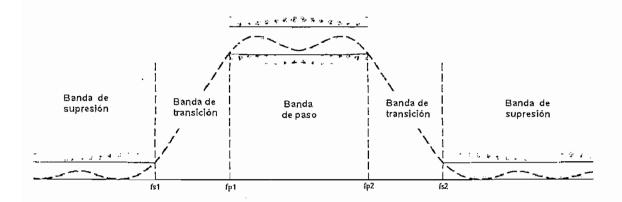

| Figura 2.15. | Parámetros de variación de un filtro pasa banda                       | 58  |

| Figura 2.16. | Parámetros de variación de un filtro rechaza banda                    | 59  |

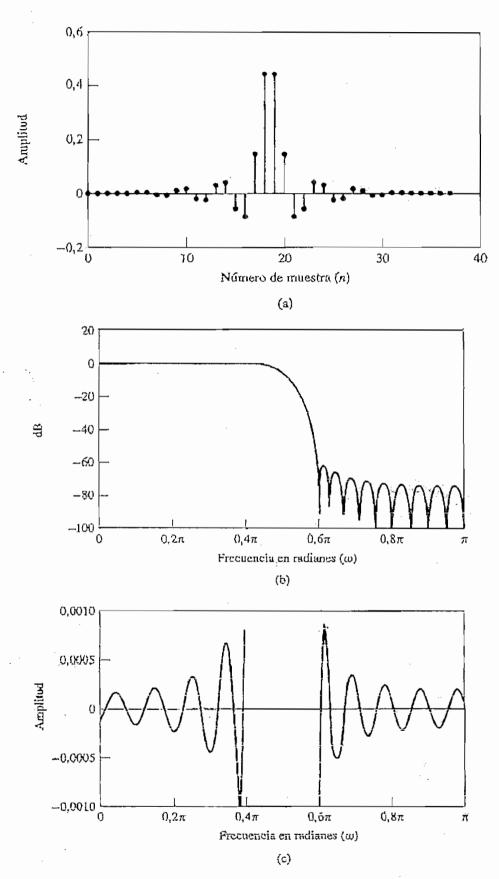

| Figura 2.17. | Funciones de respuesta del ejemplo de diseño de un filtro pasa bajo   |     |

|              | mediante la ventana de Kaiser                                         | 63  |

| Figura 3.1.  | Sistema básico para el filtrado en tiempo discreto de señales en tiem | про |

|              | contínuo                                                              | 74  |

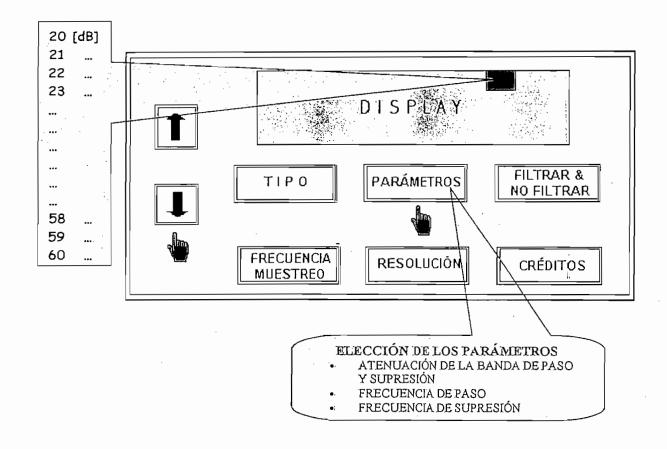

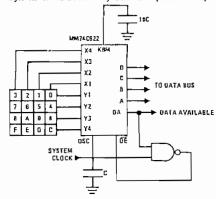

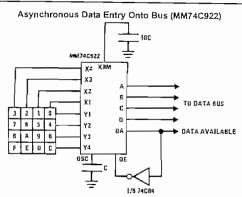

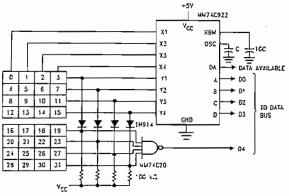

| Figura 3.2.    | Ingreso del factor de rizado mediante un teclado al DSP                      |

|----------------|------------------------------------------------------------------------------|

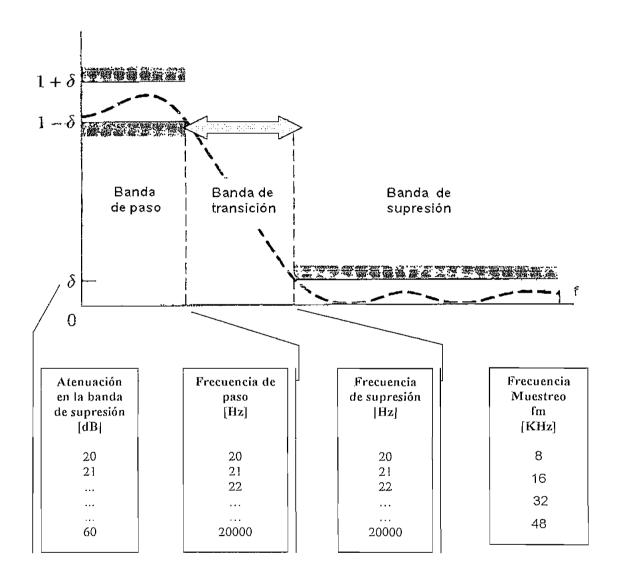

| Figura 3.3.    | Rango y determinación de los parámetros de un filtro pasa bajos 80           |

| Figura 3.4.    | Ingreso de las frecuencias de corte, supresión y muestreo                    |

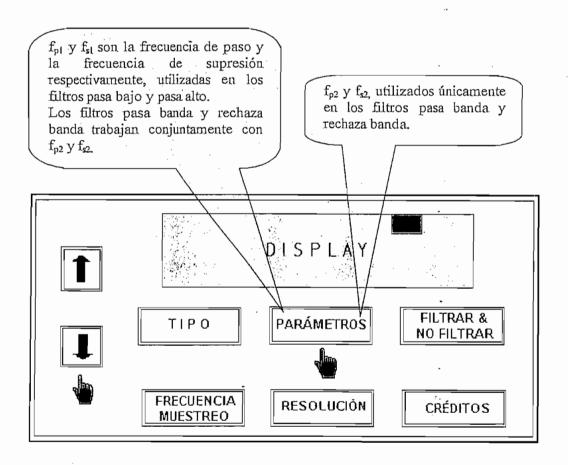

| •              | mediante un teclado al DSP                                                   |

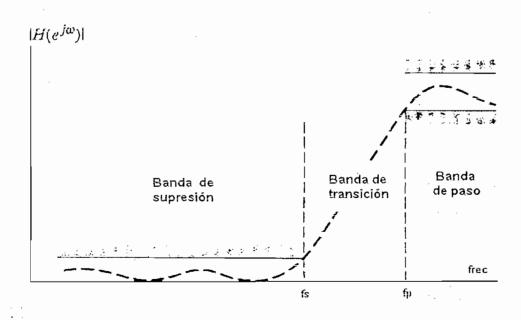

| Figura 3.5.    | Parámetros de variación de un filtro pasa alto                               |

| Figura 3.6.    | Parámetros de variación de un filtro pasa banda                              |

| Figura 3.7.    | Parámetros de variación de un filtro rechaza banda                           |

| Figura 3.8.    | Sistema de procesamiento en tiempo real sobre el que se implementa el        |

|                | filtro no recursivo                                                          |

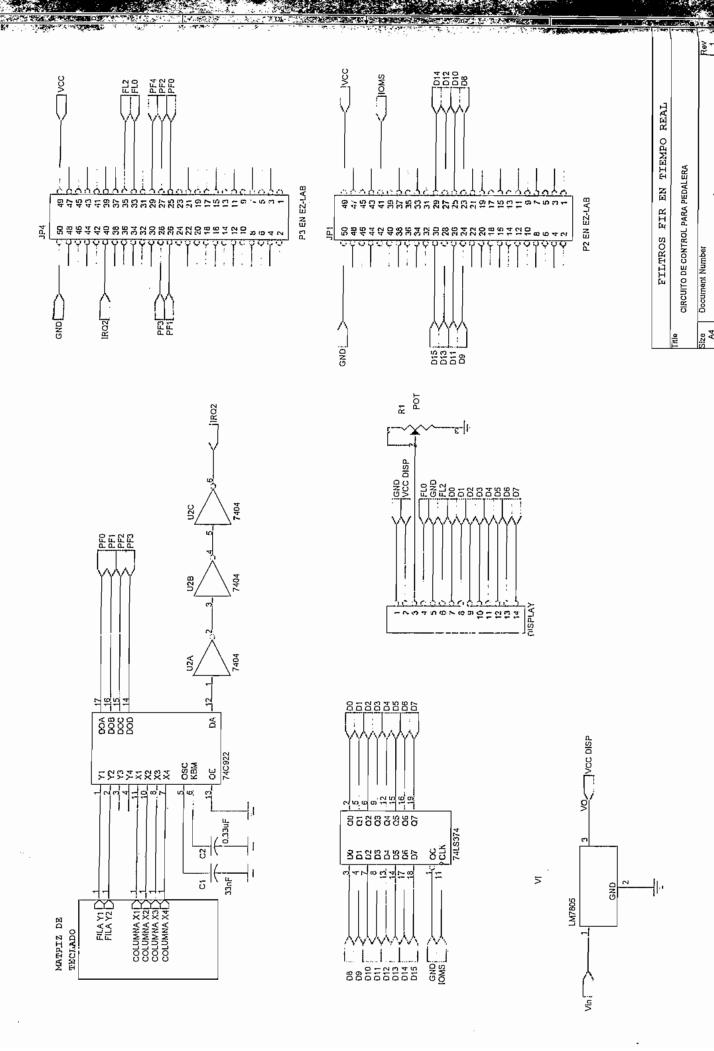

| Figura 3.9.    | Diagrama esquemático del sistema a implementarse91                           |

| Figura 3.10.   | Distribución física del teclado mediante el cual se ingresa los parámetros   |

|                | del filtro                                                                   |

| Figura 3.11.   | Matriz de display LCD                                                        |

| Figura 3.12.   | Arquitectura interna del microprocesador ADSP-210095                         |

| Figura 3.13.   | Arquitectura interna del ADSP-218196                                         |

| Figura 3.14.   | Diagrama de bloques de la ALU                                                |

| Figura 3.15.   | Diagrama de bloques del MAC                                                  |

| Figura 3.16.   | Diagrama de bloques de la unidad de desplazamiento                           |

| Figura 3.17.   | Diagrama de bloques de un generador de direcciones de datos 112              |

| Figura 3.18.   | Secuenciador de programas ADSP-2181                                          |

| Figura 3.19.   | Diagrama físico de la tarjeta EZ-Lab                                         |

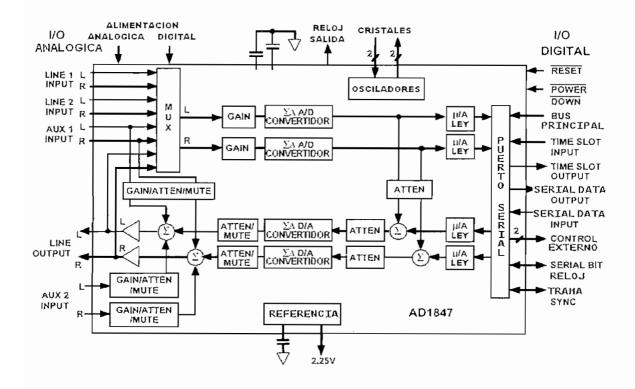

| Figura 3.20. J | Diagrama de bloques del AD1847119                                            |

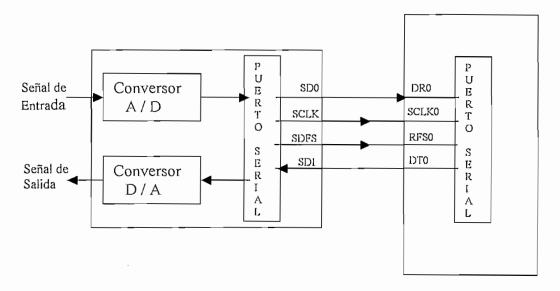

| Figura 3.21.   | Interfaz serial entre el ADSP-2181 y el AD1847                               |

| Figura 3.22.   | Selección de las señales de entrada                                          |

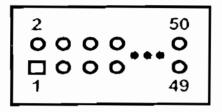

| Figura 3.23.   | Arreglo de un conector tipo header de 50 pines                               |

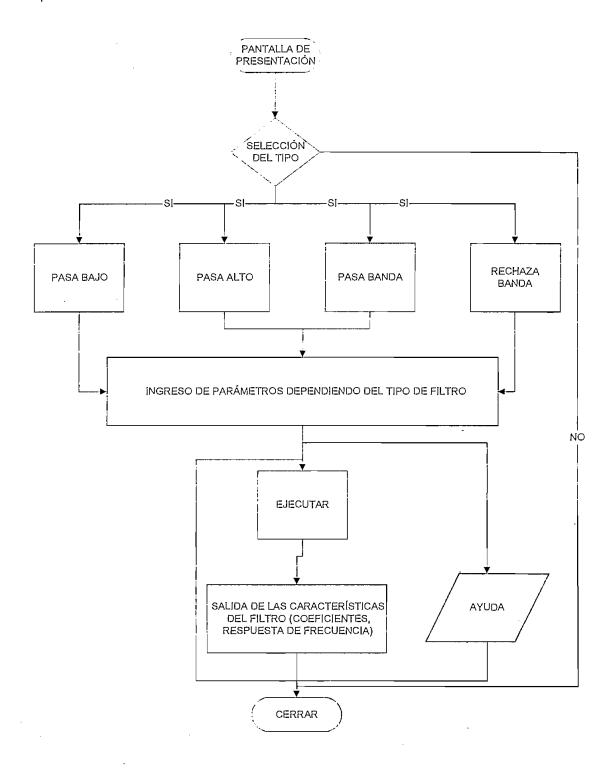

| Figura 3.24.   | Diagrama de Flujo del programa en Matlab 5.3                                 |

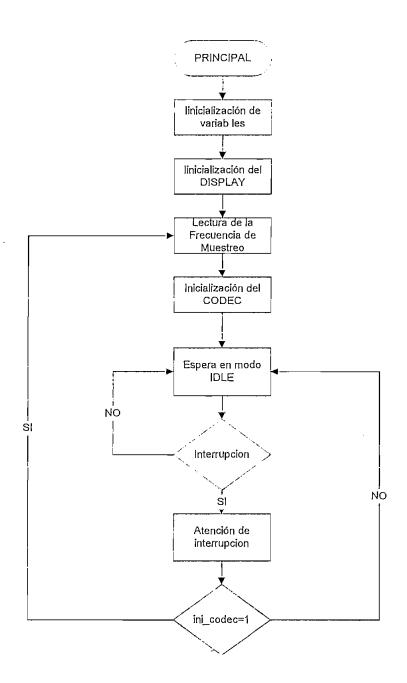

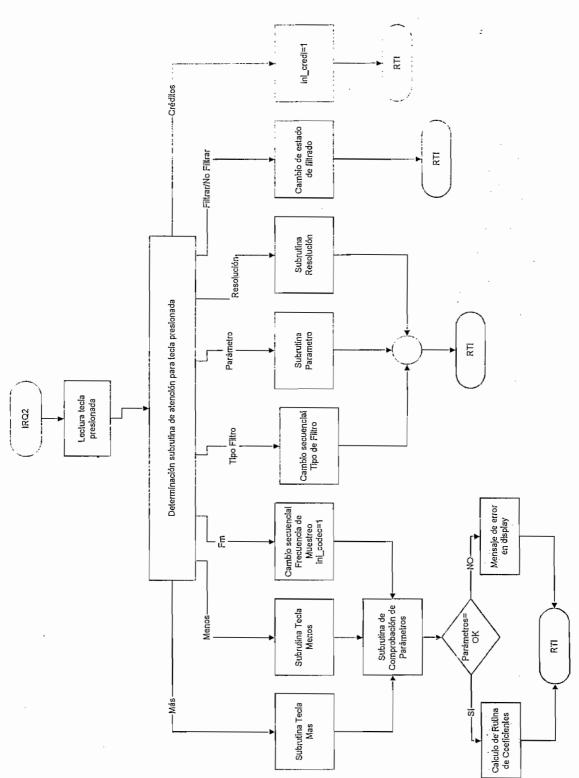

| Figura 3.25.   | Diagramas de flujo                                                           |

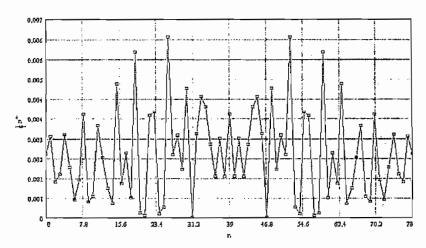

| Figura 4.1.    | Error porcentual de los coeficientes cuantificados y sin cuantificar para el |

|                | ejemplo (Filtro pasa bajo) caso no crítico                                   |

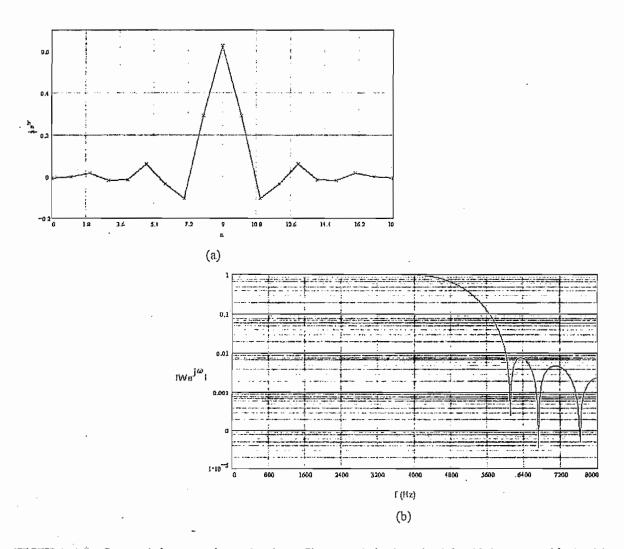

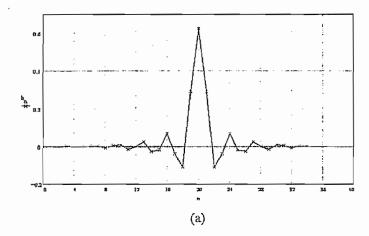

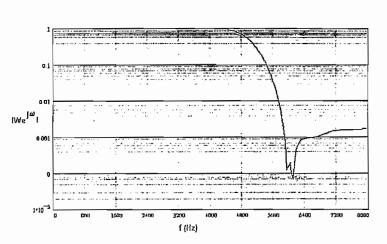

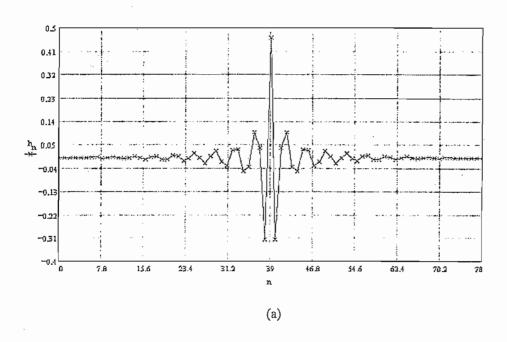

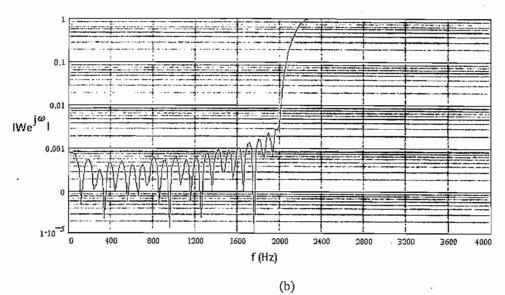

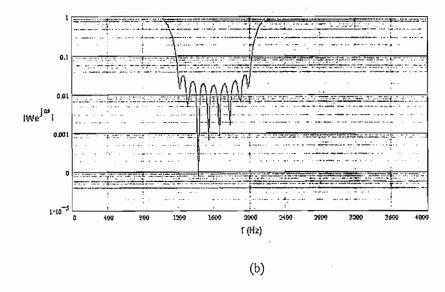

| Figura 4.2.    | Características teóricas de un filtro pasa bajo de orden M = 19              |

|                | (caso no crítico)                                                            |

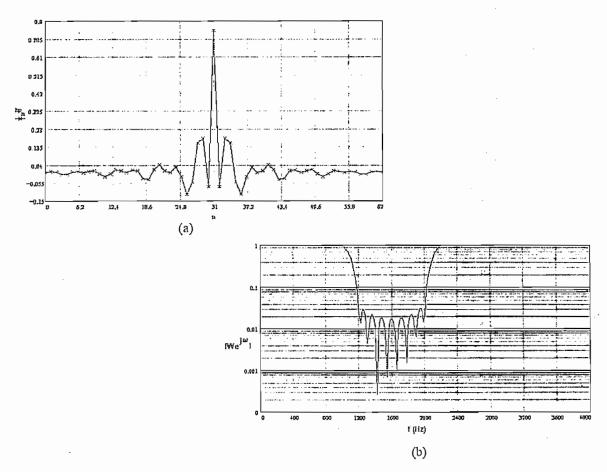

| Figura 4.3.    | Características experimentales de un filtro pasa bajo de orden M = 19        |

|                | (caso no crítico)                                                            |

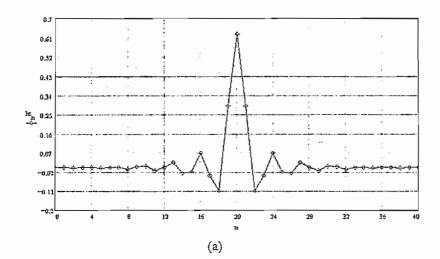

| Figura 4.4.  | Características teóricas de un filtro pasa bajo de orden M = 41                 |

|--------------|---------------------------------------------------------------------------------|

|              | y atenuación de 80 dB (caso crítico).                                           |

| Figura 4.5.  | Características experimentales de un filtro pasa bajo de orden                  |

|              | M = 41 y atenuación 80dB (caso crítico)                                         |

| Figura 4.6.  | Error porcentual de los coeficientes cuantificados y sin cuantificar para el    |

|              | ejemplo (Filtro pasa alto)141                                                   |

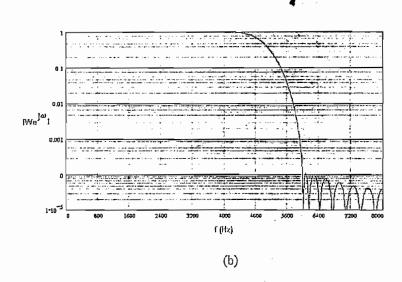

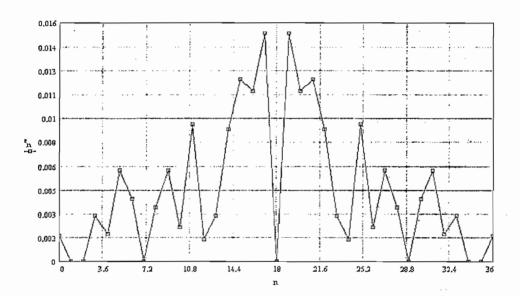

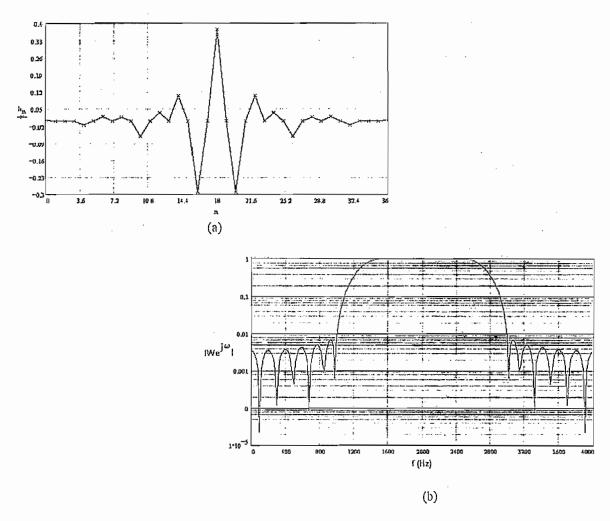

| Figura 4.7.  | Características teóricas de un filtro pasa alto de orden $M = 79$ 142           |

| Figura 4.8.  | Características experimentales de un filtro pasa alto de orden $M = 79.143$     |

| Figura 4.9.  | Error porcentual de los coeficientes cuantificados y sin cuantificar para el    |

|              | ejemplo (Filtro pasa banda)                                                     |

| Figura 4,10. | Características teóricas de un filtro pasa banda de orden $M = 37$ 147          |

| Figura 4.11. | Características experimentales de un filtro pasa banda de                       |

|              | orden M = 37                                                                    |

| Figura 4.12. | Error porcentual de los coeficientes cuantificados y sin cuantificar para el    |

|              | ejemplo (Filtro rechaza banda)                                                  |

| Figura 4.13. | Características teóricas de un filtro rechaza banda de orden $M = 63 \dots 148$ |

| Figura 4.14. | Características experimentales de un filtro rechaza banda de                    |

| •            | orden $M = 63$                                                                  |

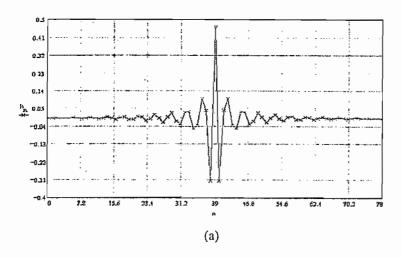

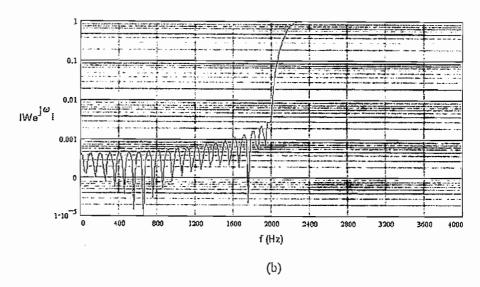

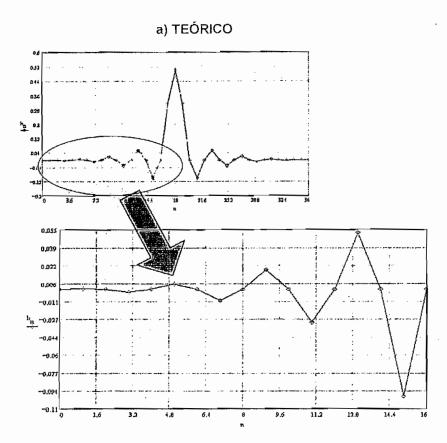

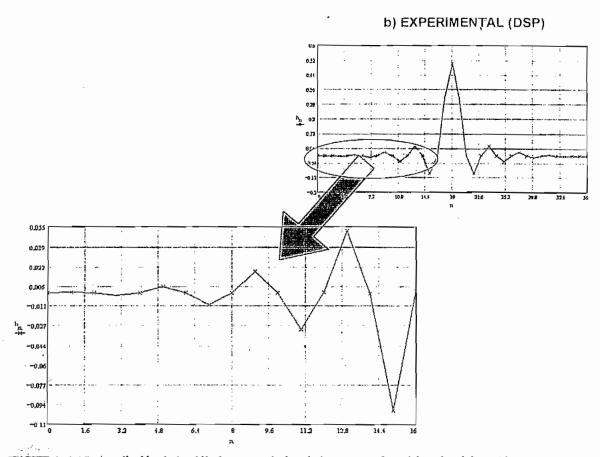

| Figura 4.15. | Ampliación de los lóbulos secundarios de la repuesta impulsiva                  |

|              | a) teórica y b) experimental                                                    |

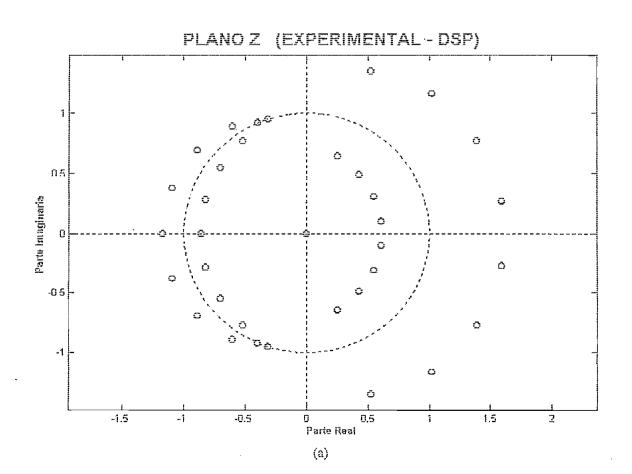

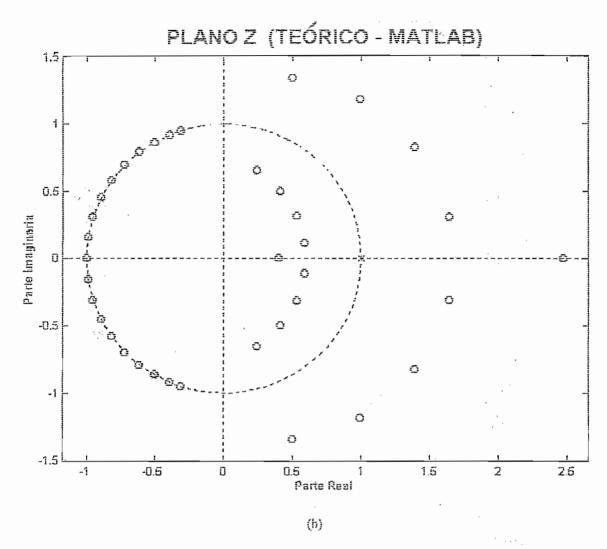

| Figura 4.16. | Efecto de cuantificación de la respuesta al impulso en los                      |

|              | ceros de H(z)                                                                   |

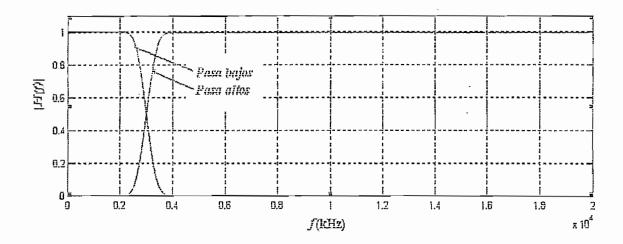

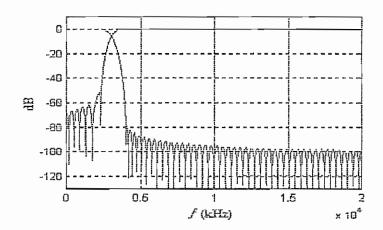

| Figura 4.17. | Magnitud de las respuestas de baja y alta frecuencia en filtros                 |

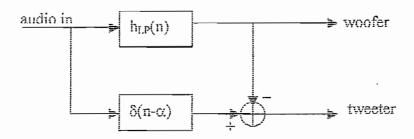

|              | Crossover de dos vías                                                           |

| Figura 4.18. | Implementación complementaria de filtros crossover de dos vías 157              |

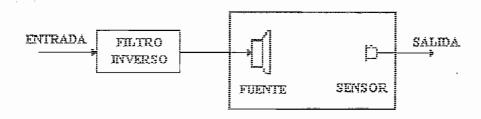

| Figura 4.19  | Sistema acústico consistente de un altoparlante y un micrófono 158              |

# LISTA DE TABLAS

| Tabla 1.1.  | Unidades funcionales de la Arquitectura ADSP-21xx                    |

|-------------|----------------------------------------------------------------------|

| Tabla 2.1.  | Comparación de las ventanas comúnmente utilizadas                    |

| Tabla 3.1.  | Formulas para el diseño de filtros digitales                         |

| Tabla 3.2.  | Fórmulas comunes para los filtros básicos para el diseño             |

| Tabla 3.3.  | Repuesta de frecuencia (coeficientes del filtro)                     |

| Tabla 3.4.  | Operaciones que realiza cada unidad computacional de la ADSP-2181 88 |

| Tabla 3.5.  | Descripción de las funciones de las banderas de la ALU101            |

| Tabla 3.6.  | Fuentes de los registros de entrada y salida de la ALU               |

| Tabla 3.7.  | Entradas y Salidas del Multiplicador - Acumulador                    |

| Tabla 3.8.  | Salida del arreglo del desplazador como función del código de        |

|             | control C y la señal HI/LO110                                        |

| Tabla 3.9.  | Fuentes de entrada y salida de la sección de desplazamiento          |

| Tabla 3.10. | Registros I, M y L de los DAGs                                       |

| Tabla 3,11. | Configuración de JP1 y tamaño de las EPROMs                          |

| Tabla 3.12. | Nombre de los pines de expansión                                     |

# CAPÍTULO 1

## **CONCEPTOS GENERALES**

La complejidad y la capacidad de los *chips* de tratamiento digital de señales han crecido exponencialmente desde principios de los 80's y no muestra signos de detenerse. A medida que las técnicas de integración se vayan desarrollando progresivamente, se implementarán sistemas de procesamiento de señales con bajo costo, tamaño miniaturizado y bajo consumo de potencia.

En consecuencia, la importancia del procesamiento de señales en tiempo discreto continuará creciendo casi con toda certeza y a la vez promoviendo avances revolucionarios en algunas áreas de aplicación. Un área notable es las telecomunicaciones en el que las técnicas de procesamiento digital de señales, la tecnología, avances de los microprocesadores y la transmisión por fibra óptica se combinan para cambiar la naturaleza de los sistemas de comunicaciones. Cambios similares se pueden esperar en muchas otras áreas de la tecnología.

#### 1.1 FILTROS DIGITALES

Aunque el procesamiento de señales es un campo dinámico y rápidamente creciente, sus fundamentos están bien establecidos. Con un tratamiento coherente de la teoría de los sistemas lineales en tiempo discreto, *las técnicas de filtrado*, muestreo de señales y el análisis de Fourier en tiempo discreto; se puede tener el conocimiento necesario para apreciar el amplio rango de aplicaciones que se pueden ejecutar y las bases para contribuir a los futuros desarrollos en el campo de la tecnología.

En general, cualquier sistema que seleccione ciertas frecuencias de una señal con respecto a otras se denomina *filtro*. La función de un filtro es la de quitar las partes no deseadas de una señal (como por ejemplo el ruido), o extraer las partes

deseadas de la señal tales como ciertas componentes dentro de un rango de frecuencias.

En la figura 1.1 se ilustra la idea básica de un filtro.

Figura 1.1 Idea general de un filtro [15]

Hay dos clases principales de filtros: *analógicos y digitales.* Éstos son muy diferentes en cuanto a su aspecto físico y a la forma cómo trabajan.

Los filtros analógicos utilizan circuitos electrónicos analógicos formados por componentes, como: resistencias, condensadores y amplificadores operacionales necesarios para producir los requerimientos de filtrado. Éstos tipos de filtros se utilizan en aplicaciones como: reducción del ruido, perfeccionamiento de señales de video, ecualizadores gráficos en sistemas de alta fidelidad, y en muchas otras áreas.

Un filtro digital utiliza un procesador digital para realizar cálculos numéricos con los valores de las muestras de la señal. El procesador podría ser un computador de propósito general como por ejemplo un PC, o un procesador especializado como un DSP (Digital Signal Processor, Procesador Digital de Señales).

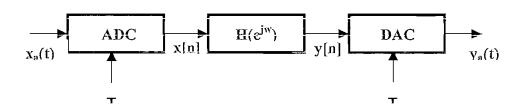

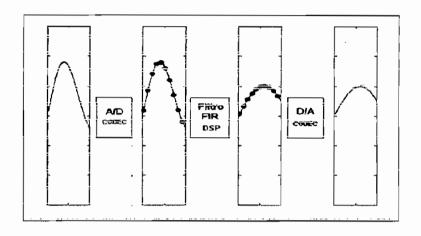

La señal de entrada analógica debe primero ser muestreada y luego digitalizada usando un ADC (Analog to Digital Converter, Conversor Analógico-Digital), obteniendo como resultado números binarios, los cuales representan los valores de las muestras sucesivas que corresponden a la señal de entrada, éstos valores son transferidos hacia el procesador, el cual realiza los cálculos numéricos.

Éstos cálculos típicamente involucran multiplicaciones de los valores de entrada por constantes y las sumas entre dichos productos. Al final los valores obtenidos del procesador son convertidos nuevamente en señal de forma analógica usando un DAC (Digital to Analog Converter, Conversor Digital-Analógico).

En un filtro digital, las señales están representadas por una secuencia de números, en lugar de valores de voltaje o corriente. En la figura 1.2 se indica el arreglo básico de dicho sistema.

Figura 1.2 Proceso de filtrado de una señal analógica [15]

Los filtros digitales son una parte muy importante de los DSP. De hecho, su extraordinario desempeño es una de las razones más importantes por las cuales los DSP han llegado a ser tan populares.

### 1.1.1 FILTROS DIGITALES vs. FILTROS ANALÓGICOS

Los filtros digitales son utilizados para dos propósitos generales:

- 1. La separación de señales que han sido combinadas.

- 2. La restauración de señales que han sido distorsionadas de alguna manera.

Los filtros analógicos también llamados *electrónicos* pueden ser utilizados para éstos mismos propósitos, sin embargo, los filtros digitales pueden alcanzar resultados superiores.

La separación de la señal es utilizada cuando ésta ha sido contaminada con interferencia, ruido u otras señales. Por ejemplo el ECG (ElectroCardioGram, Electrocardiograma) es un aparato que sirve para medir la actividad eléctrica del corazón de un bebé mientras está en el útero de su madre, la señal obtenida probablemente podría ser influenciada por la respiración y los latidos del corazón de la madre. Mediante la utilización de un filtro se podría separar éstas señales para ser analizadas individualmente.

Se utiliza la restauración de una señal cuando se produce de alguna manera distorsión de la misma. Por ejemplo, en una grabación de sonido realizada con equipos ineficaces, mediante el filtrado se podría representar de mejor manera la señal. Éstos problemas podrían ser resueltos con filtros analógicos o digitales.

Los filtros analógicos son bajos en costo, rápidos, y tienen un  $rango\ dinámico^1$  grande en amplitud y frecuencia. Los filtros digitales, en comparación, son inmensamente superiores en cuanto a la rapidez en la transición que pueden alcanzar. Por ejemplo un filtro digital pasa bajo puede tener una ganancia DC constante de  $1\pm0.0002$  a una frecuencia de 1000 hertz, y una ganancia menor que 0.0002 para frecuencias superiores a 1001 hertz. La transición ocurre dentro de tan sólo 1 hertz.

Los filtros digitales pueden alcanzar mejores tiempos de ejecución que los filtros analógicos. Esto hace una diferencia dramática en cuanto al filtrado de señales, ya que con filtros analógicos el problema radica en las limitaciones en cuanto al manejo de los elementos electrónicos, tal como la exactitud y estabilidad de las resistencias y condensadores.

<sup>&</sup>lt;sup>1</sup> Un elemento puede producir un rango constante en Amplitud entre valores máximos y mínimos, al que se le denomina Rango Dinámico, este valor es medido en Decibelios

En comparación, los filtros digitales son tan eficientes que frecuentemente se ignora el rendimiento de los mismos.

#### 1.1.2 VENTAJAS DE LOS FILTROS DIGITALES

Los filtros digitales tienen las siguientes ventajas frente a los filtros analógicos:

- Los filtros digitales son fáciles de diseñar, probar e implementar en computadoras de propósito general o en estaciones de trabajo.

- Son programables por software, ésta operación es determinada por un programa almacenado en la memoria del procesador. Esto significa que los filtros digitales pueden ser cambiados fácilmente sin afectar el hardware. Los filtros analógicos pueden ser cambiados únicamente rediseñando la circuitería del filtro.

- No son afectados por cambios en la temperatura o humedad, los filtros digitales son extremadamente estables con respecto a éstos factores, en cambio los filtros analógicos contienen elementos activos que son dependientes de la temperatura.

- Son manejables con señales de baja frecuencia, ya que los filtros digitales son implementados mediante tecnologías DSP, es decir por software, no existe inconveniente en trabajar con señales de baja frecuencia. Esto no ocurre con los filtros analógicos en los cuales se produce inestabilidad.

- Pueden manejar combinaciones complejas, gracias a la velocidad de los procesadores DSP se puede implementar por software filtros en paralelo o cascada afectando en forma mínima el tiempo de respuesta.

- Alta precisión, limitada por los errores de redondeo y truncamiento, en la aritmética empleada en el DSP.

- Intervalo dinámico. En filtros analógicos aparecen elementos electrónicos que limitan el rango dinámico, (por lo general la limitación es en el límite inferior), produciendo saturación con la alimentación. En cambio en los filtros digitales es fijado por el número de bits que representa la secuencia y los errores de redondeo.

- Respuesta dinámica. El ancho de banda del filtro digital está limitado por la frecuencia de muestreo<sup>1</sup>, mientras que en los filtros analógicos con componentes activos suelen estar restringidos por los amplificadores operacionales.

- Son versátiles, los filtros digitales tienen la habilidad de procesar señales de varias maneras, esto incluye la capacidad de adaptarse a los cambios en las características de la señal.

- Son inmunes al ruido, en filtros analógicos la utilización de dispositivos electrónicos incrementan la posibilidad de tener la presencia de anomalías dentro del sistema, así como es el ruido.

- Muy bajo costo, en un filtro analógico para poder obtener los resultados deseados se debe cambiar los dispositivos electrónicos que lo conforman, incrementando su costo.

### 1.1.3 DESVENTAJAS DE LOS FILTROS DIGITALES

Las desventajas que pueden afectar a los filtros digitales se originan básicamente de inconvenientes de aproximación que se obtengan en cada uno de los diferentes métodos matemáticos de diseño; dependiendo de cada tipo de

El intervalo de tiempo T entre dos muestras sucesivas se denomina período de muestreo o intervalo de muestreo y su recíproco 1/T = fin se llama velocidad de muestreo o frecuencia de muestreo.

filtro y de las características deseadas, un determinado método se adaptará de mejor manera que otro.

Las desventajas que se generen dependerán de la elección e implementación adecuada de éstos métodos, es decir, las desventajas que acarree un determinado método no necesariamente lo ocasionará otro.

- Por ejemplo para determinados filtros no es posible aprovechar las ventajas de la Transformada Rápida de Fourier en la implementación, ya que para esto es necesario un número de puntos finitos.

- Otros filtros alcanzan una magnifica respuesta en amplitud a expensas de un comportamiento no lineal en fase.

### 1.2 MICROPROCESADORES DSP

Uno de los motivos principales de la aceptación de los *chips* DSP en la actualidad, es la gran variedad de herramientas de desarrollo proporcionados por los principales fabricantes de éstos. (*Texas Instruments, Analog Devices, Motorola, etc.*)

### 1.2.1 PROCESAMIENTO DIGITAL DE SEÑALES

El Procesamiento Digital de Señales es una de las áreas más poderosas que puede disponer la ciencia e ingeniería actualmente. Existe un amplio conjunto de aplicaciones en donde son de mucha importancia el hardware y el software del procesamiento de señales, aplicaciones que van desde sistemas militares altamente especializados hasta llegar a la simple electrónica de bajo costo. El procesamiento de señales se ha beneficiado siempre de una relación estrecha entre la teoría, las aplicaciones y el desarrollo de las tecnologías.

El creciente número de aplicaciones y la demanda de algoritmos de sofisticación van de la mano con el avance de la tecnología de dispositivos para el procesamiento de señales. Se estima que la capacidad de proceso de los microprocesadores DSP para tratamiento de señales se incrementará en un factor de 200 o más en los próximos diez años [14].

Antes de los años 60, la tecnología para el procesamiento de señales era casi exclusiva de los elementos analógicos. Pero la rápida evolución de los computadores y los microprocesadores digitales junto con algunos importantes desarrollos teóricos como el algoritmo de la FFT¹ (Fast Fourier Transform, Transformada Rápida de Fourier) fueron la causa de un importante desplazamiento hacia las tecnologías digitales, naciendo así el campo del procesamiento digital de señales. Un aspecto importante del procesamiento digital de señales es que se basa en el procesamiento de secuencias de muestras.

## 1.2.2 PROCESADOR DIGITAL DE SEÑAL (DSP)

Actualmente los DSP se están convirtiendo en elementos muy comunes en el diseño electrónico, sustituyendo en algunas aplicaciones a los microprocesadores y microcontroladores.

Principalmente se encuentran DSP en circuitos relacionados con las telecomunicaciones, sistemas de audio y en algoritmos avanzados de control de motores. Por ejemplo, se puede encontrar DSP como integrantes de las siguientes aplicaciones:

Tarjetas con múltiples puertos seriales en servidores para proveedores de acceso a Internet.

La transformada rápida de Fourier es simplemente un algoritmo rápido para la evaluación numérica de integrales de Fourier desarrollado en los laboratorios de IBM, y su importancia radica en la rapidez de cálculo conseguida en muchos tipos de aplicaciones como: ecualización y filtrado en equipos de audio / video en tiempo real, comunicaciones, etc.

- Generadores de eco.

- · Compresión de voz en telefonía móvil.

- Decodificación de canales en telefonía celular GSM<sup>1</sup> (Global System for Mobile communication, Sistema Global para la comunicación Móvil).

- Filtros complejos de sonido.

Los DSP son sistemas programables que permiten impiementar muchos tipos de aplicaciones en función de las posibilidades del sistema y, por supuesto, de las habilidades del programador.

Desde el punto de vista de la arquitectura interna, se puede decir que un DSP es un microprocesador optimizado internamente para realizar los cálculos necesarios para implementar algoritmos de procesamiento de señal. Ésta optimización se consigue mediante algunos aspectos principales:

- Implementación de operaciones por software.

- Instrucciones poco comunes que ejecutan varias operaciones en un solo ciclo.

- Modos de direccionamiento especiales.

- Memoria de programa "ancha", con más de 8 bits.

La implementación de algunas operaciones mediante software consigue mejorar la velocidad media de cálculo, que se da en MIPS (Millones de Instrucciones Por Segundo); normalmente, las instrucciones que se implementan son aquellas que se usan más a menudo.

<sup>&</sup>lt;sup>1</sup> Sistema Global para la comunicación Móvil (GSM). El desarrollo del GSM comenzó en 1982 cuando se formó un grupo de estudio llamado inicialmente *Group Special Mobile*. El grupo tenía que estudiar y desarrollar un sistema celular público de *Pan-European* en el rango de 900 MHz.

Aunque es posible usar diferentes tipos de microprocesadores rápidos de propósito general para procesamiento de señales, éstos no son muy utilizados ya que el diseño resulta complicado de implementarlo y muy costoso de fabricar. En contraste los DSP tienen una arquitectura que simplifica el diseño y reduce el costo de las aplicaciones.

La impresionante capacidad de cálculo de un DSP puede utilizarse también para implementar algoritmos digitales de control (por ejemplo, un controlador PID¹ (*Proporcional Integral Derivativo*)) y, si el costo lo permite, otras labores realizadas tradicionalmente por microprocesadores.

Las clases de algoritmos utilizados en el procesamiento de señales pueden ser mejoradas al apoyarse en una arquitectura de computador. Para realizar el procesamiento digital de señales de una manera eficaz, el microprocesador debe tener las características siguientes:

- Unidades computacionales rápidas y flexibles.

- Permitir el flujo de datos hacia y desde las unidades computacionales.

- Precisión extendida y rango dinámico en las unidades computacionales.

- Generadores de dirección duales.

- Eficiente secuenciamiento de programas y mecanismos de lazo.

<sup>&</sup>lt;sup>1</sup> Es una de las formas más comúnmente utilizadas en sistemas industriales en la que combina las acciones de control y permite mejorar la calidad de la respuesta tanto transitoria como en estado estable.

### 1.2.2.1 Arquitectura típica de un DSP

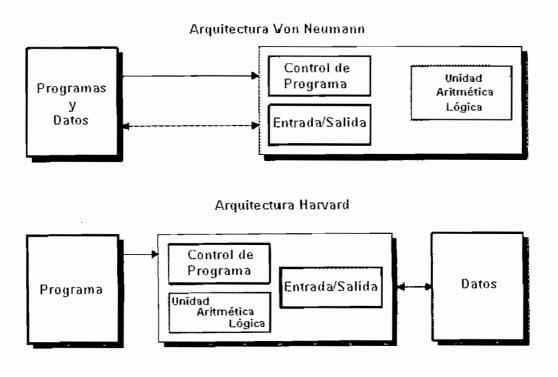

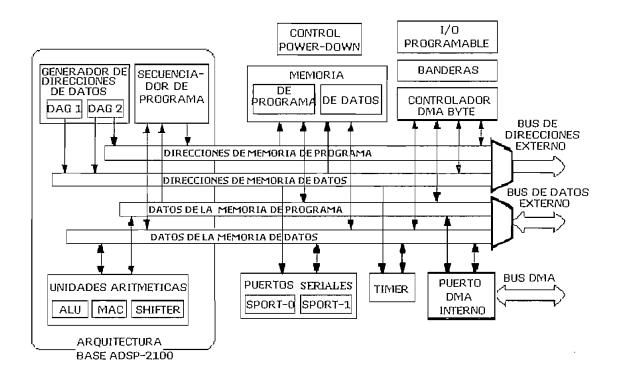

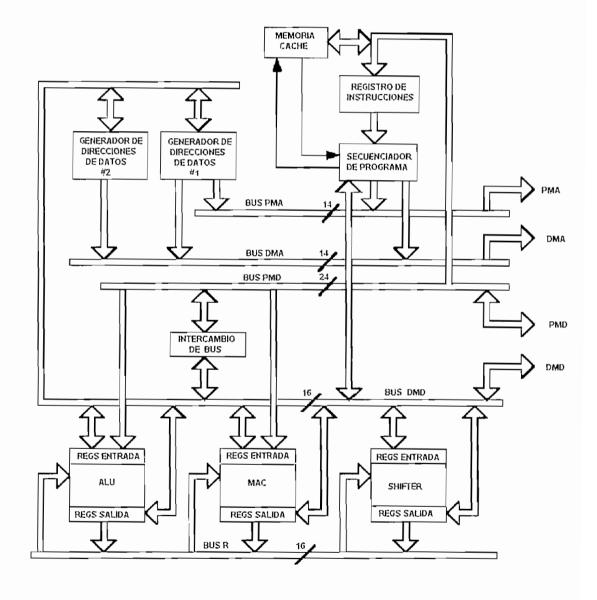

Los DSP abandonan la arquitectura clásica de *Von Neumann*, en la que datos y programas están en la misma zona de memoria, y apuestan por la denominada "Arquitectura *Hardvard*" como se observa en la figura 1.3.

En una arquitectura *Hardvard* existen bloques de memoria físicamente separados para datos y programas. Cada uno de éstos bloques de memoria se direcciona mediante buses separados (tanto de direcciones como de datos), e incluso es posible que la memoria de datos tenga distinta longitud de palabra que la memoria de programa (como ocurre en ciertos microcontroladores).

Figura 1.3 Arquitectura básica de los DSP. [15]

Con este diseño se consigue acelerar la ejecución de las instrucciones, ya que el sistema puede ejecutar simultáneamente la lectura de datos de la instrucción "n" y comenzar a decodificar la instrucción "n+1", disminuyendo el tiempo total de ejecución de cada instrucción.

Normalmente en los DSP se usa una arquitectura *Hardvard* modificada con 3 buses: uno de programa y dos de datos, lo cual permite que la Unidad Central de Procesos lea una instrucción y dos operandos a la vez ( pero no dos posiciones de memoria a la vez, para lo que hace falta una RAM (*Random Access Memory*, Memoria de Acceso Aleatorio) de doble puerto). En el proceso de señales, las operaciones con 2 operandos son muy comunes, motivo por el cual se hace ésta modificación.

También es bastante común encontrar un solapamiento entre la ROM (*Read Only Memory*, Memoria Solo de Lectura) y la RAM de datos, de modo que se puede usar parte de la ROM de programa para almacenar coeficientes y leerlos en la RAM de datos, sin tener que usar instrucciones específicas para leer los datos almacenados en ROM, como ocurre en algunos microcontroladores.

#### 1.2.2.2 Áreas de desarrollo del DSP

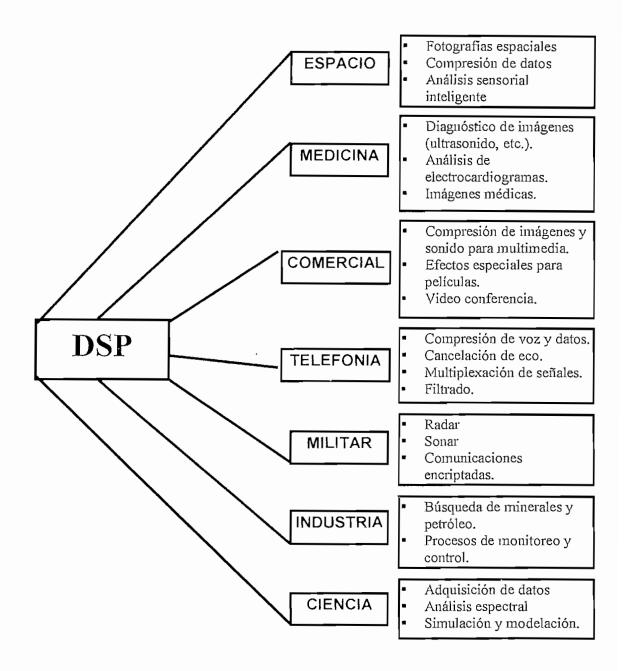

La figura 1.4 ilustra algunas áreas de aplicación de los DSP los cuales han sufrido un continuo desarrollo, tales como: las comunicaciones, imágenes médicas, radar y sonar, reproducción de música de alta fidelidad, etc. Cada una de éstas áreas han originado una tecnología DSP con sus propios algoritmos, matemáticas y técnicas especializadas.

El Procesamiento Digital de Señales se distingue de otras áreas por el tipo de datos que utiliza: señales. En la mayoría de casos, éstas señales son originadas como datos censados del mundo real tales como: vibraciones sísmicas, imágenes visuales, ondas de sonido, etc.

En general el DSP son las matemáticas, los algoritmos, y las técnicas usadas para manipular éstas señales después de que han sido convertidas en un formato digital. Esto incluye una gran variedad de metas, tales como: perfeccionamiento de imágenes visuales, reconocimiento y generación de lenguaje, compresión de datos para almacenamiento y transmisión, etc.

Figura 1.4 Áreas de desarrollo de los DSP [14]

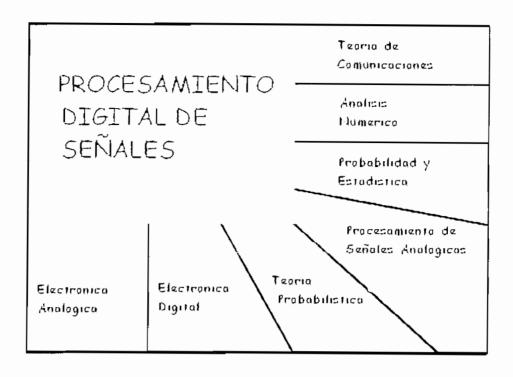

En la figura 1.5 se puede observar la interrelación que existe entre el Procesamiento Digital de Señales y otras disciplinas técnicas que se encuentran bien definidas, pero juntas han permitido desarrollarse con mayor rapidez.

Figura 1.5 Áreas afines al Procesamiento Digital de Señales. [14]

## 1.2.2.3 Familia de Microprocesadores ADSP-2100 [1]

La familia ADSP-2100 es una colección de microprocesadores programables de un solo *chip*, que tienen en común una arquitectura base ADSP-21XX optimizada para el procesamiento digital de señales y otras aplicaciones de procesamiento numérico de alta velocidad.

Las familias de procesadores difieren principalmente en el tipo de periféricos que se aumentan en la arquitectura base. Tales como memoria, temporizador, puerto(s) serial(es), y puertos paralelos que están disponibles en los diferentes miembros de la familia. Además, los procesadores ADSP-21msp58/59 incluyen un interfaz analógico para conversión de señales en la banda de voz.

La tabla 1.1 indica las principales unidades funcionales de la arquitectura ADSP-21xx, y muestra las funciones que se incluyen en cada uno de los procesadores.

| CARACTERÍSTICAS          | 2101     | 2103 | 2105     | 2115 | 2111     | 2171     | 2173 | 2181 | 2183 | 21msp58 |

|--------------------------|----------|------|----------|------|----------|----------|------|------|------|---------|

| Unidad Aritmética Lógica | *        | *    | *        | *    | ÷        | *        | *    | *    | *    | *       |

| Acumulador Multiplicador | *        | *    | ÷        | *    | *        | <b>÷</b> | *    | ÷    | *    |         |

| Shifter                  |          | *    | *        | ÷    | <b>.</b> | *        | *    | *    | *    | *       |

| Generadores de           |          |      |          |      |          |          |      |      |      |         |

| Direcciones de Datos     |          | *    | *        | *    | *        | ÷        | ÷    | ÷    | *    | *       |

| Secuenciador de          |          |      |          |      |          |          |      |      |      |         |

| Programas                |          | *    | *        | ÷    | *        | *        |      | ÷    | ÷    | ÷       |

| Memoria de Datos RAM     | ΙK       | 1K   | 512      | 512  | 1K       | 2K       | 2K   | 16K  | 16K  | 2K      |

| Memoria de Programa      |          |      |          |      |          |          |      |      |      |         |

| RAM                      | 2K       | 2.K  | ΙK       | 1K   | 2K       | 2K       | 2K   | 16K  | 16K  | 2K      |

| Temporizador             | *        | *    | *        | ÷    | 4        | <b>÷</b> | *    | *    | *    | *       |

| Puerto Serial 0          | *        | ÷    |          | ÷    | * .      | ÷        | *    | *    | ÷    | *       |

| Puerto Serial 1          | <b>÷</b> | *    | <b>*</b> | ÷    | *        | ÷        | ÷    | ÷    | ÷    | ÷       |

| Interfaz Puerto Host     |          |      |          |      | *        | *        | ÷    |      |      | *       |

| Puerto DMA               |          |      |          |      |          |          |      | *    | ÷    |         |

| Interfaz Analógico       |          |      |          |      |          |          |      |      |      | ÷       |

| Fuente de Voltaje        | 7V       | 3.3V | 5V       | 5γ   | 5V       | 5V       | 3.3V | 5V   | 3.3V | 5V      |

| Velocidad instrucciones  |          |      |          |      |          |          |      |      |      |         |

| MIPS                     | 20       | 10   | 13.8     | 20   | 20       | 33       | 20   | 33   | 33   | 26      |

TABLA 1.1 Unidades Funcionales de la Arquitectura ADSP - 21XX [1]

- Unidades Computacionales. Todos los procesadores de la familia ADSP-2100 contienen tres unidades computacionales independientes:

- Una ALU (Arihtmetic / Logic Unit, Unidad Aritmética Lógica).

- ·Un MAC (Multiplier / Accumulator, Multiplicador Acumulador) y;

- Un Shifter o Unidad de Desplazamiento.

Las unidades computacionales procesan datos de 16-bit directamente y también proveen soporte de *hardware* para cálculos de multiprecisión.

• Generadores de Dirección de Datos & Secuenciador de Programa. Los dos generadores de dirección de datos permiten al procesador establecer

direcciones simultáneas para producir operandos dobles. El secuenciador y los generadores de dirección de datos mantienen las unidades computacionales en continuo funcionamiento, maximizando de ésta manera el *throughput*<sup>1</sup>.

- Memoria. La familia ADSP-2100 utiliza la arquitectura modificada de Harvard en la que la memoria de datos almacena datos, y la memoria de programa almacena datos y programas. Toda la familia de procesadores ADSP-2100 contienen una RAM que comprende una parte del espacio para la memoria de programas y otra parte para la memoria de datos. La velocidad de la memoria permite al procesador extraer dos operandos (uno de memoria de datos y otro de memoria de programa) y una instrucción (de memoria de programa) en un solo ciclo de máquina.

- Interfaz analógico Los procesadores ADSP-21msp58/59 incluyen una circuitería para procesamientos analógicos y digitales de señales. Ésta circuitería incluye un conversor analógico digital, un conversor digital analógico, filtros analógicos y digitales, y un interfaz paralelo al centro del procesador. La arquitectura ADSP-21XX exhibe un alto grado de paralelismo, hechos a la medida de los requerimientos de los DSP. En un solo ciclo de máquina el ADSP -21XX puede:

- Generar la siguiente dirección de programa.

- Sacar la siguiente instrucción.

- Actualizar uno o dos punteros de dirección de datos.

- Ejecutar un operación.

En ese mismo ciclo los procesadores que tienen las unidades funcionales pertinentes también pueden:

<sup>&</sup>lt;sup>1</sup> Se conoce como throughput a la velocidad de procesamiento de datos.

- a. Recibir y / o transmitir datos vía puerto(s) serial(es).

- b. Recibir y / o transmitir datos vía el interfaz puerto Host.

- c. Recibir y / o transmitir datos vía los puertos DMA. (*Direct Memory Access*, Acceso Directo a Memoria)

- d. Recibir y / o transmitir datos vía el interfaz analógico.

- Temporizador Tiene un temporizador contador programable con 8-bit el cual provee una generación de interrupciones periódicas.

- Puertos Seriales Los puertos seriales (S\_PORTs) proveen un interfaz serial

completo con el hardware para la compresión y expansión de datos. Cada

S\_PORTs podría generar un reloj interno programable o aceptar un reloj

externo. El SPORTo incluye una opción de multicanal.

- Interfaz Host Puerto El Interfaz Host Puerto (HIP) permite la conexión directa a un procesador Host.

- Puertos DMA ( Direct Memory Access, Acceso Directo a Memoria). Los puertos DMA internos (IDMA) y los puertos DMA de Byte (BDMA) en los ADSP-2181 proveen eficientes transferencias de datos hacia y desde la memoria interna.

# 1.3 MÓDULO DE DESARROLLO PARA EL ADSP 2181 [1]

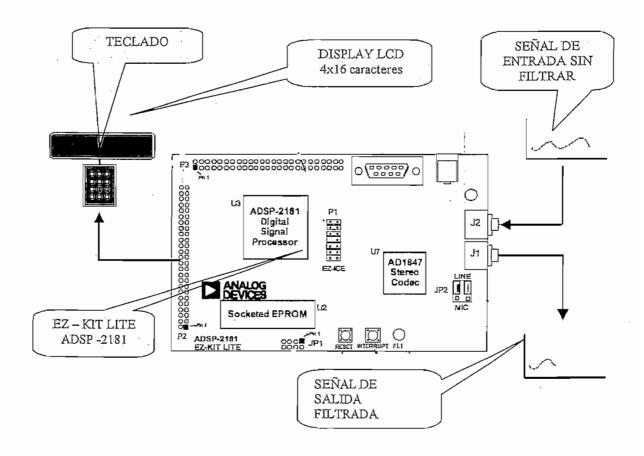

El ADSP-2181 de *Analog Devices* está sustentado por un módulo de desarrollo de bajo costo denominado *EZ-KIT Lite*. Este módulo incluye una tarjeta de evaluación (EZ-Lab) y un paquete de desarrollo de *software*.

## DESCRIPCIÓN GENERAL

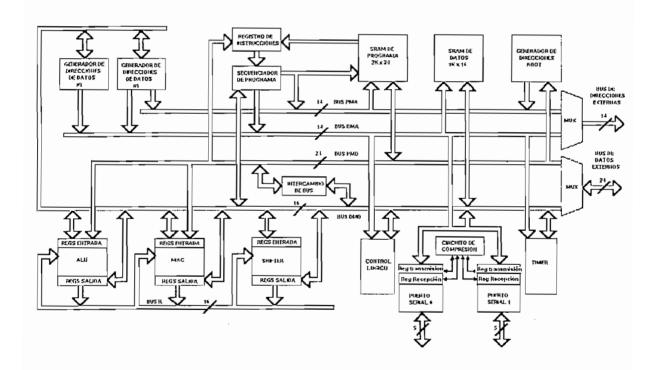

El ADSP-2181 es un microprocesador creado especialmente para Procesamiento Digital de Señales y otras aplicaciones que necesiten de procesamiento numérico de alta velocidad. Fabricado con tecnología CMOS, el ADSP-2181 opera con una sola fuente de alimentación de + 5 VDC; ejecuta 33 MIPS, en el que todas las instrucciones requieren un solo ciclo de procesador.

Figura 1.6 Diagrama de Bloques del ADSP-2181 [1]

El ADSP-2181 combina la arquitectura base de la familia ADSP-2100 (tres unidades computacionales, generadores de dirección de datos y secuenciador de programas) con dos puertos seriales, un puerto DMA interno de 16 bits, un puerto de byte DMA, un temporizador programable, banderas I/O, interrupciones y memoria de datos y de programas; como se ilustra en la figura 1.6

El EZ-KIT Lite es el módulo de desarrollo para el ADSP-2181, consta de un equipo de *hardware* y de *software* que ofrece un desarrollo completo para la familia ADSP-21XX. El EZ-KIT Lite incluye las siguientes características:

- Un ADSP-2181 de 33 MIPS

- Puerto de sonido estéreo AD 1847 (CODEC)

- Interfaz RS-232 para conexión con el PC.

- Software de Control para Windows 3.1

- · Teclas de usuario

- EPROM de 256 Kbytes

- · Conectores de expansión

- Jumpers configurables por el usuario

- Programas Demos DSP

Esta tarjeta puede trabajar sola o conectarse al pórtico RS-232 de un computador, para que un programa monitor que se ejecuta en el ADSP-2181, conjuntamente con un programa *Host* en el PC interactúen para almacenar programas de usuario y examinar los contenidos de la memoria interna del procesador.

En la memoria EPROM se graba el programa monitor, ésta memoria se encuentra alojada en un zócalo, la cual puede ser removida para insertar una nueva memoria que contenga códigos de programa desarrollados por el usuario.

El paquete de desarrollo de software proporciona el soporte necesario para el desarrollo de aplicaciones DSP. A más del programa Host y el programa monitor se incluyen utilitarios que son:

- Un Assembler, reúne los códigos fuente y los módulos de datos de la mejor manera como soporte la sintaxis de alto nivel del set de instrucciones.

- Un Linker, enlaza separadamente módulos ensamblados.

- Un PROM Splitter, este módulo lee el linker de salida y genera archivos compatibles con el programador PROM.

- Un Simulador, ejecuta un interactivo, simulador del nivel de instrucciones de la configuración de hardware descrita por el Sistema Constructor.

# CAPÍTULO 2

# DISEÑO DE FILTROS FIR

El diseño de filtros digitales es una de las áreas más importantes en el diseño electrónico. Aunque los libros de diseño de filtros analógicos lo muestran como un proceso simple, el diseño de filtros requiere de un conocimiento avanzado de matemáticas y una comprensión entera del proceso que va a ser afectado por el filtro.

Las herramientas de procesamiento digital de señales han hecho posible el reemplazo de filtros analógicos por filtros digitales en aplicaciones que requieren flexibilidad. Éstas aplicaciones incluyen audio, telecomunicaciones, control numérico de procesos, instrumentación, robótica, entre otras. Los filtros digitales son una parte muy importante de los DSP.

## 2.1. INTRODUCCIÓN

Los filtros son una clase de Sistemas LTI [5], [11] [12] (*Linear Time Invariant*, Lineales e Invariantes en el Tiempo), muy importantes. En general, cualquier sistema que modifique ciertas frecuencias con respecto a otras se denomina *filtro*.

El diseño de filtros requiere realizar las siguientes etapas:

- 1. Especificación de las propiedades deseadas,

- Aproximación de las especificaciones mediante un sistema en tiempo discreto, y

- 3. Realización del sistema.

La primera es altamente dependiente de la aplicación y la tercera de la tecnología utilizada para la realización. En términos prácticos, el filtro deseado se realiza utilizando cómputo digital y se emplea para filtrar una señal en tiempo continuo mediante muestreo periódico seguido por una conversión analógica digital. Por este motivo se suelen denominar filtros digitales a los filtros en tiempo discreto.

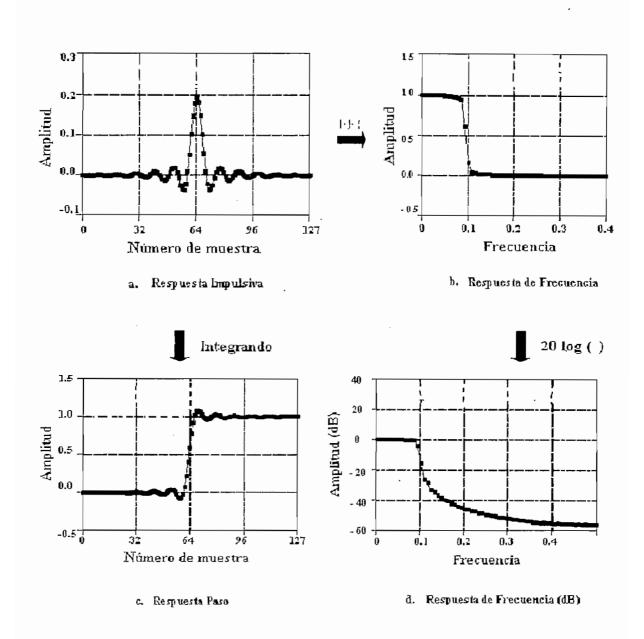

### 2.1.1 PARÁMETROS DE LOS FILTROS DIGITALES

Como se muestra en la figura 2.1, el filtro lineal tiene una *respuesta impulsiva*, una *respuesta de paso* y una *respuesta de frecuencia*. Cada una de éstas respuestas contienen información completa acerca del filtro, pero de una forma diferente. Si se especifica una de las tres formas de respuesta, la otras dos son fijadas y podrían ser calculadas directamente. Todas éstas representaciones son importantes, porque describen cómo el filtro puede reaccionar bajo diferentes circunstancias.

La salida de un sistema cuando la entrada es un impulso se denomina *respuesta impulsiva*. De la misma manera, *la respuesta paso* es la salida cuando la entrada es una función paso (también llamada borde, o una respuesta de borde). Así como la función paso es la integral de la función impulso, la respuesta paso es la integral de la respuesta impulsiva. Existe dos maneras de encontrar la respuesta paso:

- 1. Alimentando con una forma de onda paso al filtro

- 2. Integrando la respuesta impulsiva

La respuesta de frecuencia puede ser encontrada tomando la DFT <sup>1</sup> (*Discrete Fourier Transform*, Transformada Discreta de Fourier) de la respuesta impulsiva

DFT. La Transformada Discreta de Fourier es una secuencia, no una función de una variable continua y corresponde a muestras equiespaciadas en frecuencia de la Transformada de Fourier de la señal.

Figura 2.1. Parámetros de los filtros. [14]

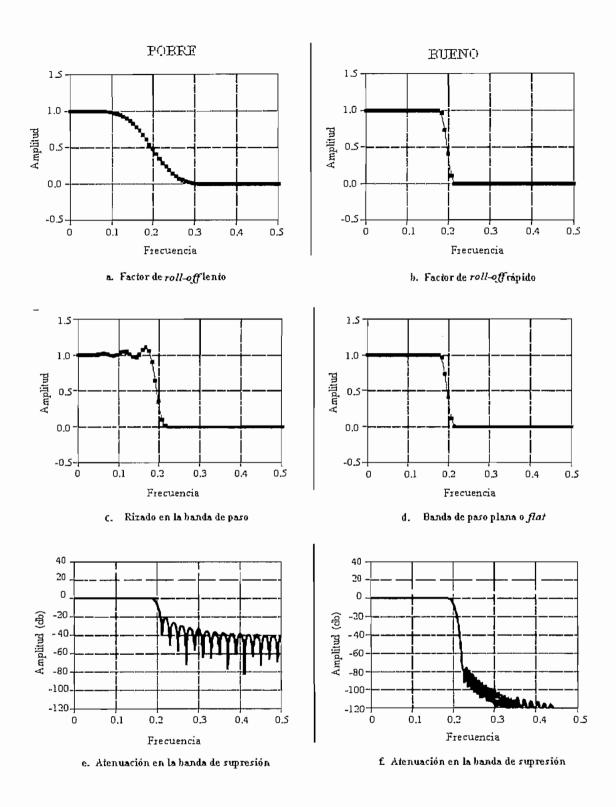

Se puede dibujar la respuesta de frecuencia (amplitud) en escala lineal o en escala logarítmica (decibelios), estas respuestas de frecuencia se pueden observar en la figura 2.1 (b) y (d) respectivamente. La escala lineal es mejor para indicar el rizado de la banda de paso y el factor de *roll-off* <sup>1</sup>, mientras que la escala en decibelios es mejor para indicar la atenuación de la banda de supresión

<sup>&</sup>lt;sup>1</sup> El factor de roll-off es una característica del filtro que indica como es la caída de la banda de transición. Permite evaluar el desempeño de un filtro digital en el dominio de la frecuencia.

(parámetros que serán detallados en la sección 2.2.1).

La palabra: dominio, es un término extensamente usado en Procesamiento de Señales. Por ejemplo una señal que use el tiempo como variable independiente, se dice estar en el dominio del tiempo. De la misma manera la señal que utilice la frecuencia como variable independiente, resulta estar en el dominio de la frecuencia. Igualmente, las señales que usen la distancia como parámetro independiente están en el dominio espacial (la distancia es una medida del espacio). El tipo de parámetro en el eje horizontal es el dominio de la señal.

Las señales de entrada y de salida de un filtro están en el dominio del tiempo. Esto es debido a que las señales son usualmente originadas al sacar una muestra o sampling¹ a intervalos iguales de tiempo. Ésta no es la única forma de sampling. Otra forma común es muestreando a intervalos iguales en espacio. Muchos otros dominios son posibles; sin embargo, el tiempo y el espacio son los más comunes.

Las maneras más comunes de contener la información en señales son:

- La información representada en el dominio del tiempo; y

- La información representada en el dominio de la frecuencia.

La información representada en el dominio del tiempo describe cuándo algo ocurre y cuál es la amplitud de ese suceso. Por ejemplo si se analizara la emisión de luz del sol, cada muestra de la señal indica que está sucediendo en ese instante, y el nivel del evento. Si una señal luminosa ocurre, la señal directamente provee la información en el tiempo de lo que ocurrió, su duración, el desarrollo sobre el tiempo, etc.

<sup>&</sup>lt;sup>1</sup> Teorema de Sampling o del Muestreo: Si una señal continua compuesta de frecuencias menores que f son muestreadas a frecuencias 2f o mayores, toda la información contenida en la señal continua se encontrará en la señal muestreada. Frecuentemente es llamado Teorema de Shannon o Teorema de Nyquist.

Cada muestra contiene información que es interpretada sin referencia de alguna otra muestra. Aun si se tiene una sola muestra de la señal, se puede saber algo acerca de esa medida.

La información representada en el dominio de la frecuencia es más indirecta. Por ejemplo un vaso del vino golpeado con la uña podría vibrar, produciendo un zumbido; el péndulo de un reloj de caja gira de un lado a otro; las estrellas y los planetas giran en su propio eje. Midiendo la frecuencia, fase, y amplitud de éstos movimientos periódicos, se podría tener información de sistemas que produzcan este tipo de movimiento. Si se toma una muestra de sonido que produjo el golpe a un vaso de vino. La frecuencia fundamental y los armónicos de la vibración periódica pueden indicar la masa y la elasticidad del material.

La respuesta paso describe cómo la información representada en el dominio del tiempo está siendo modificada por el sistema. En contraste, la respuesta de frecuencia muestra cómo la información representada en el dominio de la frecuencia está siendo cambiada. Éstas distinciones son completamente críticas en el diseño de filtros debido a que no es posible optimizar un filtro para ambas aplicaciones. Un buen rendimiento en el dominio del tiempo produce un pobre rendimiento en el dominio de la frecuencia, y viceversa. Al diseñar un filtro para eliminar el ruido de una señal ECG (información representada en el dominio del tiempo), la respuesta de paso es el parámetro importante, y la respuesta de frecuencia es de poco interés. Al diseñar un filtro digital para un audifono (con la información en el dominio de la frecuencia), la respuesta de frecuencia es muy importante, mientras que la respuesta de paso no importa.

## 2.1.1.1 Parámetros en el Dominio del Tiempo

Las respuestas paso, impulso y de frecuencia contienen idéntica información, sólo que en arreglos diferentes. La respuesta paso es útil en análisis en el dominio del tiempo porque iguala la forma de ver como la información está contenida en las señales.

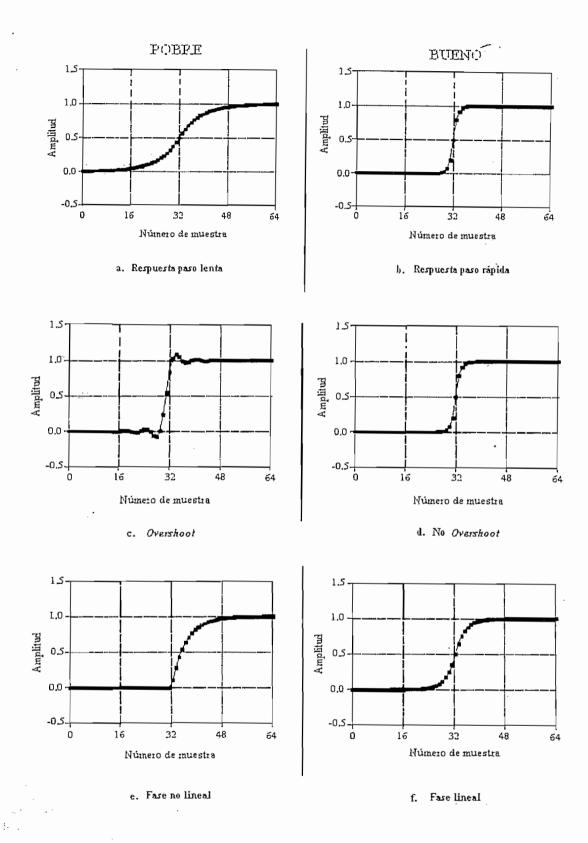

Figura 2.2 Parámetros para la evaluación de las características en el dominio del tiempo.[14]

Por ejemplo si se desea analizar una señal de origen desconocido la primera cosa que se debe hacer es dividir la señal en regiones de características similares. Algunas de las regiones podrían ser uniformes; otras tendrían grandes picos de amplitud o contendrían ruido. Ésta segmentación se logra por identificación de los puntos que separan las regiones. La función paso es la manera más pura de representar una división entre dos regiones distintas. Esto puede indicar cuando un evento empieza, o cuando un evento termina.

Los parámetros de la respuesta paso que son importantes en el diseño de filtros se indican en la figura 2.2. Para distinguir los eventos en una señal, la duración de la respuesta paso debe ser más corta que los espacios de los eventos. Es por esto que la respuesta paso debe ser lo más rápida como sea posible, a ésta velocidad de transición se conoce como *risetime*, este parámetro se ilustra en la figura (a) y (b).

Las figuras (c) y (d) hacen referencia a un parámetro que mide el nivel de rizado u overshoot en la respuesta paso. Se debe generalmente eliminar el overshoot ya que la amplitud de las muestras cambian en la señal; esto es una distorsión básica de la información contenida en el dominio del tiempo.

Finalmente, a menudo se desea que la mitad superior de la respuesta paso sea simétrica con la mitad inferior, como ilustra en los literales (e) y (f). Esta simetría es llamada *fase lineal*, debido a que la forma de la respuesta de fase es una línea recta.

#### 2.1.1.2 Parámetros del Dominio de la Frecuencia

En el diseño de filtros selectivos en frecuencia, las características deseadas de un filtro se especifican como función de la variable frecuencia " $\omega$ " denominada respuesta de frecuencia. Se denomina respuesta de frecuencia a  $H(\omega)$  dado que define la respuesta del sistema en el dominio de la frecuencia, análogamente,  $|H(\omega)|$  es la respuesta de amplitud y  $\Theta(\omega)$  es la respuesta de fase del sistema.

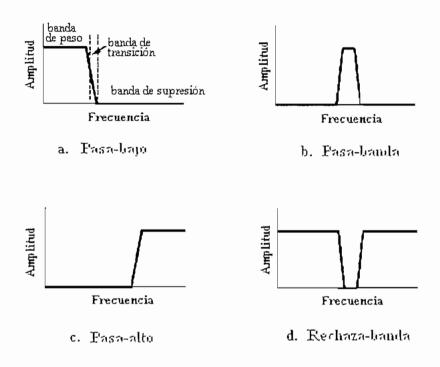

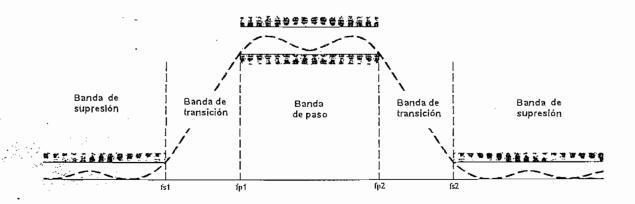

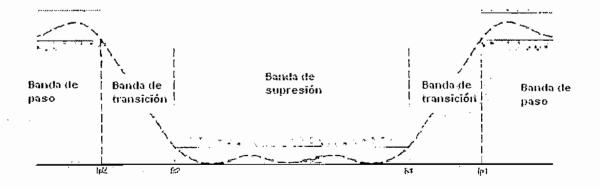

La Figura 2.3 indica las cuatro respuestas de frecuencia básicas. El propósito de éstos filtros es permitir pasar algunas frecuencias sin alterarlas, mientras se bloquean completamente otras.

Figura 2.3 Respuestas de frecuencia comunes. [14]

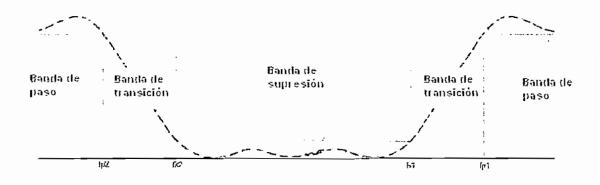

La banda de paso se refiere a las frecuencias que permite pasar el filtro, mientras que la banda de supresión, eliminada o de parada contiene las frecuencias que se bloquean o retienen. En medio de estas dos bandas se encuentra la banda de transición. Un factor de roll-off rápido significa que la banda de transición es muy estrecha. El punto que separa la banda de paso y la banda de transición se llama cut off frequency, frecuencia de corte.

En el diseño de filtros analógicos la frecuencia de corte, usualmente se define en donde la amplitud se reduce a 0.707 (-3dB). Los filtros digitales son los menos estandarizados, y es común ver níveles de amplitud del 99%, 90%, 70.7%, y 50% definidos para frecuencias de corte [14].

Figura 2.4 Parámetros para la evaluación del desempeño en el dominio de la frecuencia. [14]

La figura 2.4 indica tres parámetros que miden el rendimiento de un filtro en el dominio de la frecuencia. Al separar en cortos espacios de frecuencias, el filtro

debería tener un rápido *roll-off*, como se ilustra en (a) y (b); no debe haber ninguna ondulación en la banda de paso, como muestra en (c) y (d); es necesario tener una buena atenuación en la banda de supresión, como se observa en (e) y (f).

## 2.1.2 FILTROS DIGITALES FIR e IIR

La mejor manera de implementar un filtro digital es *convolucionando* <sup>[5, 7]</sup> la señal de entrada con la respuesta impulsiva del filtro. Cuando la respuesta impulsiva es usada de ésta manera, el diseño de los filtros tiene un nombre especial: **Filtros** de *Kernel*. Otra manera de diseñar filtros digitales, es mediante **Recursión**. <sup>[5, 7]</sup>

Para encontrar la respuesta impulsiva de un filtro recursivo, simplemente se alimenta de un impulso en la entrada. Las respuestas impulsivas de filtros recursivos están compuestas por sinusoides que decaen exponencialmente en amplitud. En principio, esto hace que su respuesta impulsiva sea infinitamente larga.

Sin embargo, la amplitud eventualmente cae por debajo del ruido *round-off* <sup>1</sup> del sistema, y las muestras que quedan pueden ser ignoradas. A causa de ésta característica, los Filtros Recursivos también son llamados Filtros IIR (*Infinite Impulse Response*, Respuesta Impulsiva Infinita). En comparación, los filtros que son realizados por convolución son llamados Filtros FIR (*Finite Impulse Response*, Respuesta Impulsiva Finita).

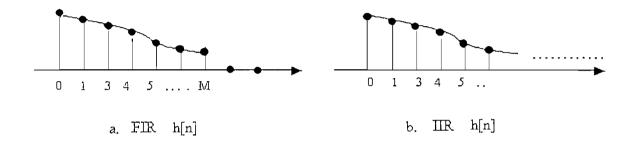

Un filtro digital es un sistema LTI, el cual pueden ser clasificado en Sistemas FIR e IIR como se ilustra en la figura 2.5, dependiendo si su respuesta impulsiva es finita o infinita.

El Ruido Round Off es el error causado por redondeo de los cálculos matemáticos para los niveles de cuantización más cercanos.

Los filtros FIR también llamados no recursivos o de convolución, tienen una respuesta impulsiva h[n] que se extiende sólo sobre un intervalo de tiempo finito, es decir  $0 \le n \le M$ , y es igual a cero para otros valores.

$$\{h_0, h_1, h_2, \dots, h_M, 0, 0, 0, 0, \dots\}$$

Figura 2.5 Respuesta impulsiva (a) Sistema FIR y (b) Sistema IIR [7]

donde M indica el orden del filtro.

Los coeficientes de la respuesta impulsiva h[n] son conocidos como coeficientes del filtro o pesos del filtro.

La salida de un filtro puede expresarse como una convolución finita, es decir:

$$y(n) = \sum_{m=0}^{M} h(m) x(n-m)$$

(2.1a)

$$y(n) = h_0 x(n) + h_1 x(n-1) + \dots + h_M x(n-M)$$

(2.1b)

donde x representa la secuencia de entrada a ser filtrada, h son los coeficientes del filtro FIR, e 1/2 representa la secuencia de salida filtrada.

Los filtros IIR tienen una respuesta impulsiva h[n] de duración infinita, definida sobre el intervalo infinito  $0 \le n \le \infty$ . La ecuación de un filtro IIR se representa por:

$$y(n) = \sum_{m=0}^{\infty} h(m)x(n-m)$$

(2.2)

#### 2.1.3 COMENTARIOS SOBRE LOS FILTROS FIR E IIR

La elección entre filtros FIR e IIR depende de la importancia que tengan para el problema de diseño las ventajas de cada tipo. Por ejemplo, los Filtros IIR, tiene la ventaja de que se puede diseñar una gran variedad de filtros selectivos en frecuencia utilizando fórmulas cerradas; es decir una vez que se ha especificado el problema en términos que sean apropiados para un determinado método de aproximación, se calcula el orden del filtro que cumplirá las especificaciones y se obtienen los coeficientes (o los polos y ceros) del filtro mediante sustitución directa en un sistema de ecuaciones de diseño. Ésta simplicidad de procedimiento de diseño hace que se puedan diseñar filtros IIR de forma manual si fuera necesario, y producir programas de computador no iterativos.

Éstos métodos se limitan a filtros selectivos en frecuencia y solo se permite especificar el módulo de la respuesta en frecuencia. Si se desean otras formas del módulo, o es necesario aproximar una respuesta de fase o retardo de grupo predeterminado, se requiere un procedimiento algorítmico.

Por el contrario, los filtro FIR pueden tener una fase lineal (generalizada) de forma precisa. Sin embargo, no existen ecuaciones de diseño en forma cerrada para filtros FIR. Aunque el método de ventanas es sencillo de aplicar, puede ser necesaria alguna iteración para cumplir unas determinadas especificaciones. Además, el método de ventanas y la mayor parte de los procedimientos algorítmicos permiten la posibilidad de aproximar características de respuesta en frecuencia arbitrarias, con solo un poco más de dificultad de la necesaria para diseñar filtros pasa bajo.

Adicionalmente el problema de diseño de filtros FIR está mucho más controlado que el diseño de filtros IIR, debido a la existencia de teoremas de optimización para filtros FIR aplicable en un amplio rango de situaciones prácticas.

Las cuestiones económicas deben ser también tenidas en cuenta al realizar filtros, éstas cuestiones se miden generalmente en términos de complejidad del hardware, área del chip o velocidad computacional. Éstos factores están relacionados mas o menos directamente con el orden del filtro necesario para cumplir una determinada especificación.

Dejando de lado las consideraciones sobre la fase, generalmente es cierto que una determinada especificación de la respuesta de amplitud se puede concebir de forma más eficiente empleando un filtro IIR. Sin embargo, en muchos casos la fase lineal que se puede conseguir utilizando un filtro FIR, puede compensar el costo adicional.

Los filtros FIR pueden ser tan eficientes como los IIR, además existen microcomputadoras orientadas al tratamiento digital de señales cuyas capacidades aritméticas están diseñadas para acumular sumas de productos como los que aparecen en los filtros FIR.

Por tanto, hay varios compromisos a considerar en el diseño de un filtro. En definitiva, la elección final se basará muy a menudo en juicios de Ingeniería sobre la formulación de las especificaciones, el método de realización del filtro, y los procedimientos computacionales y *software* disponible para realizar el diseño.

## 2.2 MÉTODOS DE DISEÑO

El problema del diseño de filtros digitales es el de construir la función de transferencia de un filtro que cumpla con especificaciones que garanticen un buen desempeño en el dominio de la frecuencia.

La entrada para un método de diseño de un filtro es el establecimiento de especificaciones deseadas; y, la salida es el vector formado por los coeficientes de respuesta de la función impulsiva finita  $h = [h_0, h_1, ....., h_{N-1}]$  en el caso de filtros FIR o los coeficientes de los vectores del numerador y denominador  $b = [b_0, b_1, ....., b_M]$ ,  $a = [1, a_1, ....., a_M]$  en el caso de filtros IIR.

Las dos principales ventajas de los filtros FIR son la fase lineal y la garantía de estabilidad debido a la ausencia de polos. Su desventaja potencial es que requiere de sus especificaciones bien definidas que pueden afectar la longitud de los filtros, consecuentemente incrementando su costo computacional.

Las principales ventajas de los filtros IIR son su bajo costo computacional y su implementación eficiente en cascada de secciones de segundo orden. Su principal desventaja es su potencial inestabilidad introducida cuando la cuantización de los coeficientes desplaza los polos fuera del círculo unitario. Para filtros IIR, la fase lineal no puede ser realizada exactamente sobre el intervalo total de *Nyquist*, pero esto puede ser logrado aproximadamente sobre la banda de paso relevante del filtro, por ejemplo, usando diseños de filtros de *Bessel*.

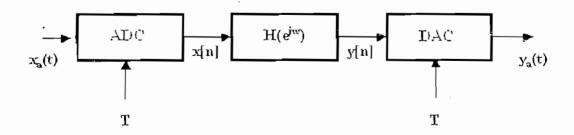

Cuando se utiliza un filtro en tiempo discreto para realizar el tratamiento en tiempo discreto de señales en tiempo continuo empleando una configuración como la que se indica en la figura.2.6, tanto las especificaciones del filtro en tiempo discreto como en tiempo continuo se suelen dar en el dominio de la frecuencia.

Figura 2.6 Sistema básico para el filtrado en tiempo discreto de señales en tiempo continuo.

Esto es particularmente cierto para el caso de filtros selectivos en frecuencia como los filtros pasa bajo, pasa banda y pasa alto. Si se usa un sistema lineal e invariante en el tiempo como el de la figura 2.6, el sistema completo se comporta como un sistema en tiempo continuo lineal e invariante con el tiempo cuya respuesta en frecuencia es:

$$H_{eff}(j\Omega) = \begin{cases} H(e^{j\Omega T}) & |\Omega| < \pi/T \\ 0 & |\Omega| > \pi/T \end{cases}$$

(2.3)

Para convertir las especificaciones del filtro en tiempo continuo en especificaciones del filtro en tiempo discreto, se utiliza la relación  $\omega = \Omega T$  donde  $\Omega$  es la frecuencia normalizada. Es decir,  $H(e^{i\omega})$  se especifica sólo en un periodo mediante la ecuación:

$$H(e^{j\omega}) = H_{eff}(j\frac{\omega}{T}), \qquad |\omega| < \pi$$

(2.4)

donde:

$\omega$  = Variable de frecuencia.

T = Período de muestreo

# 2.2.1 DETERMINACIÓN DE LAS ESPECIFICACIONES DE UN FILTRO EN TIEMPO DISCRETO

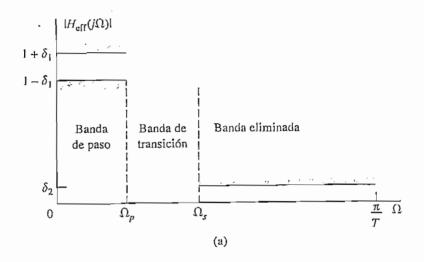

En un filtro pasa bajo en tiempo discreto, el cual se va a utilizar para filtrar una señal en tiempo continuo por medio de la configuración básica de la figura 2.6, se busca que el sistema completo de la figura tenga las siguientes propiedades para una determinada frecuencia de muestreo  $f_m$ . (El periodo de muestreo es  $T = 1 / f_m$ ).

- 1. La ganancia  $|H_{eff}(j\Omega)|$  debe diferir de la unidad en un factor de  $\pm \delta_1$  en la banda  $0 \le \Omega \le \omega_p$ ; en donde  $\delta_1$  es el factor de rizado en la banda de paso y  $\omega_p$  es la frecuencia de paso.

- 2. La ganancia no debe ser mayor que  $\delta_2$  en la banda de frecuencias  $\omega_s \leq \Omega$ ; donde  $\delta_2$  es el factor de rizado en la banda de supresión y  $\omega_s$  es la frecuencia de supresión.

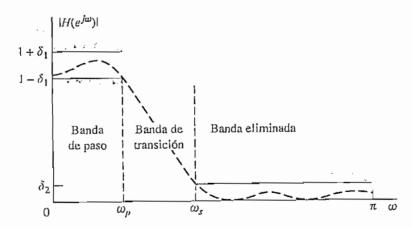

Figura 2.7 Especificaciones de un filtro pasa bajo [5]

a) Especificaciones de la respuesta de frecuencia del sistema de la figura 2.6.

b) Especificaciones del filtro discreto de la figura 2.6.

Por tanto en este caso, la ganancia ideal en la banda de paso es la unidad. La ganancia en la banda de paso varía entre  $(1+\delta_1)$  y  $(1-\delta_1)$ , y la ganancia en la

banda de supresión varía entre 0 y  $\delta_2$ . Es habitual expresar las máximas ganancias en la banda de paso y en la banda de supresión en decibelios.

- o Ganancia ideal de la banda de paso en decibelios =  $20 \log_{10}(1) = 0 dB$

- o Máxima ganancia de la banda de paso en decibelios = 20  $log_{10}(1+\delta_1)$

- o Máxima ganancia de la banda eliminada en decibelios = 20  $\log_{10}(\delta_2)$ .

Para una frecuencia de muestreo  $f_m$ , la ganancia del sistema completo es cero por encima de  $\Omega = 2\pi (f_m / 2)$ .

La Figura 2.7(b) muestra el esquema de tolerancias del filtro en tiempo discreto. Es similar al de la Figura 2.7(a), salvo porque se dibuja en función de la frecuencia normalizada ( $\omega = \Omega T$ ), y sólo es necesario dibujarlo en el intervalo  $0 \le \omega \le \pi$ , ya que el resto se puede deducir de las propiedades de simetría (suponiendo que h[n] es real) y de la periodicidad de  $H(e^{j\omega})$ . A partir de la Ecuación (2.4) se puede deducir que en la banda de paso el módulo de la respuesta en frecuencia debe aproximarse a la unidad con un error menor que  $\pm \delta_1$ , es decir:

$$(1 - \delta_1) \le \left| H(e^{j\omega}) \right| \le (1 + \delta_1), \qquad |\omega| \le \omega_{\rho} \tag{2.5}$$

siendo  $\delta_1$  y  $\omega_p = 2\pi . f_p. f_m$  radianes. La otra banda de aproximación es la banda de supresión en la que la respuesta en amplitud se debe aproximar a cero con un error menor que  $\delta_2$ ; es decir:

$$|H(e^{j\omega})| \le \delta_2, \qquad \omega_s \le |\omega| \le \pi$$

(2.6)

$\delta_2$  y  $\omega_s = 2\pi.f_s.f_m$  radianes. La frecuencia de corte de la banda de paso  $\omega_p$  y la frecuencia de corte de la banda eliminada  $\omega_s$ , se dan en unidades de frecuencia

angular normalizada, o equivalentemente en unidades de fase en el plano z. Para aproximarse de ésta forma al filtro pasa bajo ideal con un sistema realizable que proporciona una banda de transición no nula  $(\omega_s - \omega_p)$  en la que el módulo de la respuesta varíe suavemente de la banda de paso a la banda de supresión. La curva discontinua de la Figura 2.6(b) es la respuesta de amplitud de un sistema que cumple las especificaciones dadas.

## 2.2.2 MÉTODO DE VENTANAS PARA FILTROS FIR

Los filtros FIR están restringidos casi totalmente a realizaciones en tiempo discreto. En consecuncia, las técnicas de diseño de filtros FIR se basan en aproximar directamente la respuesta de frecuencia deseada del sistema en tiempo discreto; la mayoría de técnicas de aproximación de la respuesta de amplitud de un sistema FIR asumen una restricción de fase lineal.

El método más simple de diseño de filtros FIR se denomina método de ventanas.

Este método empieza generalmente con una respuesta de frecuencia deseada ideal que se puede representar como:

$$H_d(e^{j\omega}) = \sum_{n=-\infty}^{\infty} h_d[n]e^{-j\omega n}$$

(2.7)

Siendo  $h_d[n]$  la correspondiente secuencia de respuesta al impulso, que se puede expresar en función de  $H_d(e^{j\omega})$  como:

$$h_d[n] = \frac{1}{2\pi} \int_{-\pi}^{\pi} H_d[e^{j\omega}] e^{j\omega n} d\omega$$

(2.8)

Muchos sistemas se definen de forma idealizada mediante respuestas de frecuencia constantes por tramos con discontinuidades en los límites de las bandas. Como resultado, la respuesta al impulso de éstos sistemas es no causal

e infinitamente larga. La forma más directa de obtener una aproximación FIR causal a éstos sistemas es truncar la respuesta ideal.

La ecuación (2.7) puede verse como el desarrollo en series de *Fourier* de la respuesta de frecuencia periódica  $H_d(e^{j\omega})$  donde los valores de la secuencia  $h_d[n]$  juegan el papel de coeficientes del desarrollo en serie de *Fourier*. Por tanto, la aproximación de un filtro ideal mediante el truncamiento de la respuesta al impulso ideal es idéntica al tema de la convergencia del desarrollo en series de *Fourier*.

La forma más simple de obtener un filtro FIR causal a partir de  $h_d[n]$  es definir un nuevo sistema con respuesta al impulso h[n] dado por :

$$h[n] = \begin{cases} h_d[n] & 0 \le n \le M \\ 0 & \text{en el resto} \end{cases}$$

(2.9)

De forma mas general, h[n] se puede representar como el producto de la respuesta al impulso deseada  $h_d[n]$  y una ventana de longitud finita  $\omega[n]$ , es decir:

$$h[n] = h_d[n] \ \omega[n] \tag{2.10}$$

donde, para el truncamiento simple que indica la ecuación (2.9), la ventana aplicada se denomina ventana rectangular.

$$w[n] = \begin{cases} I & 0 \le n \le M \\ 0 & \text{en el resto} \end{cases}$$

(2.11)

Utilizando el teorema de modulación[2] o enventanado se puede ver que:

$$H[e^{j\omega}] = \frac{1}{2\pi} \int_{-\pi}^{\pi} H_d[e^{j\omega}] W(e^{j(\omega-\theta)}) d\theta$$

(2.12)

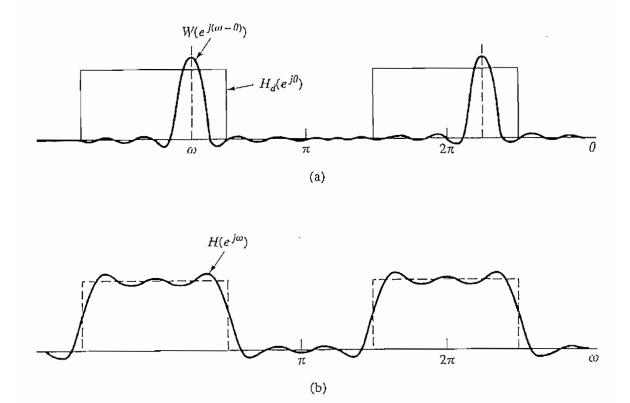

Es decir,  $H(e^{j\omega})$  es la convolución periódica de la respuesta en frecuencia ideal deseada con la trasformada de Fourier de la ventana. Por tanto, la respuesta de frecuencia  $H(e^{j\omega})$  será una versión "distorsionada" de la respuesta deseada  $H_d(e^{j\omega})$ . La figura 2.8(a) muestra funciones típicas  $H_d(e^{j\omega})$  y  $W(e^{j(\omega-0)})$  como se usarían en la ecuación (2.12).

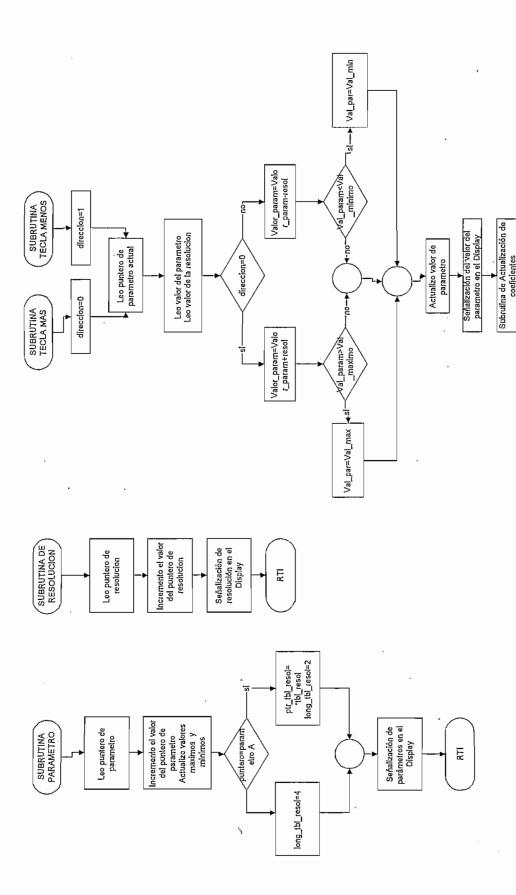

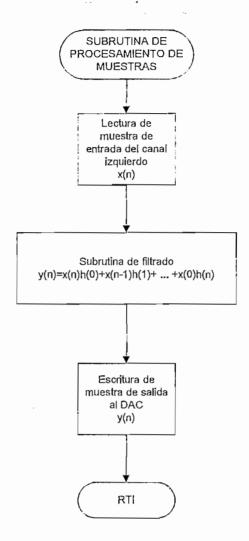

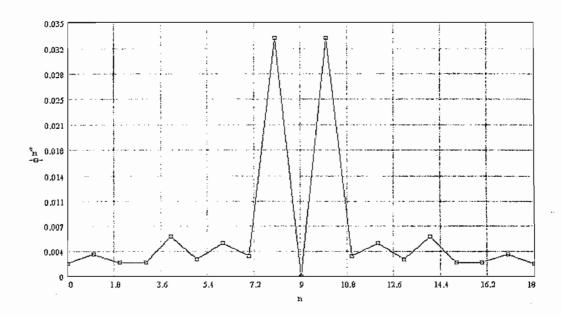

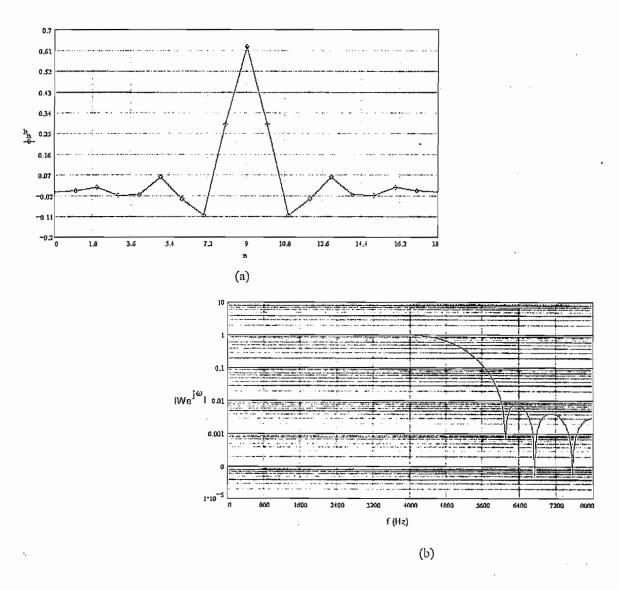

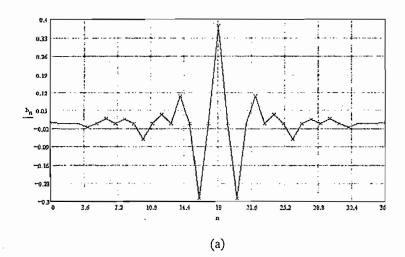

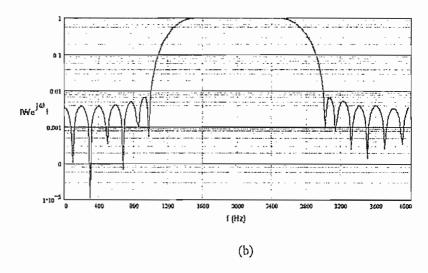

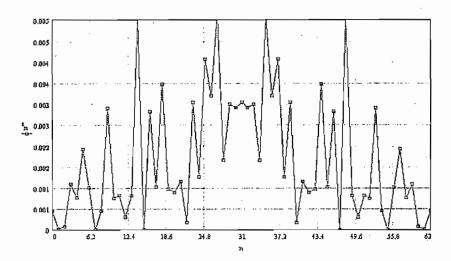

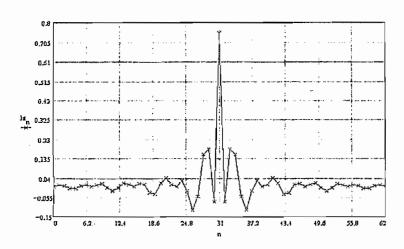

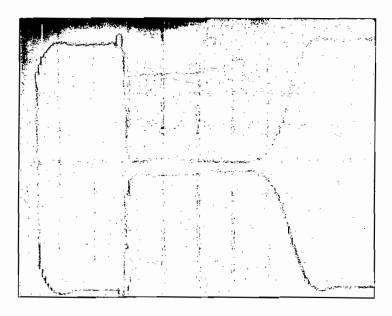

Figura 2.8 (a). Proceso de convolución implicado por el truncamiento de la respuesta impulso ideal (b). Aproximación típica resultante del enventanado de la respuesta al impulso ideal