GRAFIZADOR DE CARACTERISTICAS DE TRANSISTORES EN EMISOR

COMUN

Tesis previa a la obtención del título de Ingeniero en la especialización de Electrónica y Telecomunicaciones de la Escuela Politécnica Nacional.

CARLOS ALBERTO SERRANO CISNEROS

QUITO

Diciembre de 1.973

Certifico que este trabajo ha sido realizado en su to talidad por el Sr. Carlos A. Serrano Cisneros.

Zmanicio Vega V.

Ing. Mauricio Vega CONSULTOR DE TESIS

Quito, Diciembre de 1.973

A MI ESPOSA MARIA GRACIELA

A MI HIJA CARLA PAOLA

A MI MADRE CLEMENCIA DE REYES

# AGRADECIMIENTO

A mis hermanos en cuyo estímulo diario encontré apoyo mo ral y fuerzas para culminar mi carrera.

A todos los ecuatorianos que aportan para la creación de nuevos Ingenieros en las Universidades y particularmente en la Escuela Politécnica Nacional.

A mis amigos y profesores en especial a los Ings. Mauricio Vega y Jacinto Jijón quienes donaron su iniciativa y visión práctica para llevar a felíz culminación esta tesis.

A todos mis compañeros del Departamento de Electrónica - particularmente a los Sres. Dr. Kanti Hore, Erwin Barriga y - Marcelo Guarderas.

### PROLOGO

En la epoca actual en que verdaderamente se siente la necesidad de desarrollar nuestro Pais, la juventud pensante ecuato riana forjada con un criterio futurista en las Universidades, ha creido concientemente que una de las maneras de lograrlo, es creando una tecnología propia que esté de acuerdo con el medio ambiente y alcance a cubrir las necesidades de este pueblo; con esto no se tiende una barrera a la tecnología extranjera, sino que se puede hacer uso de ella para fortificar la nuestra; criterio del que participo y a mi sencillo juicio me parece muy acertado.

Si de lo antes expuesto se ha de partir, no se pretenda - creer que el trabajo que contiene esta tesis, es fruto de una - tecnología propia, pues, es de exponerse el hecho de que si algo del mismo resulta nuevo y útil, no será más que simplemente por experiencias personales de laboratorio y afán de lograr simplificar el conocimiento de Electrónica particularmente y el de los - Transistores en general.

Me complace indicar que si el diseño electrónico del aparato construido sigue procedimientos tradicionales, no todo se ajusta a él, sino que también contiene conceptos y consideraciones que los he creido lógicos y que en primera instancia lo ha

en la materia que trata este trabajo de tesis, podrá parecerles que se ha seguido un camino demasiado largo para conseguir el ok jetivo de la misma, sin embargo cabe mencionarse sin ningún sentido de justificación, el hecho que si bien es cierto un aparato debe ser lo más sencillo posible, no es menos cierto también que éste debe brindar garantía y seguridad en su manejo, aunque para conseguirlo sea necesario dejar en un plano secundario la sencillez; anhelo sobre manera que el presente trabajo teórico y su creación práctica brinden la confianza, sencillez y seguridad deseadas y aporten provechosamente para la creación de una tecnología tan buscada por la juventud actual.

Finalmente mi reconocimiento a mi esposa María Graciela quien me ayudó a transcribir este trabajo.

# INDICE GENERAL

|          |                                                                                                                           | Página |

|----------|---------------------------------------------------------------------------------------------------------------------------|--------|

| Pı       | rologo                                                                                                                    | v      |

| CAPITULO | PRIMERO INTRODUCCION                                                                                                      | 1      |

| CAPITULO | SEGUNDO DIAGRAMA BLOQUE PARCIAL Y TOTAL DEL SISTEMA                                                                       | 5      |

|          | A Análisis preliminar                                                                                                     | 6      |

|          | <ul><li>B Diagrama bloque de un generador de tensión tipo escalera</li><li>C Diagrama bloque de un generador de</li></ul> | 13     |

|          | onda triangular                                                                                                           | 19     |

| CAPITULO | TERCERO DISEÑO CIRCUITAL                                                                                                  | 25     |

|          | A Diseño del generador de tensión                                                                                         |        |

|          | tipo escalera                                                                                                             | 26     |

|          | a1 Diseño del circuito de disparo                                                                                         | 26     |

|          | a2 Multivibrador Astable acoplado                                                                                         |        |

|          | por colector                                                                                                              | 27     |

|          | a3 Tiempo de cada parte de un ciclo                                                                                       | 30     |

|          | a4 Diseño del Multivibrador Astable                                                                                       | 32     |

| a5   | Diseño de los multivibradores biesta- |    |

|------|---------------------------------------|----|

|      | bles con transistores                 | 35 |

| a6   | Clasificación de los Flip-Flops       | 36 |

| a7   | Consideraciones prácticas de diseño   | 37 |

| a8   | Determinación de los estados esta-    |    |

|      | bles de un Flip-Flop                  | 40 |

| a9   | Diseño numérico de un Flip-Flop       | 42 |

| a10  | Introducción a los condensadores      |    |

|      | de aceleración o conmutación          | 48 |

| a11  | Formas de disparar un binario         | 53 |

| a12  | Disparo simétrico de un binario       |    |

|      | por las bases                         | 55 |

| a13  | Diseño de los amplificadores          |    |

|      | operacionales                         | 62 |

| a14  | Diseño del amplificador operacional   |    |

|      | que será usado como sumador           | 66 |

| a15  | Determinación de la ganancia          | 67 |

| a16  | Funcionamiento del amplificador       |    |

|      | diseñado como sumador                 | 71 |

| a17  | Diseño de los sistemas resistivos     |    |

|      | para control de corriente             | 75 |

| a18  | Cálculo de las resistencias de emisor |    |

|      | del transistor de prueba, en relación |    |

|      | con las diferentes corrientes de base | 79 |

| B Di | seño del generador de onda triangular | 82 |

|          | D 1   | Disend del ampilitador operacional       |     |

|----------|-------|------------------------------------------|-----|

|          |       | a ser usado como integrador              | 83  |

|          | b2    | Funcionamiento del amplificador opera    |     |

|          |       | cional usado como integrador             | 87  |

|          | b3    | Cálculo de Z=R para determinar las       |     |

|          |       | tensiones máxima y mínima de salida      | 95  |

|          | C D   | iseño de las fuentes de alimentación del |     |

|          | s:    | istema                                   | 102 |

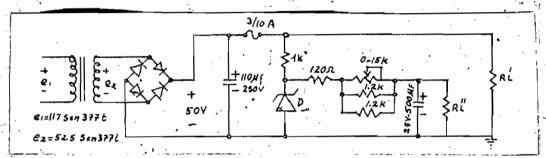

|          | c1.   | Diseño de una fuente de poder de 50v     |     |

|          |       | y una estabilizada y regulable de 4 a 9v | 102 |

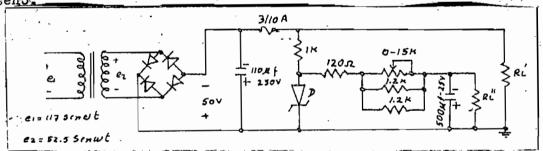

|          | c2    | Filtro de condensador y fuente de poder  |     |

|          |       | de 50v DC.                               | 103 |

|          | c3    | Fuente de poder estabilizada y           |     |

|          |       | regulable de 4 a 9v                      | 106 |

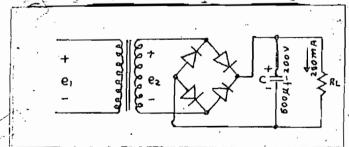

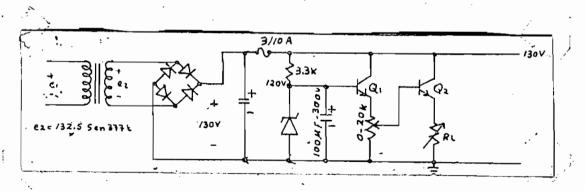

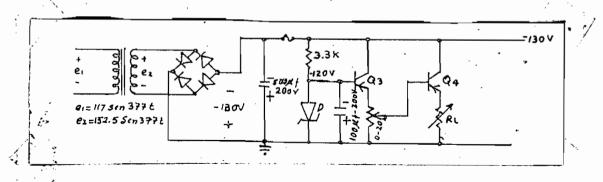

|          | c4    | Fuente de poder regulable de 0 a 120v    | 110 |

|          |       |                                          |     |

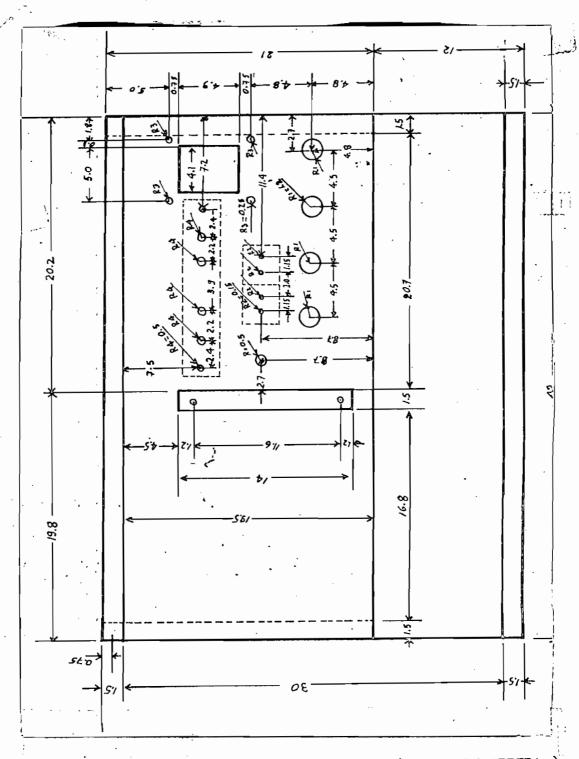

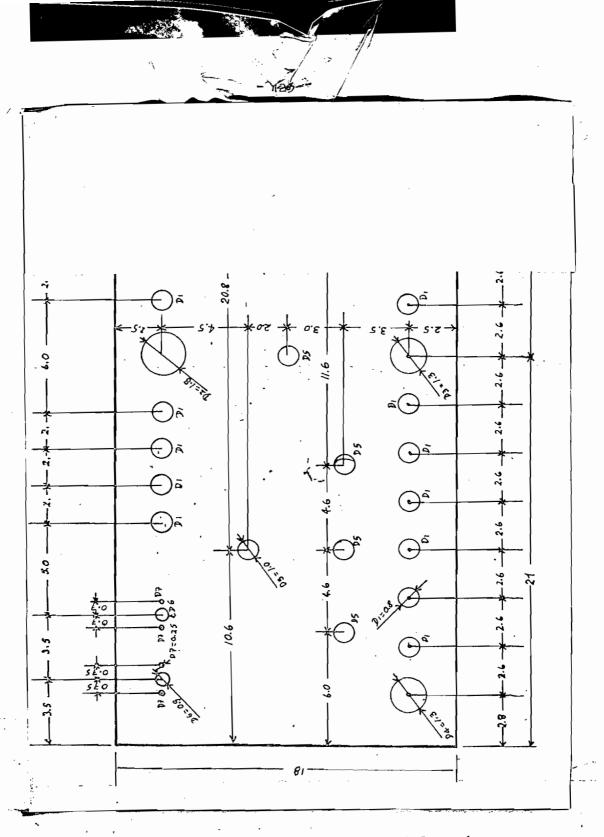

| CAPITULO | CUART | O CONSTRUCCION DEL EQUIPO DISEÑADO       | 117 |

|          |       |                                          |     |

| CAPITULO | QUINT | O RESULTADOS EXPERIMENTALES Y            |     |

|          |       | CONCLUSIONES                             | 128 |

|          |       |                                          | ·   |

| -        | Compa | ración de los valores calculados         |     |

|          | con l | os medidos                               | 129 |

|          | Concl | usiones                                  | 131 |

|          | Bibli | ografía                                  | 132 |

CAPITULO PRIMERO

TNTRODIT-CCTON

#### INTRODUCCION.

El objetivo primordial de este trabajo, es lograr hacer algo útil para la enseñanza práctica del estudiante de Ingenie ría Electrónica de la Escuela Politécnica Nacional. Al referirme al término útil, pongo en conocimiento de las personas a cuyas manos llegue este trabajo, el hecho de que la parterpráctica fruta de la teoría que contiene esta tesis, está equipado de tal manera que el estudiante que comienza a conocerellectrónica y por ende los transistores, tenga en este aparato una ayuda en el sentido de que podrá observar objetivamente las variaciones de polarización de un transistor, variaciones en la inclinación de la recta de carga, y, comportamiento electrónico del mismo con variaciones en su corriente de base, así como también las características Colector Emisor de aquellos transistores cuyo comportamiento se desconoce o no existen en manuales.

En lo que al diseño propiamente se refiere, cabe mencio narse el hecho de que este trabajo presenta pocas obras de con sulta pues una gran parte de él fue diseñado con experiencias prácticas obtenidas en el laboratorio de Electrónica, a más de los conocimientos teóricos adquiridos cuando estudiante, época de la cual los resúmenes de Electrónica fueron mis mejores — aliados.

De lo expuesto anteriormente, se desprende con claridad el que este trabajo no será una fuente de virtudes, sino más - bien una pequeña recopilación de ciertas consideraciones prác

ticas de diseño que las he creido de especial importancia, dadas a conocer a medida que se avanza en la lectura de esta tesis y - en el desarrollo de las diferentes partes constitutivas de la - misma.

En lo que al capítulo I se refiere, he deseado desarro - llar este trabajo de una manera objetiva a base de formas de onda y diagramas bloque, los mismos que ha medida que han ido cre- ándose han dejado al descubierto la necesidad de un próximo paso o bloque hasta llegar a culminar en un diagrama total, que reflejará las partes a ser diseñadas bajo las condiciones de las necesidades creadas.

El capítulo II, contiene únicamente el diseño teórico de las partes constitutivas del equipo a ser construido, en el cual se da una especial importancia a las aproximaciones que son usua les en los circuitos electrónicos, especialmente en los circui—tos equivalentes. Este capítulo guarda en sus páginas análisis teóricos y consideraciones desprendidas de la práctica especialmente en la forma de disparo de los Flip-Flops y el uso de un am plificador operacional con un solo paso de amplificación a ser usado en la elaboración de los generadores de tensión en escalera y de onda triangular, así como también diseños completos y recomendaciones para los siguientes circuitos electrónicos que por cierto son muy usados y su tecnología bastante avanzada: Circuitos de reloj (Astable); multivibradores biestables (Flip-Flops); fuentes de poder estabilizadas y regulables; sistemas resistivos para control de corriente de base del transistor a ser probado y para control de corriente de base del transistor a ser probado y para control de corriente de base del transistor a ser probado y para control de corriente de base del transistor a ser probado y para control de corriente de base del transistor a ser probado y para control de corriente de base del transistor a ser probado y para control de corriente de la constante de la constante de la corriente de la corriente de la constante de la constante de la corriente de la corriente de la constante de la constante de la corriente de la corriente de la constante de la

resistencias de emisor del mismo transistor para tomar muestras.

de corriente de emisor, cuya consideración de que es similar a

la de colector es muy aceptable.

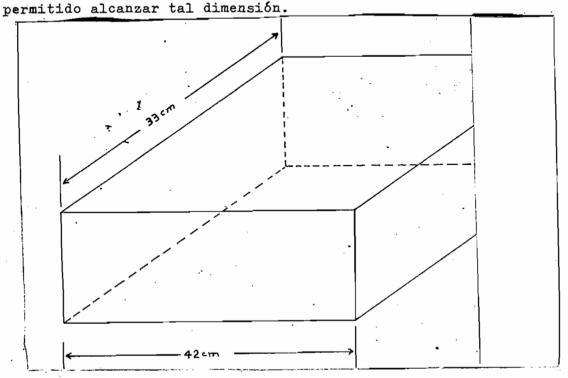

El capítulo IV contiene dimensiones del equipo construido fotografías del mismo, así como de las plaquetas constitutivas - y curvas obtenidas de algunos transistores haciendo uso del equipo diseñado.

El capítulo V es un fiel reflejo de lo conseguido prácticamente haciendo uso de lo teórico, en el cual se puede valorar objetivamente la concordancia de la teoría con la práctica, pudiéndose concluir con mucha claridad si las consideraciones hechas para el diseño son útiles o no.

CAPITULO SEGUNDO

D-IAGRAMA BLOQUE PARCIAL

Y TOTAL DEL SISTEMA

DIAGRAMA BLOQUE PARCIAL Y TOTAL DEL SISTEMA.

A menudo un problema de cualquier índole, es visualizado en mejor forma, cuando lo resolvemos gráficamente constituyendo se este hecho en el objetivo del presente capítulo.

### A .- ANALISIS PRELIMINAR.

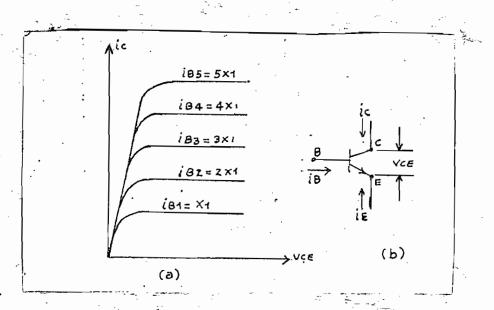

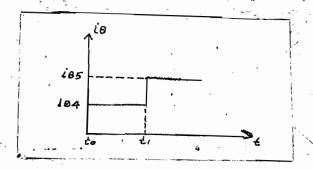

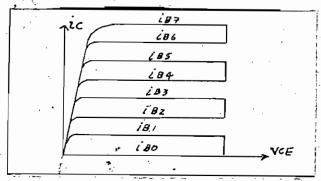

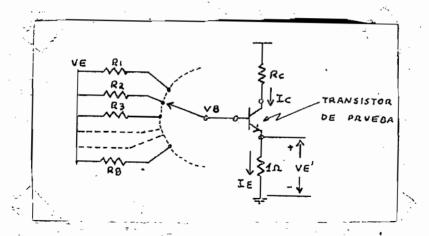

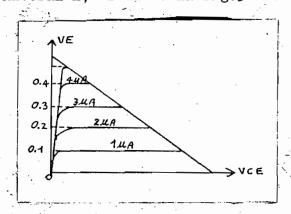

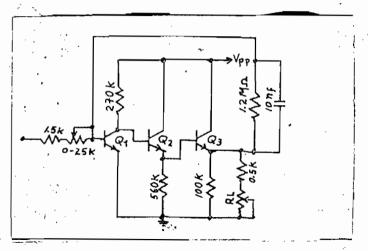

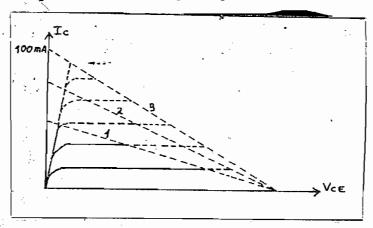

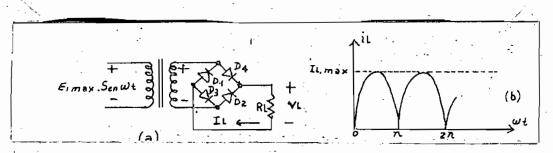

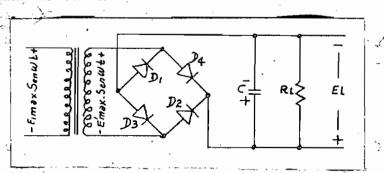

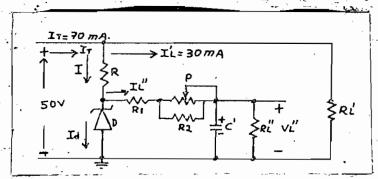

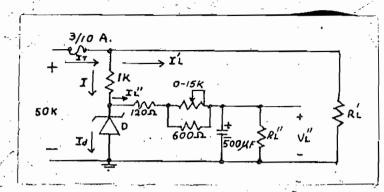

Partiremos de la meta de esta tesis, es decir, asumiendo que ya hemos obtenido en el osciloscopio las características colector emisor de un transistor conectado en emisor común Fig.2-l y analizándolas; de donde se desprende el hecho de que cada línea de corriente de base LB, posee un valor constante de lo cual haremos uso para realizar el análisis.

Fig. 2-1 (a) Características de un transistor en emisor común;(b) representación de un transistor.

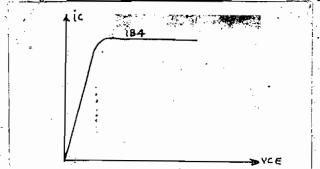

Es muy conocido que muchos problemas se los resuelve par tiendo del plano de la suposición, y haremos uso de este hecho para considerar que se tiene únicamente la línea de corriente - de base (B4 Fig.2-1 representada en la Fig. 2-2, la cual se man tiene constante aún cuando los valores de VCE e lc han variado, lo cual se lo justifica del modo siguiente: Fig.2-3 y 2-4.

Fig.2-2 Característica de un transistor en emisor común para una corriente de base constante.

Fig. 2-3 Linea de corriente de base constante como función del tiempo.

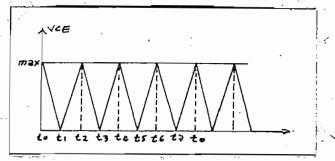

Fig. 2-4 Voltaje colector - emisor como función del tiem po.

A un tiempo t = to

$$v$$

CE = 0  $e$   $i$  B =  $i$  B4

A un tiempo t = t1  $v$  CE = A v.  $e$   $i$  B =  $i$  B4

A un tiempo t = t2  $v$  CE = B v.  $e$   $i$  B =  $i$  B4

A un tiempo t = t3  $v$  CE = C v.  $e$   $i$  B =  $i$  B4

A un tiempo t = t4  $v$  CE = D v.  $e$   $i$  B =  $i$  B4

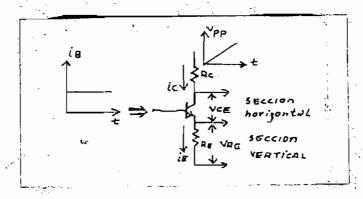

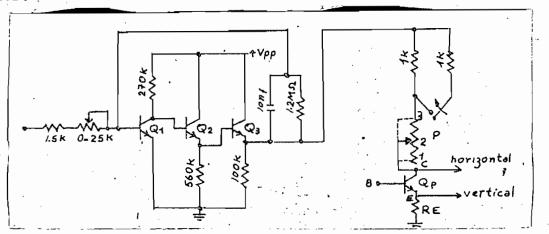

Luego, si en la configuración de la Fig. 2-5, polarizamos al transistor conectado en emisor común con una tensión de volta je rampa igual a la de la Fig. 2-4, e introduciendo una señal de corriente de base igual a la de la Fig. 2-3 y sacando señales de VCE e introduciendo en la sección horizontal del osciloscopio, - para ser usada como señal de barrido horizontal, obtendermos larepresentación gráfica en la pantalla del osciloscopio igual a - la de la Fig. 2-2, cuando una señal equivalente a la corriente - de colector del transistor, sea introducida en la sección vertical del mismo.

Fig. 2-5 Polarización del transistor de prueba.

Las siguientes ecuaciones representan el comportamiento de de un transistor en las que  $\beta$  es la amplificación de corriente para la configuración en emisor común y se lo define como la razón de transferencia de corriente continua en cortocircuito.

Este parámetro se obtiene facilmente de las características con emisor común, tomando la razón de la variación de la corriente de colector a la de la corriente de base a lo largo de una línea de VCE constante.

$$\beta = \frac{dic}{diB} | vcE, const.$$

$$VRE = iE \times RE = (iC + iB)RE$$

$$iB = \frac{iC}{\beta}$$

$$VRE = (iC + \frac{iC}{\beta})RE = iC(\frac{\beta + 1}{\beta})RE$$

(2-1)

Podríamos generalizar el caso en que  $\beta$  1, luego la Ec. - (2-1), se transforma con mucha aproximación en la Ec.(2-2), en - la que, cuando RE =  $1\Omega$ , entonces

$$\begin{aligned}

\nabla RE &= i C \times 1\Omega \\

|\nabla RE| &= |i C| \\

\nabla RE &\approx i C \times RE

\end{aligned} (2-2)$$

siendo una señal representada por la Ec.(2-2) la que usemos en - la parte vertical del osciloscopio para lograr nuestro objetivo.

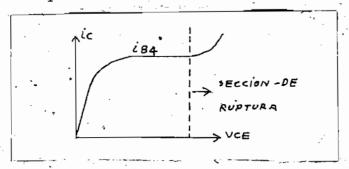

Si llegamos al caso en que VCE toma valores muy grandes, se puede llegar a la sección de ruptura del transistor Fig. 2-6 lo que se puede evitar de dos maneras:

- l.- Controlando el voltaje colector emisor o en definit $\underline{i}$  va el de polarización y

- 2.- Si llega a ser este el caso, se puede preservar un po

co más el transistor, limitando la corriente de colector con una resistencia Rc, la misma que tendrá más acción sobre las líneas de más alta corriente de base que sobre las de pequeña corriente, pudiéndose evitar que pasen por la zona de máxima disipación de potencia del transistor.

Fig. 2-6 Muestra de la sección de ruptura cuando VCE llega a valores altos.

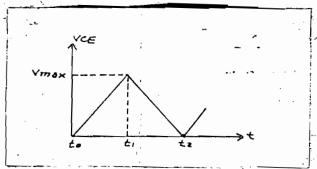

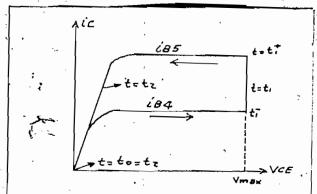

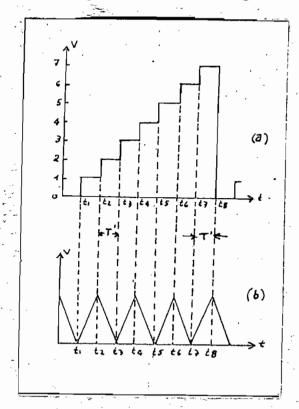

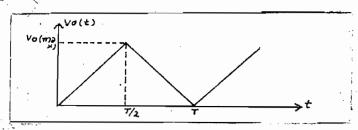

Continuando con nuestro análisis, veamos lo que sucede - cuando tenemos una corriente de base igual a la de la Fig. 2-7 - y el VCE sea aquel de la Fig. 2-8 . Del tiempo t=t0 al t=t1- el gráfico que se observará en el osciloscopio es el de la Fig. 2-2 pero en el instante t=t1+; la corriente de base cambia a - un valor  $\langle B=\langle B5\rangle$ ; estando el valor de VCE en su pico máximo, y comienza a descender en valor hasta llegar en el tiempo t=t2 - a un valor cero donde la corriente de colector  $\langle C$  será cero, manteniéndose constante la corriente de base en  $\langle B=\langle B5\rangle$ ; para este caso, el gráfico a observarse en el osciloscopio es el de la Fig. 2-9, donde el trazo de ida será por  $\langle B4\rangle$  y el de retorno - por  $\langle B5\rangle$ .

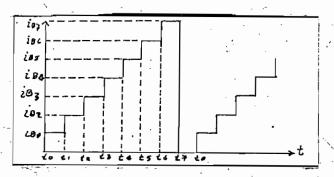

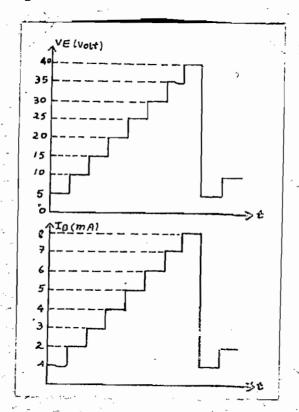

Veamos lo que sucede cuando la corriente de base tenga la forma de una escalera Fig. 2-10 y la tensión VCE la de una onda triangular Fig. 2-11

Fig. 2-7 Gráfico de la corriente de base con doble escalón como función del tiempo.

Fig. 2-8 VCE como función del tiempo cuando la polarización del transistor se realiza con una tensión triangular.

Fig. 2-9 Caracteristicas de un transistor cuando / B es la de la Fig. 2-7 y VCE es el de la Fig. 2-8.

Al tiempo t = t04;  $\sqrt{CE} = \sqrt{CE}$  max.  $e \ / B = / B1$ ; a partir - de este instante  $\sqrt{CE}$  decrecerá linealmente hasta el tiempo t = t1- momento en el que / B como  $\sqrt{CE}$  serán cero. En el instante - t = t7+, / B permanecerá en cero hasta el tiempo t1- mientras -  $\sqrt{CE}$  llegará a su punto máximo comenzando un nuevo ciclo de ocho

escalones en la corriente de base y en consecuencia un nuevo ba rrido completo en el osciloscopio. Si la frecuencia, tanto de - 1B como de VCE es suficientemente alta, se podrá observar en la pantalla del osciloscopio un trazo aparentemente instantáneo para la vista, de las ocho curvas características del transistor a ser probado, apareciendo todas simultáneamente como en la Fig. 2-12.

Fig. 2-10 Corriente de base tipo escalera.

Fig. 2-11 VCE de tipo onda triangular.

Fig. 2-12 Características de un transistor cuando lB es tipo es calera y VCE triangular.

Lógicamente los ejes de ordenadas tanto de 1C como de VCE, no aparecerán pero se puede en el osciloscopio tomar estas referencias, determinando el origen de las mismas. De este análisis y para cumplir con el propósito del presente capítulo, es una ne cesidad imperante obtener gráficamente tanto la corriente tipo escalera como la tensión tipo triangular, lo que se puede satisfacer del modo siguiente:

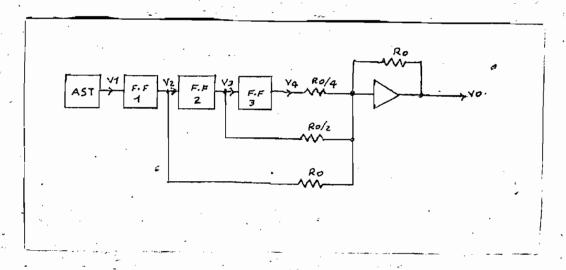

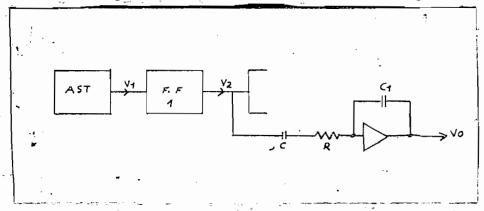

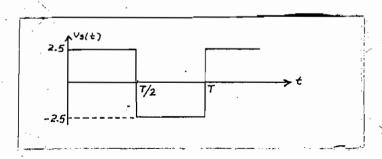

### B .- DIAGRAMA BLOQUE DE UN GENERADOR DE TENSION TIPO ESCALERA.

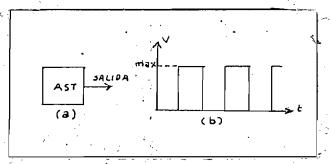

- 1.- Construimos un circuito Astable cuya función principal es oscilar a una frecuencia definida dando un tipo de onda rectan gular. La Fig. 2-13 muestra la representación a usarse para de terminar a un Astable como la forma de onda que genera y que será usada como la señal patrón o de reloj.

- 2.- Es imperante también tener circuitos biestables o Flip

-Flops, cuyas salidas se encuentran en corte y saturación, siendo

necesarios sacarles de estos estados con señales de disparo, adquiriendo el estado contrario, hasta que un nuevo disparo prove niente de una fuente exterior al circuito sea producido.

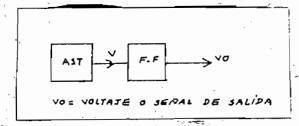

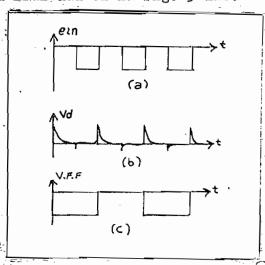

Fig. 2-13 (a) Representación gráfica de un circuito Astable (b) - Forma de onda que genera.

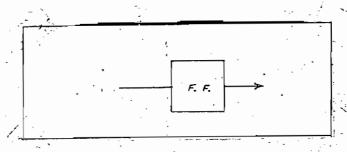

Fig. 2-14 Representación gráfica de un F.F.

Vo = voltaje o señal de sa - lida.

Fig. 2-15Forma de disparar al F.F.

La Fig. 2-14 ilustra la representación del circuito biestable y la Fig. 2-15 la forma de obtener el cambio de estado del Flip-Flop (F.F.), usando como señal de disparo la forma de onda -de salida del circuito Astable.

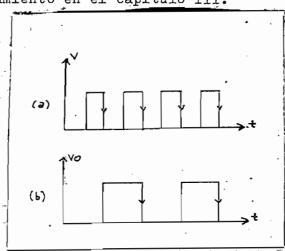

Como se observará en la Fig. 2-16 el circuito F.F. divide por dos la frecuencia de oscilación del Astable, justificandose - este comportamiento en el capítulo III.

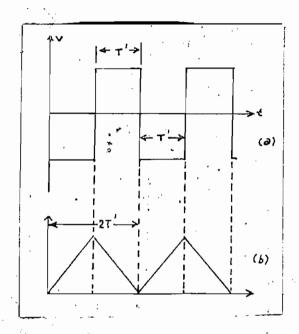

Fig. 2-16 (a) Señal del Astable (b) señal de salida del F.F.

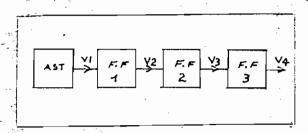

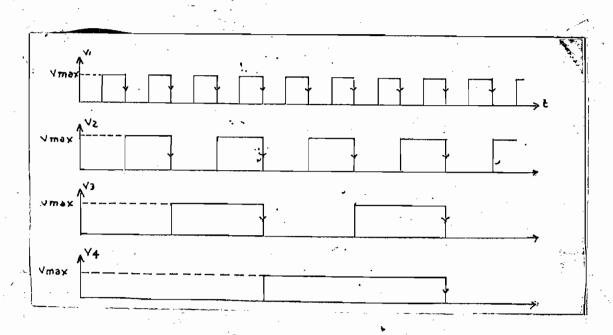

Si la señal del circuito de la Fig. 2-15 se usa como señal de reloj para un siguiente F.F. y la de este como señal de reloj de otro similar, se obtiene un gráfico en bloque como el de la Fig. 2-17 y sus señales serán las de la Fig. 2-18.

Fig. 2-17 Diagrama bloque del acoplamiento del circuito Astable con los Flip-Flops.

Fig. 2-18 Señales de salida de cada uno de los circuitos de la - Fig. 2-17.

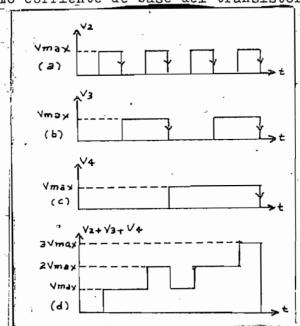

Si se suman los voltajes V2; V3 y V4 como función del -tiempo, la respuesta es la grafizada en la Fig. 2-19, en la que

se observa que si Vmax = 1, se hace imperante multiplicar a V3 por 2; a V4 por 4 y sumando a estas con V2, se obtiene la res --

.puesta grafizada en la Fig. 2-20, con lo cual se ha logrado cum-.

plir con la necesidad de obtener una corriente tipo escalera para ser usada como corriente de base del transistor de prueba.

Fig. 2-19 (a) Señal del F.F.1; (b) señal del F.F.2; (c) señal -- del F.F.3; (d) suma de las señales de los 3 F.Fs. en el tiempo.

Fig. 2-20 (a) señal del F.F.1; (b) señal del F.F.2 x 2; (c) señal del F.F.3 x 4; (d) suma de las señales del sistema compuesto porlos tres F.Fs.

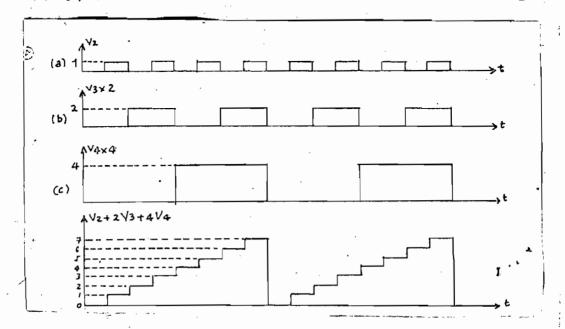

Par sumar V2 + V3x2 + V4x4, es necesario disponer de un circuito que realice tal operación; este elemento es un amplificador operacional que sea usado como sumador cuya representación se ilustra en la Fig.2-21 y que cumple con la Ec.(2-3).

$$\frac{\text{Vin}}{\text{Vout}} = -\frac{\Re 1}{\Re 0} \qquad \text{Vout} = -\text{VinxRo/R1} \qquad (2-3)$$

Si R1 =

$$\frac{\text{Ro}}{2}$$

entonces Vout = - 2Vin.

Consecuentemente, el voltaje o señal de entrada ha sido - invertido y multiplicado por dos.

Si R1 =

$$\frac{R0}{4}$$

entonces Vout = -4Vin.

En este caso, las señales de entrada han sido invertidas y multiplicadas por dos y cuatro respectivamente, realizándose la suma del modo que se indica en la Fig.2-22, en la que se cumple con la siguiente ecuación.

$$Vout = -(V2 + 2V3 + 4V4)$$

Siendo V2 la señal de la Fig.2-19a, V3 la señal de la Fig.2-19b, y V4 la de la Fig.2-19c, la salida Vout, será como aquella de la Fig.2-20d pero invertida.

El diagrama bloque de este generador de tensión tipo es-

calera es el de la Fig. 2-23, cumpliéndose de este modo con el diseño en bloque del generador, restando el diseño en bloque del generador de onda triangular para barrido horizontal.

Fig. 2-21 (a) Representación de un amplificador operacional; (b) Amplificador operacional usado como sumador y multiplicador inversor.

Fig 2-22 Amplificador operacional usado como sumador y multiplicador de señales.

Fig. 2-23 Diagrama bloque de un generador de tensión tipo escalera.

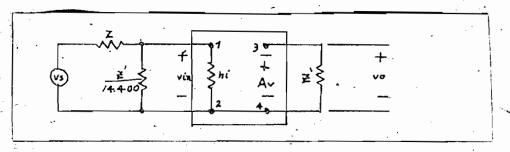

# C .- DIAGRAMA BLOQUE DE UN GENERADOR DE ONDA TRIANGULAR.

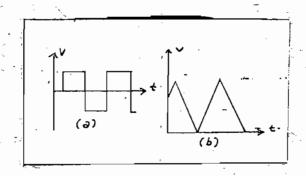

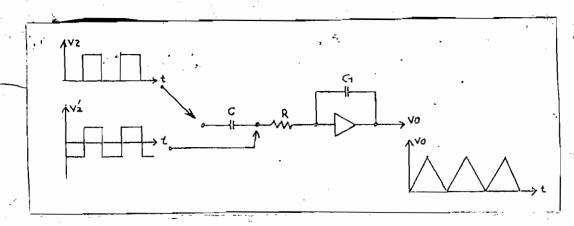

El punto de partida para cumplir con este diseño, es el hecho que, al integrarauna onda de tensión rectangular, matemá ticamente se obtiene una onda triangular, de cuyo diagrama blo que nos ocuparemos a continuación.

La Fig. 2-24a y b; muestra las ondar rectangular y triangular respectivamente. Si la integración de la onda de la Fig. - 2-24a, es la de la Fig. 2-24b, se necesita conocer que tipo de - circuito electrónico realiza tal labor, y, esta designación lo - cumple el amplificador operacional usado como integrador, cuya - representación en bloque es aquella de la Fig. 2-25 y responde - a la ecuación integral definida como Ec.(2-4) que se estudiará - en el capítulo III literal a-3.

Fig. 2-24 (a) Tensión rectangular; (b) Integración de la tensión rectangular.

$$\frac{\text{Vout.}}{\text{Vin.}} = \frac{-1}{\text{Rc}} \int i \, dt. \qquad (2-4)$$

En consecuencia si Vin. es la onda de tensión de la Fig.

2-24a, la salida Vout. tendrá la forma de aquella de la Fig. 2-24b con lo cual se ha cumplido con otro requerimiento, restando únicamente determinar el lugar de donde se obtendrá la señal de entrada al integrador, puesto que, ésta al ser integrada, debe ser sincronizada con aquella tensión tipo escalera del modo siguiente Fig. 2-26.

Fig. 2-25 Representación gráfica de un integrador.

Fig. 2-26 Sincronismo entre (a) la tensión tipo escalera y (b) la tensión rectangular.

Como se observa en la Fig. 2-26, es necerio integrar una - tensión de tipo de onda rectangular cuyo semiperíodo tenga una -- duración T como se indica en la Fig. 2-26a, obteniéndose la ten-- sión tipo triangular Fig. 2-27.

Fig. 2-27 (a) Tensión de onda rectangular; (b) Integración de la onda rectangular.

Analisando la Fig. 2-20, se deduce que la tensión que cum ple dicha condición es la de la Fig. 2-20a, que se lo obtiene de la salida del F.F.1 Fig. 2-17 y su salida se encuentra representada como V2 en la Fig. 2-18, siendo imprescindible hacerla pasar a través de un condensador "C" Fig. 2-28 de un valor relativamente grande con el propósito de eliminar la parte de D.C. y obtener la forma de onda ilustrada en la Fig. 2-27a. Consecuente mente el diagrama bloque parcial de obtener la tensión tipo triangular, es el de la Fig. 2-29.

A menudo, uno de los problemas del diseño, es el control de

la corriente de base y de colector, en este trabajo, dicho inconveniente se obvia con el uso de un sistema de resistencias en la base, para evitar que las características que se observen en el osciloscopio del transistor que se está probando, aparezcan solo en la región de corte o solo en la de saturación.

Fig. 2-28 Modo de eliminar la parte de DC. de V2 para transformarla en V2 la que está en condiciones de ser integrada.

Fig. 2-29 Diagrama bloque parcial con el que se obtendrá una tensión tipo triangular.

Un sistema de resistencias o un potenciómetro en el colector del transistor de prueba, limitará la corriente de dicho elemento y se observará las diferentes líneas de carga, así como también se evitará que el transistor en la región de líneas de corriente de base constante superiores, llegue a regiones de rup

tura. Lo anotado anteriormente, se representa en forma gráfica - del modo siguiente Fig. 2-30:

Fig. 2-30-(a) Representación gráfica de un sistema de resisten - cias; (b) Forma de controlar la corriente de base y de limitar - la de colector.

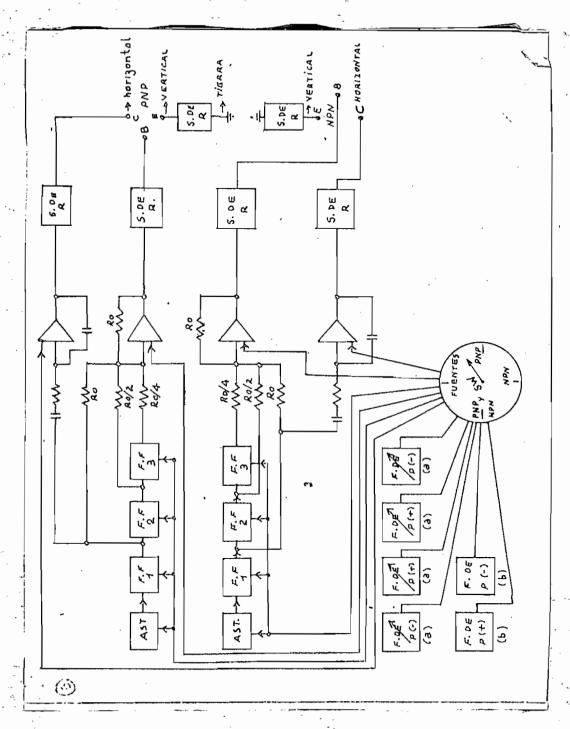

De todo lo hasta el momento expuesto, se concluye que con el gráfico ilustrado en la Fig. 2-31, se puede obtener las carac terísticas de transistores PNP o NPN en emisor común, siendo ésta una representación en bloque total del equipo a diseñarse. La misma figura muestra un sistema de switches para poder seleccionar el tipo de transistor a ser probado, con el objeto de polarizar los elementos activos constitutivos de los diferentes circuitos electrónicos.

Fig. 2-31 Diagrama bloque total del equipo a construirse, donde - los cuadros que están junto a la (a), representan fuentes de poder de tensión variable y los que están junto a la (b) fuentes de poder de tensión fija. El switche SW. selecciona el tipo de transistor a ser probado siendo PNP o NPN o los dos tipos simultáneamente, además de que posee una posición adicional que permite u sar las fuentes del equipo para uso exterior almismo.

CAPITULO TERCERO

DISEÑO CIRCUITAL

### DISEÑO CIRCUITAL

Este capítulo se ocupa del diseño circuital y numérico del equipo a ser construido, así como también las consideraciones o simplificaciones que se permiten hacer al transcurso del mismo,—con el objeto de que no sea tedioso matemáticamente, sino de —cierta utilidad práctica. Se observará que a medida que se re—quiera, se hace uso de ciertas constantes que muchos libros las—consideran prácticas y que serán dadas a conocer con oportunidad.

#### A.- DISEÑO DEL GENERADOR DE TENSION TIPO ESCALERA

Del análisis realizado en el capítulo II literal B, se -llegó a concluir que el circuito en bloque generador de una tensión tipo escalera, es aquel de la Fig. 2-22 constituido de un multivibrador Astable; tres Flip-Flops y un amplificador opera cional usado como sumador multiplicador de cuyo diseño nos ocupa

remos.

### a.- 1 DISEÑO DEL CIRCUITO DE DISPARO

A menudo se considera que la señal proveniente de un os - cilador de onda cuadrada o multivibrador Astable, puede ser usa- da para que a través de un circuito de disparo, controle el tra-bajo de los F.Fs., constituyéndose de este modo en la señal de reloj del conjunto. El circuito Astable posee dos estados semi-

estables, en los cuales sin necesidad de una señal de disparo exterior, el circuito pasará sucesivamente de un estado semiesta - ble al otro, consecuentemente, el circuito Astable no es sino un acoplamiento de dos etapas de amplificación de tal manera que se obtengan dos estados semiestables.

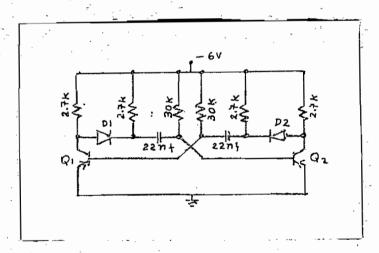

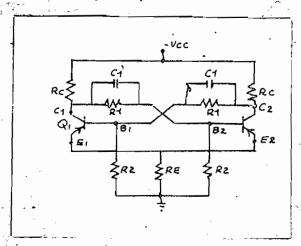

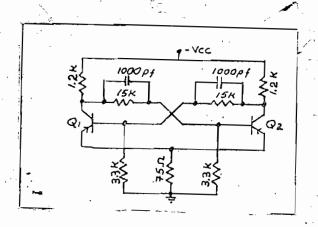

## a. - 2 MILTIVIBRADOR ASTABLE ACCPLADO POR COLECTOR

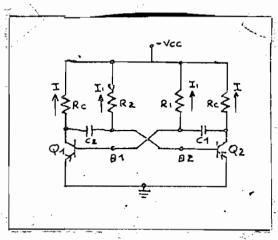

La Fig. 3-1 ilustra la forma de un miltiwibrador (MV) Astable acoplado por colector. Debido a que existe un acoplamiento por capacidad entre etapas, ningún transistor puede permane cer cortado permanentemente y por el contrario tendrá dos esta dos semiestables realizando transiciones periódicas entre los -mismos.

Fig. 3-1 Multivibrador Astable acoplado por Colector.

Su finalidad y su funcionamiento en el diseño son los siguientes:

Si se supone que inmediatamente antes del instante t = 0,

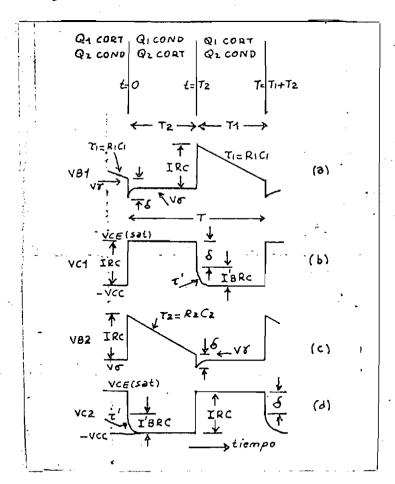

el transistor Q1 se encuentra en saturación con una corriente de colector I, y Q2 está cortado, a un tiempo t<0, se podrá observar las diferentes tensiones del circuito en la Fig. 3-2, donde C1 se carga a través de R1 y cae exponencialmente hacia -Vcc. -Para t = 0. la base B1 alcanza la tensión de armanque VY v 01 conduce. Al ir Q1 hacia la saturación, Tc1 sube el escalón IRc hasta el valor VCE(sat) como se observa en la Fig. 3-2b. El sal to en Vc1, ocaciona otro similar, IRc en VB2, puesto que ambos están acoplados por capacidad, lo que cortará a Q2 y la tensión de su colector cae a -Vcc. Esta caida en Vc2, se acopla mediante el condensador C1 a la base de Q1, ocacionando el subpulso  $\delta$  en VB1 Fig. 3-2a y la caida brusca en Vc2 de la misma magnitud Estando la corriente de base I'b en el subrepulso, las ondas en la base de Q1 y el colector de Q2 varian exponencialmente con la constante de tiempo  $\mathcal{T}' = (Rc + rbb!)C1$  hacia los valores  $V \sigma y$ -Vcc respectivamente. Para t = 0+, la tensión VB2 es IRc + V6. decreciendo exponencialmente con una constante de tiempo 72 =R2C2 hacia -Vcc y al tiempo t = T2, la tensión en B2, alcanza el valor de arranque V7 originándose una transición inversa.

V 6 = VBE( saturación ).

De la Fig. 3-3 se puede determinar la corriente de colector Ic que tendrán los transistores cuando el uno esté en corte y el otro en saturación y será:

$$Ic = \frac{Vcc - VCE(sat)}{Rc}$$

(3-1)

La tabla 3-1 puede resultar de utilidad práctica cuando -, se requiere de diseños sin mucha precisión como es el caso que - nos ocupa.

| VCE(sat)   | VBE(sat)=V | VBE(activa) | VBE(arranque) | VBE(corte)  |

|------------|------------|-------------|---------------|-------------|

| 0.3<br>0.1 | 0.7        | 0.6         | 0.5<br>0.1    | 0.0<br>-0.1 |

Tabla 3-1 Valores de tensión típicos en las uniones de un transistor NPN a 25 C.

Fig 3-2 Ondas en el MV  $A^S$ table acoplado por colector de la Fig. 3-1 usando transistores PNP. Para t=0-, la primera etapa Q1, eatá cortada y la segunda Q2 conduce.

### a.- 3 TIEMPO DE CADA PARTE DE UN CICLO.

El tiempo de cada parte de un ciclo se lo puede encontrar del modo siguiente:

De la Fig.3-2a y b, se deduce que T es aproximadamente - definido por:

$$T = T1 + T2 = 0.69(R1C1 + R2C2)$$

(3-2)

y para un circuito simétrico en el que R1 = R2=R y C1 = C2 = C

$$T = 1.38RC$$

(3-3)

La frecuencia de oscilación se puede variar desde ciclos a megaciclos ajustando R o C. Si se observa la Fig.3-2 se nota rá que aparece un fenómeno transitorio con constante de tiempo  $\mathcal{T}'$ , asociado a las ondas de un transistor cuando a este se lo lleva a la saturación, pues cada onda de colector tiene una esquina redondeada debido al tiempo que necesita este fenómeno para desaparecer, denominado tiempo de recuperación o  $\mathcal{T}$ , el que puede constituirse en una fracción apreciable de la mitad del período  $\mathcal{T}/2$  como vamos a ver, asumiendo que el elemento en discusión es un MV simétrico.

$$tr = 2.2t' = 2.2(Rc + rbb')C \approx 2.2RcxC$$

puesto que  $T/2 = 0.69RC$  se tiene:

$\frac{tr}{T/2} = \frac{2.2Rc}{0.69R} = 3.2Rc/R$  (3-4)

Si Rc = 1.35K

$$\Omega$$

y R = 30K $\Omega$  entonces

$$\frac{tr}{T/2} = 3.2 \times \frac{1.35}{30} \times 100 = 14.4\%$$

que será una honda no muy cuadrada como aquella de la Fig. 3-2b la que será usada como señal de disparo.

Despreciando los potenciales de saturación, especialmente cuando el voltaje de polarización es grande comparado con dichos potenciales, se puede afirmar que para transistores en saturación se cumplen las siguientes aproximaciones:

Ic

$$\approx \frac{\text{Vcc}}{\text{Rc}}$$

e IB  $\approx \frac{\text{Vcc}}{\text{R}}$

Para asegurar la saturación debe cumplirse que IB $\gamma$ Ic/h $_{

m FE}$ por consiguiente R $\lesssim$ h $_{

m FE}$ Rc. Para el caso que nos ocupa tenemos

$$30Kn < 40 \times 1.35Kn = 54Kn$$

puesto que  $h_{\rm FE} = 40$  para el transistor que se usará ( 30404 PNP )

$$\frac{\ell r}{T/2} = \frac{3.2 \text{ x}}{R} \gg \frac{3.2}{h_{\text{FE}}}$$

resultando  $14.4\% > \frac{3.2}{40} \text{ x}$  100= 8

en consecuencia hemos cumplido con los requerimientos del diseño para este ejemplo.

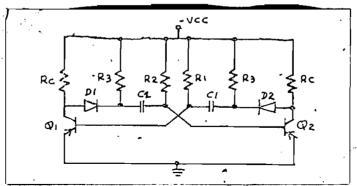

Pero como nuestro deseo es tener una onda cuadrada bastante aceptable, se diseña la configuración de la Fig. 3-3, en la que la adición de los diodos D1 y D2 y de la resistencia R3 al - MB acoplado por colector de la Fig.3-1, produce una onda en el colector con flancos verticales.

Fig. 3-3 Multivibrador Astable usando diodos para obtener una on da cuadrada con flancos verticales.

# a.- 4 DISEÑO DEL MULTIVIBRADOR ASTABLE

Para diseñar el multivibrador astable de la Fig.3-4, es necesario tener en cuenta las siguientes consideraciones: Usando

los valores dados en la tabla 3-1, y sabiendo que el transistor

a ser usado es el 3C404 cuyas características son muy similares

a las del 2N404 del que se conocen los siguientes datos:

| MAXIMOS                             |                                      | FUGAS GANAN                             |  | GANANCIA                          |

|-------------------------------------|--------------------------------------|-----------------------------------------|--|-----------------------------------|

| VCB = 25v<br>VCE = 24v<br>VBE = 12v | Ic = 200mA<br>Pt = 150mW<br>Tc = 100 | $I_{CBO} = 5 \mathcal{M} A$ $VCB = 12v$ |  | = $40 = \beta$ cuando<br>= $24mA$ |

Asumimos que Q1 está cortado; Q2 conduce y que R2 = R1 además de que C1 = C2

1.- Se limita la corriente del transisstor Q2 que conduce además de que en el momento de saturación VCE(sat) =

-0.1v. Bajo estas circunstancias D2 conduce y tiene - una resistencia directa de aproximadamente 300Ω en -

serie con R3 y estos a su vez en paralelo con Rc.

2.- Se asume una corriente de saturación de -4.4mA y Vcc = -6v; consecuentemente:

$$-4.4\text{mA} = \frac{-6\text{v} - \text{VCE(sat)}}{R}$$

luego,  $R = \frac{-5.9\text{v}}{-4.4\text{mA}} = 1.35\text{KA}$

donde

$$R = Rc//(R3 + Rd)$$

/// = Paralelo

Rd = Resistencia directa del diodo.

$$Si R3 + Rd = Rc$$

entonces,

$$R = \frac{Rc \times Rc}{2Rc}$$

y  $Rc = 2.7K\Omega$

$$R3 = Rc - Rd = 2.4K$$

Pero para el diseño práctico, se usa R3 = Rc y las condiciones no varian mayormente, tomando en cuenta la tolerancia de los elementos resistivos.

3.- Para asegurar la saturación, debe cumplirse que

$$IB \gg \frac{Ic}{H_{FE}}$$

; para este caso,

$$R2 = \frac{-6v - VBE(sat)}{IB} = \frac{-5.7v}{IB}$$

IB>

$$\frac{4.4\text{mA}}{\text{H}_{\text{FE}}} = \frac{4.4\text{mA}}{40} = 110\text{MA}$$

pudiéndose asumir IB=190MA

con lo cual

$$R2 = \frac{-5.7v}{-190 \text{M A}} = 30 \text{K}\Omega$$

4.- Puesto que R1 = R2 y C1 = C2

T = 1.38R1C1.

En este caso, se debe asumir una frecuencia tal que -las líneas características de los transistores a ser -probados, puedan ser vistas en el osciloscopio siendo

suficiente una frecuencia de 1.100 ciclos

$$\frac{1}{T} = \frac{f}{1} = 1.100 = \frac{1}{1,38R1C1}$$

; de donde

$C1 = \frac{1}{1.38R1 \times 1.100} = 22.000 \text{ pf.}$

En consecuencia el Astable diseñado es el de la Fig. - 3-4 y deberá cumplir con las especificaciones del di - seño.

Fig. 3-4 Astable diseñado y que será usado en este trabajo.

Los diodos D1 y  $^{\mathrm{D}2}$  son de señal o baja corriente cuyas es pecificaciones no se conocen.

### å.- 5 DISEÑO DE LOS MULTIVIBRADORES BIESTABLES CON TRANSISTORES.

Un multivibrador biestable (MVB) es aquel que puede per manecer indefinidamente en cualquiera de sus dos estados estables

(corte o saturación) y que pueda pasar de un estado al otro me diante una exitación exterior. Este circuito es usado como conta

dor de escala dos para almacenar información binaria y como gene

rador de ondas de pulsos. No solo se lo conoce como MVB sino como F.F., circuito Eccles-Jordan, circuito disparador, circuito contador de escala dos y binario.

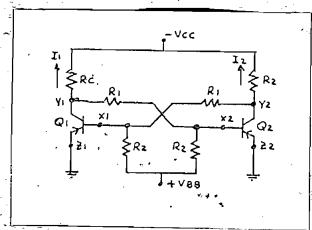

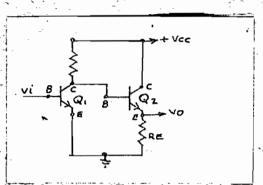

Un F.F. común es aquel de la Fig. 3-5, en el que la salida de cada amplificador está acoplado directamente a la entrada del otro.

Fig. 3-5 Flip-Flop de transistores PNP con polarización fija.

Se dice que un transistor está en corte o abierto, cortado o apagado, si está polarizado por debajo del corte y su co rriente no existe o es tan pequeña que se puede afirmar que no conduce; y está saturado, prendido o cerrado cuando conduce; lue

go para que un F.F. esté en su estado estable, será necesario -que: o bien uno de los elementos activos esté cortado o bien que

uno esté saturado.

1

En la práctica es aconsejable diseñar estos F.F. usando - componentes cuya tolerancia no sea mayor que el 10% y tener la - seguridad de que seguirá trabajando aún cuando la fuente de alimentación o la temperatura ambiente tuvieran cambios razonables; por esta razón el F.F. se diseña de tal modo que en su estado estable, el un elemento activo esté muy por debajo del corte y el otro en fijación o saturación.

#### a. - 6 CLASIFICACION DE LOS FLIP-FLOPS

De acuerdo al tipo de polarización, los F.Fs. se dividen en: F.F. de polarización fija Fig. 3-5 y autopolarizados Fig.3-6. Para este trabajo se escoge el F.F. autopolarizado porque representa una ventaja económica al prescindir de una de las fuentes de polarización usando la resistencia común de emisor R3 que suministra autopolarización.

Fig. 3-6 Binario autopolarizado.

### a.- 7 CONSIDERACIONES PRACTICAS DE DISEÑO

Analizando el circuito de la Fig. 3-6 se concluye que, en el caso de que R3 sea una resistencia bastante pequeña en comparación con Rc, casi toda la tensión de alimentación -Vcc aparece rá en los bornes del transistor que está cortado es decir VCE z -Vcc; debiéndose tener en cuenta que -Vcc debe ser menor que el voltaje de ruptura de colector BVCE, lo cual limitará el valor de -Vcc. En condiciones de saturación, logramos obtener la corriente máxima de colector y tomando en cuenta que R3 Rc, el valor máximo de dicha corriente, se lo puede aproximar por la Ec. (3-5).

$$-Vcc = -Ic (Rc + R3) - VCE(sat)-IRR3$$

Asumiendo que VCE(sat) es pequeño en relación a Vcc tenemos:

+Vcc = Ic(Rc + R3) - IB.R3.como IB =

$$\frac{Ic}{h_{FE}}$$

, se lo puede

despreciar en relación a Ic al igual que R3, pues R3 KRc y queda

$$Ic \approx \frac{Vcc^{-2}}{Rc}$$

(3-5)

en el cual debemos notar que el valor de Ic no exceda al máximo - admisible por el transistor. En consecuencia lo que limita la -

corriente del mismo es Rc. Los valores de R1 y R2 deben ser elegidos de modo que en uno de los dos estados estables, la corriente de base sea suficiente para llevar al transistor a saturación mientras que en el otro estado, la unión de emisor está por debajo del corte.

Réspecto a la señal de salida de uno de los colectores, - (VWO), esta es la variación de la tensión resultante de la transición del F.F. del, un estado al otro del modo indicado por la - Ec. (3-6).

$$VWO = Vc1 - Vc2$$

(3-6)

Cuando se tiene el caso de la Fig.3-6, en el que se asume que R1 tiene un efecto de carga despreciable, se considera con gran aproximación que VWO & Vcc, resultando de suma utilidad el que el voltaje de salida sea independiente de Rc.

Tratandose del uso de transistores como Switches, los fabricantes dan curvas de ciertos parámetros que únicamente los en nunciaré por no ser considerados muy prácticos, tales curvas son: Corriente inversa saturada o de saturación ICBo como función de la temperatura; here como función de la corriente de colector Ic; tensión de saturación VCE(sat) como función de Ic y de IB; así como también la influencia de la temperatura en los parámetros de saturación. Para diseñar los F.Fs. a transistores, son suficientes los siguientes parámetros:

ICBo; H<sub>FE</sub>; VCE(sat) y VBE(sat)

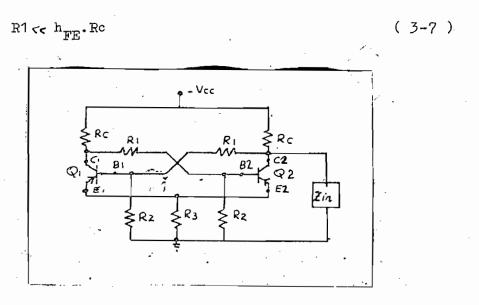

Como los F.Fs. de este trabajo serán usados para alimentar otros circuitos, a uno de los colectores se les aplicará una carga que para este caso es la impedancia de entrada del siguientes—circuito mostrado como Zin en la Fig.3-7. Estas cargas deben ser tomadas muy en cuenta porque reducen la tensión del colector Vc2 asumiendo que está cortado y en consecuencia disminuye la tensión de salida. Lo más grave es que Vc2 disminuya tanto que la corriente IB2 no sea suficiente para llevar al transistor Q1 a la satura ción, por esta razón los componentes de un F.F. deben elegirse de modo que en las condiciones más severas de carga, uno de los transistores está en saturación mientras el otro está cortado.

Orientando nuestra atención a la Fig.3-7, se nota que no - solo Zin es la carga del circuito sino que también lo es R1, por esta razón, se usa un valor de R1 bastante grande comparado con - Rc de modo que se cumpla la Ec.(3-7).

Fig. 3-7. Circuito F.F. con carga.

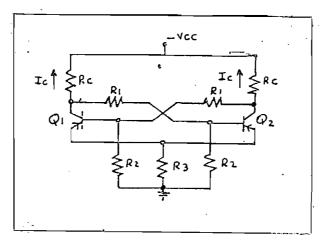

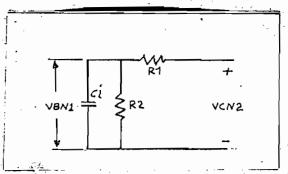

# a.- 8 DETERMINACION DE LOS ESTADOS ESTABLES DE UN FLIP-FLOP

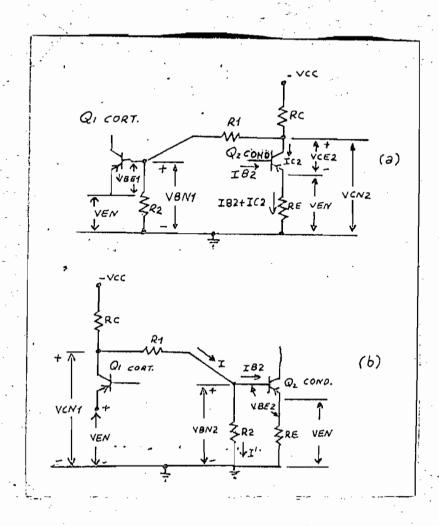

Para realizar este estudio y tomando como tema al circuito de la Fig. 3-6, no está por demás anotar que partiremos de la suposición de que Q1 está cortado y Q2 saturado, para lo cual analicemos las conexiones de la base de Q1 con el colector de Q2 y viceversa mostrado en la Fig. 3-8a y b respectivamente.

$$VEN = (IB2 + Ic2)RE \qquad VBE1 = VBN1 - VEN$$

$$VCN2 = VCE + VEN \qquad VBN2 = VBE2 + VEN$$

$$VCN1 = \frac{-Vcc.R1}{Rc+R1} + \frac{VBN2.Rc}{Rc+R1}$$

$$VBN1 = \frac{R2.VCN2}{R1+R2}$$

Puesto que se pretende trabajar con valores característicos promedios de los transistores; con resistencias cuya toleran

cia sea el 10% y sabiendo que los niveles de voltaje de un F.F.

muy pocas veces necesitan ser conocidos con gran precisión, se

puede hacer uso de los valores especificados en la tabla (3-1).

Para terminar el análisis, es necesario determinar las corrientes de saturación, para lo que debemos observar la Fig, 3-6 en la que se determina el circuito equivalente para localizar a Q2 mostrado en la Fig. 3-9, en la que se ha sustituido el circuito de colector de Q2 de la Fig. 3-8a por su equivalente de Thé venin del modo siguiente:

$$Vcq = \frac{-Vcc (R1 + R2)}{R1 + R2 + Rc}$$

(3-9)

Fig. 3-8 Conexiones entre la base de Q1 y el colector de Q2 y viceversa para uno de los estados estables.

Fig. 3-9 Circuito equivalente de base y colector para el caso - en que Q2 está cortado .

Vcq = voltaje equivalente en el Colector.

Req1 = Resistencia equivalente en el Colector.

$$Req1 = \frac{Rc(R1 + R2)}{R1 + R2 + Rc}$$

(3-10)

De una manera similar se determina el equivalente de la -

$$VBq = \frac{-Vcc.R2}{R1 + R2 + Rc}$$

(3-11)

En serie con la resistencia.

$$Req2 = \frac{R2(R1 + Rc)}{R1 + R2 + Rc}$$

(3-12)

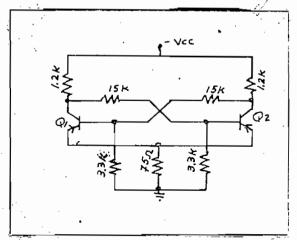

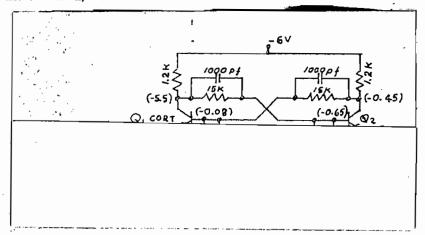

# a.- 9 DISEÑO NUMERICO DE UN FLIP-FLOP

Sabiendo que el transistor a ser usado es el 30404 PNP de Germanio, se anotó en el literal (a.- 4) de este capítulo sus características con lo cual analizando el circuito de la Fig. 3-6 se procede del modo siguiente:

De la Ec. 3-5 y asumiendo que Vcc = -6v e Ic = -5mA. se determina el valor de Rc.

$$Ic = Vcc / Rc \qquad Rc = \frac{6v}{5mA} = 1.2K n$$

Debido a que la condición para hacer uso de la Ec.(3-5)es que RE < Rc, se asume que RE = 75

De la relación o Ec. (3-6) se tiene que

R1≪h<sub>RE</sub>•Rc

si  $h_{FE} = 40$ , entonces R1</br><br/>40x1.2K $\Omega$  = 48K $\Omega$

pudiendo asumir R1 =  $15 \mathrm{K}\Omega$ , considerando la carga que va a so portar cada F.F. y asegurando de este modo el normal trabajo de los mismos bajo condiciones severas de carga. De la relación:

IB2 =

$$\frac{-1c}{3}$$

=  $-5mA$  /40 =  $-0.125mA$  =  $-125\mu$ A

haciendo uso de las ecuaciones (3-8) se tiene:

VEN2 = RE(Ic2 + IB2) =

$$75(-5 - 0.125)v = -0.384v$$

.

VBE2(sat) =  $-0.3v$

VBN2 = VBE2 + VEN2' =  $(-0.384 - 0.3)v = -0.684v$

De la Fig. 3-8b se observa que:

$$I = \frac{-Vcc - VBN2}{Rc + R1} = \frac{(-6 + 0.684)v}{(1.2 + 15)K\Omega} = -0.33mA$$

$$I = I' + IB2 \qquad I' = -0.33 + 0.125 = 0.205mA$$

$$luego R2 = \frac{VBN2}{I'} = + 0.684v/0.205mA = 3.340 \Omega.$$

Como este valor de resistencia no existe en el mercado se

usa el más próximo que es el de R2 = 3.3Kn y el circuito resultante es el de la Fig. 3-10.

Fig. 3-10 Circuito F.F. a ser usado en la parte práctica de este trabajo.

Las tensiones de corte y saturación calculadas, son las - que resulten de resolver las Ecs. (3-8).

VEN2 = (IB2 + Ic2)RE =

$$-384mv$$

VCN2 = VCE2(sat) + VEN2 =  $-0.1 - 0.384 = -0.484v$

VBN2 = VBE(sat)2 + VEN =  $-0.3 - 0.384 = -0.684v$

VBN1 =  $\frac{VCN2.R2}{R1 + R2} = -\frac{0.484 \times 3.3}{15 + 3.3} = +0.0875v$

VBE1 = VBN1 - VEN =  $-0.0875 + 0.384 = +0.2965v$

como VBE1 es el voltaje de corte y este valor es de +0.1 según - la tabla (3-1), se concluye que Q1 efectivamente está cortado.

$$VCN1 = \frac{-Vcc.R1}{R1 + Rc} + \frac{VBN2.Rc}{Rc + R1} = -\frac{6 \times 15}{15 + 1.2}v + 0.684x\frac{1.2}{15 + 1.2}v$$

$$= -5.48v.$$

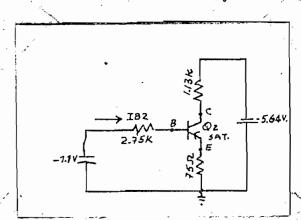

Una manera más exacta de resolver el mismo problema, es -- usando el circuito de la Fig. 3-9 con los valores obtenidos para la Fig. 3-10.

De la Ec.(3-9)

$$Vcq = -5.64v$$

De la Ec.(3-10)  $Req1 = 1.13Kn$

De la Ec.(3-11)  $VBq = -1.1v$

De la Ec.(3-12)  $Req2 = 2.75Kn$

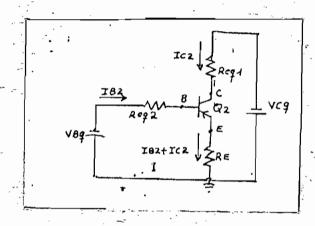

resultando el circuito equivalente de la Fig. 3-11, del cual se determina los valores de saturación de Q2.

Fig. 3-11 Circuito equivalente para determinar los valores de - saturación de Q2.

Despejando Ic2 y sabiendo que VCE(sat) = -0.1v se tiene:

Ic2 = 4.6mA

VEN2 = RE(Ic2 + IB2) = -75n (137 + 4.600) MA = -0.356v

VBE(sat) = -0.3v

PRIMER DISEÑO

VBN2 = VBE(sat) + VEN2 = -0.656v

VCN2 = VCE(sat) + VEN2 = -0.1 - 0.356 = -0.456v

VBN1 = VCN2.R2/(R1 + R2) = -0.0822v

VBE1 = VBN1 - VEN = -0.0822 + 0.356 = +0.2738v

como VBE1 = VBE1 de corte y este valor es de +0.1v se concluye que el transistor Q1 está efectivamente cortado.

$$VCN1 = \frac{-Vcc.R1}{R1 + Rc} + \frac{VBN2.Rc}{Rc + R1} = -5.5v$$

Comparando los valores obtenidos en el primer diseño con aquellos del segundo se tiene que el estado estable toma los valores siguientes:

SEGUNDO DISEÑO

#

$$Ic2 = 5mA$$

$Ic2 = -4.6mA$

$$IB2 = -125\mu_A$$

$IB2 = -137\mu_A$

VCN2 = -0.484v

VCN2 = -0.456v

VBN2 = -0.684v

VBN2 = -0.656v

VEN = -0.384v

VEN = -6.356v

VWO = VCN2 - VCN1 = -5v VWO = VCN2 - VCN1 = -5.044v

Como se podrá observar en los valores anteriores, tanto con el primer procedimiento como con el segundo, los valores son muv aproximados y con estos deberíamos ir a las curvas que pro porciona el fabricante para determinar con precisión los valores de VBE(sat) y VCE(sat) para las respectivas corrientes Ic2 e IB2 y repetir los cálculos anteriores; pero como esto para el presen te trabajo no lo necesitamos, se prescinde de este paso, además de que debido a que se trabaja con características medias. no se justifica una aproximación adicional.

Adoptemos como tema de estudio la resistencia RE y en ella se puede afirmar que la caida de tensión, es nominalmente la mis ma para ambos estados estables, sin embargo, durante la transi ción de estados la corriente IE no es la misma sino que tiene -una variación 🕰 IE y para mantener VEN casi constante durante el tiempo de transición, es necesario poner un condensador en paralelo con RE de tal modo que, durante el tiempo de transición, la variación de voltaje en este paralelo sea pequeña comparado con Los estados estables NO QUEDAN AFECTADOS por la presencia de dicho condensador y por consiguiente no será usado en este -trabajo, aunque la facilidad de provocar una transición entre es tados y la rapidez con que el F.F. se acomoda a su nuevo estado,

-puede resultar perjudicada si se omite este condensador, especial mente en frecuencias altas que no es tema de estudio.

Un F.F. permanece en uno de sus estados estables hasta — que una señal de disparo proveniente de una fuente exterior, provoque una transición y en muchos casos, es necesario que el cambio sea tan rápido como sea posible después de la aplicación de la señal de disparo; por lo cual es preciso definir los siguientes términos a ser usados:

Tiempo de Transición: Es el intervalo durante el cual se transfiere la conducción de uno a otro transistor.

Tiempo de Resolución: Es el menor intervalo posible entre dos disparos y su inversa es la má xima frecuencia a la que puede responder el F.F.

Tiempo de Establecimiento o Acomodación: Es el tiempo adicional requerido para completar la recarga de los condensadores des pués de la transferencia de conducción.

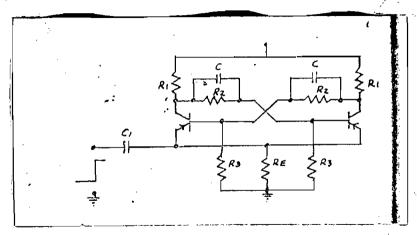

El tiempo de transición puede reducirse conectando pequeñas capacidades en paralelo con las resistencias R1 de acopla miento del F.F., y, son usadas para ayudar al binario a realizar transiciones bruscas entre estados, siendo por este motivo denominadas condensadores de transición conmutación o aceleración y su conexión se ilustra en la Fig. 3-12.

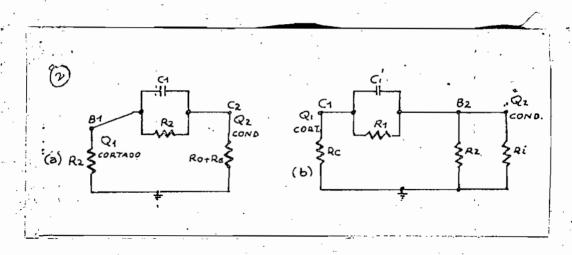

a.- 10 INTRODUCCION A LOS CONDENSADORES DE ACELERACION O CONMU-TACION.

Ē.

En la Fig. 3-12 se supone que Q2 conduce y Q1 esta corta-

do, al aplicar un escalón positivo a la base B2, el punto C2 bajará rápidamente de voltaje a un valor aproximado a -Vcc, siendo nuestro deseo que esta disminución se transmita con el mínimo retardo a B1; el circuito de entrada del transistor Q1 tiene una - capacidad Ci y en ausencia de C1, el circuito formado por R1; R2 y Ci tiene la configuración atenuadora de la Fig. 3-13, lográndose desvirtuar esta configuración haciendo uso del condensador C1,

Fig. 3-12 Circuito completo de un F.F. autopolarizado.

Fig. 3-13 Atenuador.

En otras palabras, lo que se ha logrado al colocar el condensador C1 es aumentar la velocidad con la que crece VBN1.

Cuando se dispara el circuito de modo que Q1 conduce y Q2 pasa a corte, existe un intercambio de tensiones en los condensado

res y el F.F. no se habrá acomodado a su nuevo estado hasta que esta transición o intercambio de tensiones en los condensadores haya terminado.

Los circuitos equivalentes para calcular la constante de tiempo  $\mathcal{T}$  asociado con la energía o recarga de C1 es el dado en la Fig.3-14a, cuando Q2 conduce y si la impedancia de salida de Q2 es Ro + RE incluido Rc, la constante de tiempo es

$$\tau = \text{C1.R}$$

siendo  $R = \frac{(\text{Ro} + \text{R2} + \text{RE})\text{R1}}{\text{R1} + \text{R2} + \text{RE} + \text{R0}}$

donde Ro es la impedancia de la juntura Colector Emisor cuando - el transistor está en saturación y (Ro + RE)//Rc  $\approx$  Ro + RE.

En un transistor saturado Ro + RE es muy pequeño en comparación con R2 pudiéndose de una manera análoga a la de la Fig. - 3-14b, hallar la constante de tiempo  $\tau'$  asociada con la recarga - de C1' en la que Ri es la resistencia de entrada de Q2 y

$$\tau = C1'R'$$

siendo  $R' = R1//(Rc + R2//Ri)$

Puesto que (Rc + R2//Ri) es generalmente menor que R1 o - R2, será  $\tau > \tau'$  y la mayor de ambas constantes de tiempo es

$$\tau = R.C1$$

$\frac{R1.R2.C1}{R1 + R2}$  (3-13)

donde C1 = C1' representan la capacidad de conmutación y Ri = hi  $+ (\beta + 1)$ RE.

Fig. 3-14 Circuitos equivalentes para calcular las constantes - de tiempo de los condensadores de conmutación.

Prácticamente se ha podido observar que los condensadores de conmutación de los F.Fs. adquieren valores dedde 50 a 500pf - asegurando el disparo de los mismos, con esto no se cierra el paso a que adquieran valores más elevados.

Es de suponer que si se guarda un tiempo 27 entre disparos, los fenómenos transitorios habrán decaido lo suficiente como para poder disparar con seguridad al F.F. También es de suponerse que 1/27 será la frecuencia máxima de funcionamiento dada

por:

fmax =

$$\frac{1}{2.7}$$

=  $\frac{R1 + R2}{201.R1.R2}$  (3-14)

Si C1 = 1000pf R1 = 15K $\Omega$  y R2 = 3.3K $\Omega$  tenemos:

fmax =  $\frac{15 + 3.3}{2 \times 15 \times 3.3}$  10<sup>6</sup> = 181 Khz.

Como el generador de tensión rectangular o de disparo tiene una frecuencia de 1.1 Khz. el período de la misma es

$$T = \frac{1}{f} = \frac{1}{1.1} = 0.90$$

milisegundos

En la Fig. 3-15, se indica la forma en la que se espera obtener la señal en el colector de Q2 que se encuentra saturado -- cuando se aplica una señal de disparo al F.F.

Fig. 3-15 (a) Señal de disparo; (b) respuesta del F.F. a la señal de disparo.

En la Fig. 3-15b, se puede determinar  $\tau$  del modo siguiente;

$$\tau = \frac{\text{C1.R1.R2.}}{\text{R1 + R2}} = \frac{10^{-9} \text{x15.10}^3 \text{x3.3x10}^3}{18.3 \text{x10}^3} = 2.7 \text{x10}^{-6}$$

que en comparación con 0.9 milisegundos resulta

$$\frac{2.7 \times 10^{-6}}{0.9 \times 10^{-3}} \times 10^{2} = 0.3\%$$

lo que en el osciloscopio se observará prácticamente una onda -rectangular y el F.F. diseñado es el de la Fig. 3-16

Fig. 3-16 Diseño completo del F.F. a ser usado tomando como ele mentos activos a los transistores 3C-404.

#### a.- 11 FORMAS DE DISPARAR UN BINARIO

Existen algunas maneras de hacerlo siendo generalmente por los colectores; dichas formas únicamente se ilustrará y enun

ciará por no ser usadas en esta tesis sino una forma de disparo

simétrico por las bases.

Una señal de disparo, normalmente se emplea para provo-car la transición de uno a otro estado y se lo puede hacer con

un pulso de corta duración o con una tensión en escalón la que

producirá el disparo simétrico o asimétrico. En el caso de dis

paro asimétrico Fig. 3-17, la señal de disparo provoca la transición solo en un sentido. En el caso de disparo simétrico Fig

3-18, cada señal de disparo provoca una transición con independencia del estado en que se pueda encontrar el binario.

En la Fig. 3-17, un escalón positivo aplicado a través de un condensador a la entrada del transistor cortado, no dará:

respuesta hasta que la amplitud del escalón supere a la tensión a la que se halla el elemento por debajo del corte.

Fig. 3-17 Binario autopolarizado con disparo asimétrico.

Fig. 3-18 Binario autopolarizado disparado simétricamente por - el emisor.

De los estudios realizados sobre la forma de disparo asimétrico se ha concluido que: Un método excelente para disparar - asimétricamente un binario con el flanco anterior de un pulso - Fig. 3-17, es aplicar dicho pulso mediante una fuente de alta impedancia a la salida del elemento que está cortado. Si el ele - mento es un transistor PNP se necesita un pulso negativo.

Es de anotarse también que existen otras maneras de dis -

parar asimétricamente un binario, y, una de ellas es mediante un elemento unilateral (diodo).

En el caso de un disparo simétrico, la Fig. 3-18 ilustra la forma de disparar un F.F. por los emisores, en este caso es posible el disparo simétrico, debido a la presencia de los condensadores de conmutación y puede realizarse solo si estos condensadores son lo bastante grandes para prevalecer sobre todas las demás capacidades que se encuentran presentes de modo que, durante la transición, las tensiones en dichos condensadores no cambien apreciablemente. Puesto que para disparar este tipo de F.F. se necesita condensadores de conmutación relativamente grandes, este método no es usado especialmente debido a que en ciertas oportunidades se exige un tiempo de resolución lo más corto posible. Existen otras maneras de disparo simétrico, pero usan diodos o triodos auxiliares.

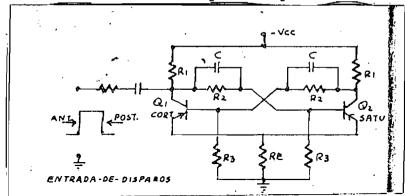

#### a.- 12 DISPARO SIMETRICO DE UN BINARIO POR LAS BASES

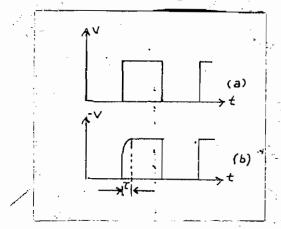

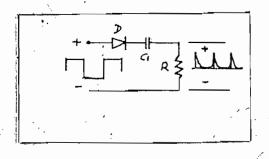

El circuito de la Fig. 3-19, ilustra la forma de disparo simétrico del F.F. autopolarizado en el que el terminal de entrada corresponde al del disparo T, de cuyo análisis nos ocuparemos:

Si se tiene un circuito como el de la Fig. 3-20a que tiene una señal de salida como la ilustrada en la Fig. 3-20b, cuando es exitada por una tensión de onda cuadrada, es muy conocido que la salida adoptará dicha forma cuando la constante de tiem-

po del circuito sea muy pequeña comparada con el semiperíodo de la onda cuadrada T/2.

Fig. 3-19 Binario autopolarizado disparado simétricamente a tra vés de condensadores.

Fig. 3-20 (a); Circuito de disparo (b); Respuesta del circuito - de disparo, cuando R.C T/2.

Fig. 3-21 Circuito de disparo usando un diodo para eliminar los sobrepulsos negativos.

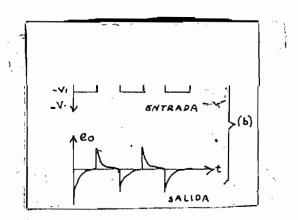

Puesto que se desea que el F.F. duplique el período de - la onda cuadrada de entrada, se puede eliminar los pulsos negativos Fig. 3-20b, evitándonos de este modo que pueda ser disparado también por estos y es de esperarse que la salida del F.F. adopte la forma indicada en la Fig. 3-22c.

Fig. 3-22 Formas de onda (a); Entrada (b); Disparo (c) Salida del F.F.

Para eliminar los pulsos negativos, se usa un diodo conectado en serie con el condensador C como se indica en la Fig.

3-21, asegurando de este modo que el F.F. cambie de estado cada

vez que se produce un pulso positivo.

Si la señal de la Fig. 3-22c, es la salida del colector de Q1, la salida en el colector de Q2 será igual pero con un - defasamiento de  $180^{\circ}$  o de un semiperíodo.

Analizando la Fig. 3-19, en la que se tiene un circuito de disparo como el de la Fig. 3-21, en el que C1 es un capacitor pequeño C1 C y R la resistencia de entrada que presenta - cada base a la señal de onda cuadrada, debiendo anotarse que - dicha capacidad se encontró experimentalmente puesto que no es

posible conocer el valor de R en cada uno de los estados estables; en todo caso su valor para este trabajo oscilará entre 10 y 500pf. En lo que al diodo se refiere, resulta útil cualquier otro que -- sea de contacto o señal y que tenga una resistencia directa relativamente baja, especialmente los de Germanio, porque de no ser - así, sería necesario poner dos o tres diodos en paralelo caso en el cual resulta más ventajoso usar otra forma de disparo como por los colectores e incluso por las bases.

Veamos la Fig. 3-19 y estudiemos su comportamiento: Analizando sus estados estables es decir Q1 cortado y Q2 conduciendo, es imperante anotar los valores calculados en el literal a.- 9 - de este capítulo e indicados entre paréntesis y que corresponden a instantes antes de introducir la señal de disparo.

Si se aplica la señal de la Fig. 3-23a, que representa la salida del circuito Astable, a la configuración de la Fig. 3-23b que es el sistema de disparo utilizado en este trabajo de tesis, donde B1 y B2 son las basesade los transistores del primer F.F. con sus respectivos voltajes Fig. 3-19, es de esperarse que si - se considera al diodo D como ideal, este conducirá cuando el voltaje de la onda cuadrada se encuentre en su valor máximo es decir -0.1v Fig. 3-23a pues en este momento está directamente polari - zado respecto de B2 dando como consecuencia este circuito de disparo una salida en la misma base como la indicada en la Fig. -- 3-23c, en la que es de esperarse que el momento en que la base - B2 llegue al valor -01v, su tensión VBE = -0.1v - (-0.35v) =0.25v lo que indica que se encuentra inversamente polarizada y el tran

sistor Q2 irá al corte mientras que Q1 deberá dejar su estado y pasar a saturación produciéndose de este modo la transición y lo

grándose una salida como la indicada en la Fig. 3-23d la que ser

virá como señal de disparo del siguiente F.F. el mismo que se acoge al razonamiento anteriormente expuesto. El resultado obtenido prácticamente, ratifica las consideraciones anteriores y es

así como el circuito diseñado estará equipado con redes de disparo riguales a las de la Fig. 3-23b.

Fig. 3-23 (a); Señal del astable (b); Circuito de disparo (c); Voltaje de disparo en la base de Q2 (d); Señal de salida del primer F.F.

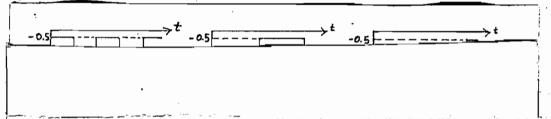

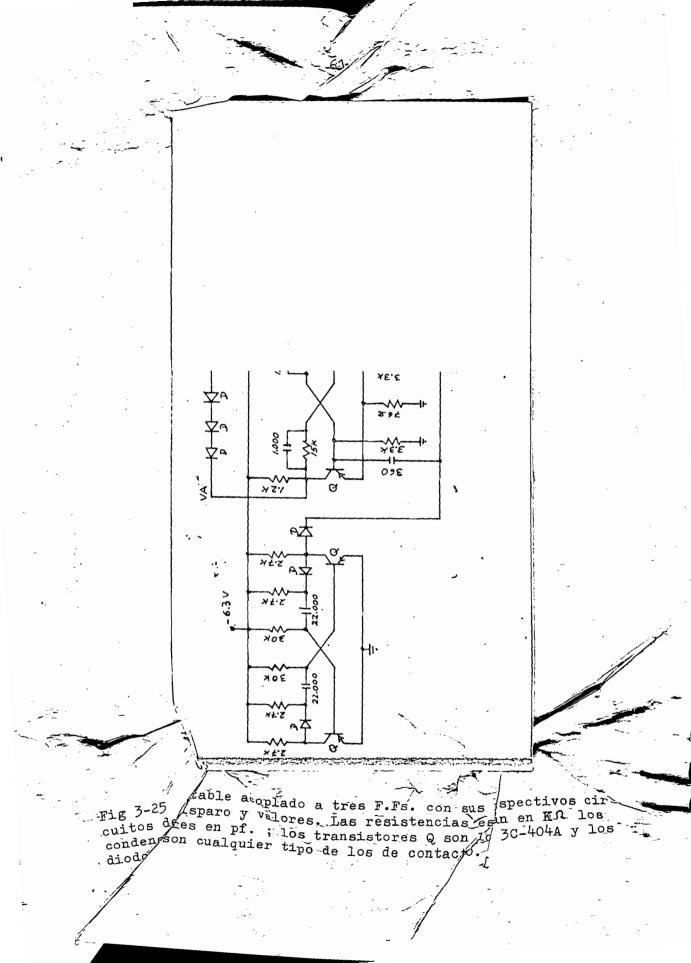

Es preciso que los condensadores C1 se eligan lo suficien temente pequeños con el objeto de que después que entre el escalón, la tensión en las bases puedan caer antes que la tensión de los condensadores de conmutación sufran una variación apreciable. Finalmente las tensiones en C y C' Fig. 3-19 se intercambiarán y el F.F. se acomodará a su nuevo estado. Debido a que la señal -- que produce el disparo es una onda cuadrada, el F.F. responderá al flanco ascendente pero no al descendente cumpliéndose el requerimiento de la Fig. 2-18, quedando indicado el circuito diseñado en la Fig 3-25.

En la sección correspondiente al diseño numérico de los

F.Fs. se dedujo que VCN2 - VCN1 = VWO = -5.48 + 0.48 = -5v que

es la magnitud de la onda cuadrada por lo que en los puntos VA,

VB y Vc de la Fig. 3-25 se tendrán salidas como las indicadas

en la Fig. 3-24a,b y c; respectivamente, es decir con ≈ 0.5v DC

que para poder sumarlas es necesario eliminar esta parte de DC.

lográndose con diodos que prácticamente resultan en número de

tres conectados en serie como se ilustra en la Fig. 3-25 obtenién

dose las salidas V1, V2 y V3 indicadas en la Fig. 3-24d,e y f,

respectivamente, quedando listas para ser sumadas.

Fig 3-24 (a); (b); y (c) Voltajes de salida de cada uno de los - tres F.Fs. de la Fig. 3-25. (d); (e) y (f) Tensiones que aparecen despues de los diodos en serie de la Fig. 3-25.

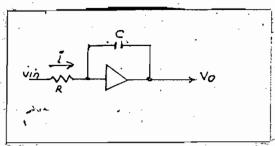

### a. - 13 DISEÑO DE LOS AMPLIFICADORES OPERACIONALES

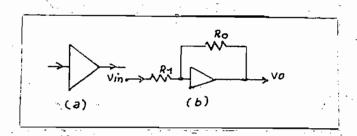

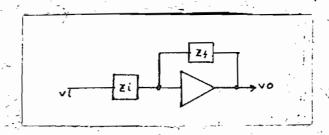

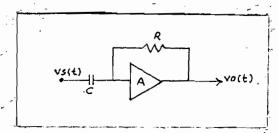

Un amplificador operacional es un aparato o elemento electrónico usado en computación con una alta ganancia DC., una impedancia de entrada y una impedancia de realimentación como se indica en la Fig. 3-26.

Fig. 3-26 Representación gráfica básica de un amplificador operacional.

Una de sus aplicaciones es en las computadoras analógicas en las que se establece un circuito eléctrico tal, que su respues ta es la solución de una ecuación diferencial.

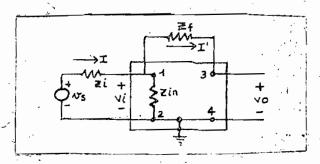

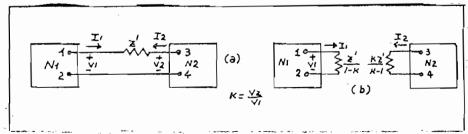

Un amplificador operacional debe satisfacer las condiciones indicadas en la Fig. 3-27, en la que los terminales de entrada 1 y 2 y los de salida 3 y 4, tiene ganancia real negativa grande y lo único que se añade son las impedancias Zi y Zf. La impedancia Zin es la impedancia de entrada del amplificador. El amplificador encerrado en la Fig. 3-27 se denomina amplificador básico y puede contar de uno o más pasos de amplificación de válvu-las o transistores en cascada. Para este trabajo se hará uso exclusivamente de transistores.

Consideremos el diagrama de la Fig. 3-27 y supondremos - que el amplificador es ideal en el sentido que Zin es infinita y que Vo/Vin = -A; si esto ocurre, la corriente I debe pasar por

Zi y Zf concluyéndose que I = I' y en consecuencia

$$I = \frac{\text{Vin} - \text{Vo}}{2f} = \frac{\text{Vs} - \text{Vin}}{2i}$$

$$\text{pero} \quad \text{Vin} = \frac{\text{Vo}}{-A} \quad \text{luego}$$

$$\frac{\text{Vo}}{-A} = \text{Vo} \quad \text{Vo} \quad \frac{\text{Vo}}{-A} \quad \text{Zi}$$

$$\frac{\text{Vo} + \text{AVo}}{2f} = \frac{-\text{A.Vs} - \text{Vo}}{2i}$$

$$\text{Vo}(\text{Zi} + \text{AZi} + \text{Zf}) = -\text{Vs.A.Zf}$$

$$\frac{\text{Vo}}{2f} \left\{ \frac{1}{A} (1 + \text{Zf/Zi}) + 1 \right\} = -\text{Vs.A.Zf/A.Zf.Zi}$$

bajo la suposición de que la ganancia de tensión sea lo suficientemente alta como para que

$$1 \gg \left| \frac{1}{A} (1 + \text{Zf/Zi}) \right| \quad \text{resulta que}$$

$$\frac{\text{Vo}}{\text{Vs}} = -\frac{\text{Zf}}{\text{Zi}} \qquad (3-15)$$

Si  $\text{Zf} = \text{Rf} \quad \text{Y} \quad \text{Zi} = \text{Ri}$

$$\text{Vo} = -\frac{\text{Rf}}{\text{Ni}} \cdot \text{Vs} \qquad (3-16)$$

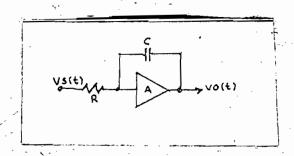

lográndose multiplicar por una constante que es la relación Rf/Ri La Ec.(3-15) también es representada del modo siguiente:

tiempo representa:

$vo(t) = -\frac{1}{C \cdot R}$  vs(t)dt + vo(t0) obteniéndose un integrador y su representación es la de la Fig. 3-28

Fig. 3-27 Representación de un amplificador operacional.

Fig. 3-28 Representación gráfica de un integrador.

Cuando Zi(s) = 1/Cs y Rf = R de la Ec.(3-17) se tiene

Vo(s) = -RCs.Vs(s) lo que en el dominio del tiempo es vo(t) = -RC. $\frac{d}{dt}$  vs(t) lográndose un diferenciador y cu ya representación gráfica se ilustra en la Fig. 3-29.

Fig. 3-29 Representación gráfica de un diferenciador.

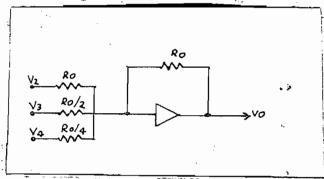

Cuando se tiene el circuito de la Fig. 3-30, se cumple que

$$Vo(s) = -\frac{Rf}{Ri} V1(s) - \frac{Rf}{R2} V2(s) - \frac{Rf}{R3} V3(s)$$

Que representa la ecuación de un circuito sumador de tensiones y multiplicador por una constante Rf/Ri donde Ri = R1;R2;R3;

la misma que en el dominio del tiempo representa la Ec.(3-18)

$$\left(\frac{v1(t)}{R1} + \frac{v2(t)}{R2} + \frac{v3(t)}{R3}\right)$$

(3-18)

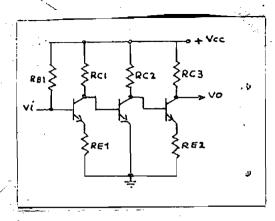

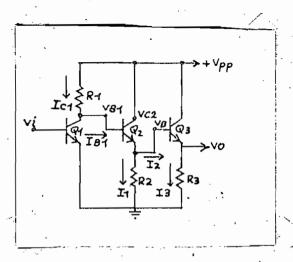

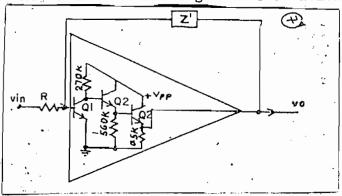

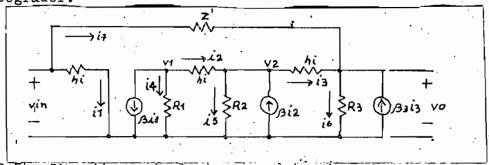

El circuito electrónico de la Fig. 3-31, representa un amplificador operacional ideal porque cumple con requerimientos del mismo, es decir, tener acoplamiento directo, alta impedancia de entrada y una amplificación negativa muy grande; no obstante, si analizamos el amplificador ilustrado en la Fig. 3-32, se observará que posee acoplamiento directo, alta ganancia como se demostrará posteriormente, pero su impedancia de entrada es relativamente baja por lo que se creería que no resulta útil para nuestros propósitos de usarlo como un amplificador operacional y como tal en un sumador de tensiones.

Fig. 3-31 Amplificador operacional óptimo.

Dicho amplificador únicamente posee una etapa de amplificación constituida por el transistor Q1 y una segunda etapa que

es un seguidor de emisor con el propósito de aumentar la corriente de carga.

Fig. 3-32 Tipo de amplificador operacional a ser usado como sumador.

a.- 14 DISEÑO DEL AMPLIFICADOR OPERACIONAL QUE SERA USADO COMO SUMADOR.

Los transistores a ser usados son los 40321 RCA NPN de Si que poseen las siguientes características:

VCER =

$$300v$$

Pt(W) = 5 Ic(A) = 0.5  $h_{pp}$  = 25-200

Condiciones que debe cumplir:

- 1.- Tener alta ganancia negativa.

- 2.- Acoplamiento directo

- 3.- Máxima corriente que circule por RE = 10mA.

Con las condiciones anteriores podemos realizar la POLARI-

Asumimos un  $h_{FE}$  intermedio entre 25 y 200, adoptando un - valor de 120; al igual que el hi, lo consideramos como de 1K $\Lambda$ -

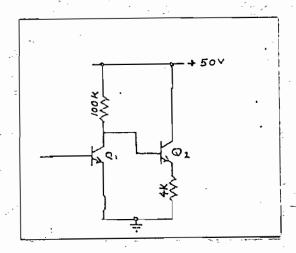

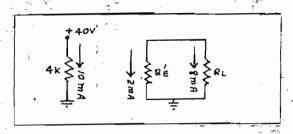

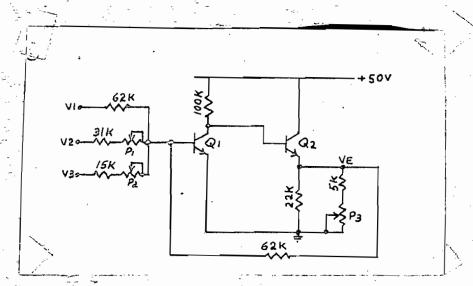

Puesto que este amplificador se usará para dar un voltaje de salida de 40v máximo, se pueden hacer las siguientes consideraciones:

si IEmax = 10mA y Vcc = 50v

entonces RE =

$$\frac{\text{Vomax}}{\text{IE.max}} = \frac{40\text{v}}{10\text{x}10^{-3}\text{A}} = 4\text{K}\Omega$$

VB =  $40\text{v} + \text{VBE} = 40\text{v} + 0.6\text{v} = 40.6\text{v}$

EB  $\approx \frac{\text{IE}}{3} = \frac{10\text{x}10^{-3}}{120} = 83\text{x}10^{-6}\text{A}$  luego

Rc =  $\frac{50\text{-VE}}{\text{IB}} = \frac{50\text{-}40.6}{83\text{x}10^{-6}} = 9.4\text{x}10^{6}/83 = 113\text{K}\Omega$

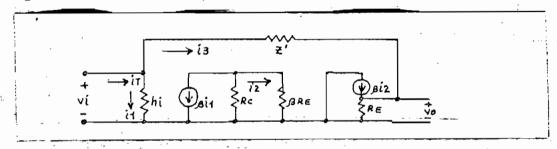

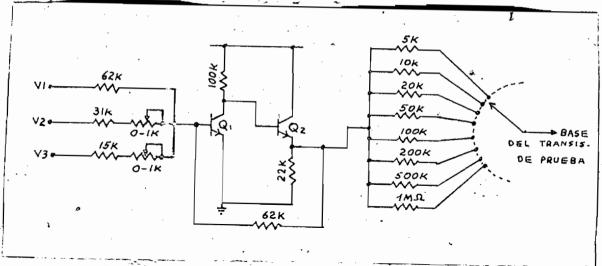

El valor de Rc prácticamente es de 100K que es comer - cial pero con su porcentaje de tolerancia puede hacer que el amplificador trabaje normalmente. En lo que al transistor Q1 se refiere, se lo ha diseñado de tal forma que la corriente que active al mismo, sea aquella de la señal de entrada y la resistencia.conocida como Rf la que le dará la polarización requerida. En consecuencia el circuito diseñado es el de la Fig. 3-33.

## a. - 15 DETERMINACION DE LA GANANCIA

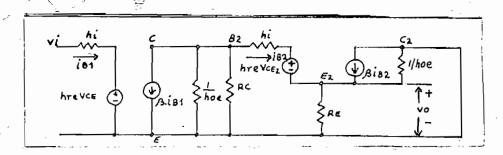

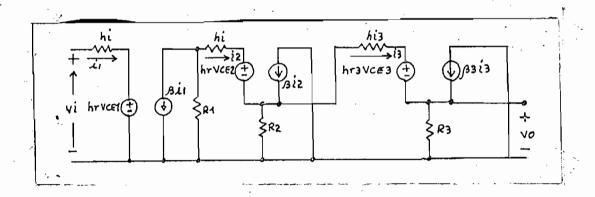

El circuito equivalente a partir del cual se calcula la -ganancia del amplificador de la Fig. 3-33 es el de la Fig. 3-34

Fig. 3-33 Amplificador operacional diseñado para ser usado como sumador.

y un circuito simplificado de el de la Fig. 3-34 es el de la Fig. 3-35 del cual haremos uso para el análisis y las simplificacio - nes respectivas.

hr es muy pequeño por lo que hr.VCE resulta despreciable, 1/hoe es tan grande que se lo puede considerar circuito abierto con bastante aproximación; también se puede simplificar ( $\beta + 1$ )  $\approx \beta$  sin cometer un error apreciable.

Fig. 3-34 Circuito equivalente para AC del amplificador de la - Fig. 3-32.

A consecuencia de que la frecuencia con la que se trabaja

res prácticamente pequeña 550Hz, se puede considerar el A AC del transistor como el A de DC; es decir 132120.

Fig. 3-35 Circuito equivalente simplificado de la Fig. 3-34.

De la Fig.3-35 se deduce que:

$$iB1 = \frac{vin}{hi}$$

$$(hi + \beta RE) / / Rc = RA$$

$$v1 = -\beta iB1xRA$$

$$iB2 = \frac{v1}{hi + \beta RE}$$

$$vo = \frac{v1x \beta RE}{hi + \beta RE} = -\frac{vin \cdot RA \cdot RE \cdot \beta^{2}}{hi (hi + \beta RE)}$$

$$\frac{vo}{vin} = \frac{\beta^{2} \cdot Rc \cdot RE}{hi (hi + \beta RE + Rc)}$$

$$(3-19)$$

A = Amplificación del circuito de la Fig.3-32.

De la Ec. (3-19), tambień es posible hacer una siguiente - aproximación pues resulta que ( $\beta$  RE + Rc) $\gg$  hi quedando la Ec. - (3-20).

$$A = -\frac{\beta^2 \cdot Rc \cdot RE}{hi(\beta RE + Rc)}$$

(3-20)

Sustituyendo en la Ec.(3-20) los valores de la Fig.3-33,

- se obtiene la amplificación teórica a máxima carga y que será:

$$A = -\frac{120^2 \times 100 \times 10^3 \times 4 \times 10^3}{10^3 (120 \times 4 \times 10^3 + 4 \times 10^3)} \approx -11.900$$

Con tal amplificación, se puede afirmare que este amplificador está dentro de los operacionales aunque no cumple la condición de tener una impedancia de entrada muy grande por tratarese de transistores. De su funcionamiento como sumador resulta - lo siguiente:

RE, representa la resistencia de emisor del seguidor de emisor en la que está incluida la resistencia de carga y que se desarrollará en el literal a.- 17.

Asumimos que nuestra corriente máxima sea 1mA por escalón y que el primero de los mismos esté a 5v; de lo que se desprende que el octavo escalón tendrá 40v, con una resistencia de limitación de corriente que permita el paso de 8mA, la que a la postre se convertirá en la máxima corriente de base del transis tor de prueba.

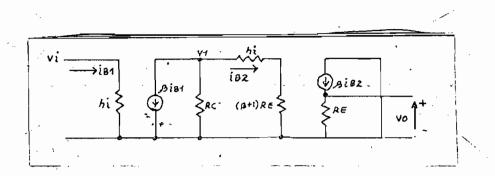

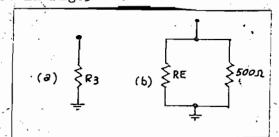

La Fig.3-36, ilustra la resistencia de emisor RE del seguidor de emisor desarrollada, en la que se asume que la máxima corriente de carga es 8mA a 40v y que proporciona la siguiente información:

$$RL = \frac{40v}{8mA} = 5KA$$

$$R'E = \frac{40v}{2mA} = 20KA$$

puesto que estos valores no son comerciales, se usa R'E = 22K 2.

con su porcentaje de tolerancia y RL una resistencia variable cuyo valor mínimo debe ser  $5 \text{K} \Omega$ .

Fig. 3-36 Resistencia RE desarrollada.

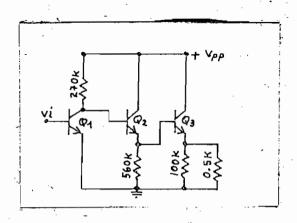

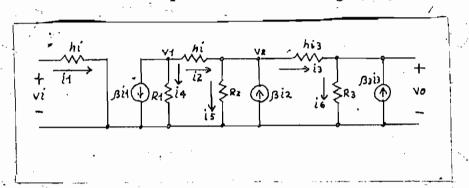

a.- 16 FUNCIONAMIENTO DEL AMPLIFICADOR DISEÑADO COMO SUMADOR.

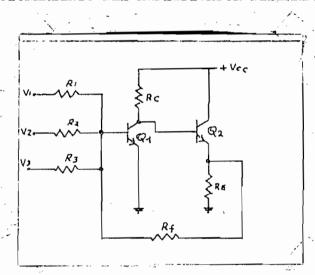

Fig. 3-37 Amplificador operacional usado como sumador.

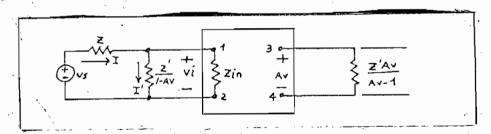

Usando el teorema de Miller ilustrado en la Fig.3-38a y b y aplicándolo en la Fig. 3-27, tenemos:

Fig. 3-38 Teorema de Miller.

Por definición Av =  $\frac{\text{Vo}}{\text{Vin}}$  con Z' conectado.

Fig. 3-39 Aplicación del teorema de Miller al circuito de la -- Fig. 3-27.

El circuito equivalente para determinar Av del amplificador de la Fig. 3-37 es el siguiente Fig. 3-40 con sus respectivas simplificaciones:

Fig. 3-40 Circuito equivalente para determinar Av.

Asumiendo que hi + (β + 1)RE ≈ /3 RE

$$i1 = \frac{\text{vin}}{\text{hi}} \qquad i2 = -\frac{\beta \text{i1.Rc}}{\text{Rc} + \beta \text{RE}} \qquad \text{vo} = -(\beta \text{i2} + \text{i3})\text{RE}$$

$$i3 = \frac{\text{vin} - \text{vo}}{\text{Z'}}; i3\text{Z'} = \text{vin} - \hat{\text{vo}} \qquad \text{vin} = \text{vo} + \text{i3Z'}$$

$$\text{luego vo} = (\beta \text{i2} + \frac{\text{vin} - \text{vo}}{\text{Z'}})\text{RE} = (\underline{\text{Z'}})^3 \text{i2} + \text{vin} - \text{vo}/\underline{\text{Z'}})\text{RE}$$

Resolviendo las últimas eduaciones, resulta que:

$$\frac{\text{vo}}{\text{vin}} = \text{Av} = \left(\frac{-\cancel{3}^2 \cdot \text{Z'\cdot Rc} + \text{hi}(\text{Rc} + \cancel{3}\text{RE})}{\text{hi}(\text{Rc} + \cancel{3}\text{RE})(\cancel{2}' + \text{RE})}\right) \quad (3-21)$$

Asumiendo que  $Z' = 62K\Omega$  y las otras resistencias las ilustradas en la Fig.3-33, tenemos:

$\beta$  = 120 Rc = 100K $\Omega$  hi = 1K $\Omega$  RE = 4K $\Omega$ - máxima carga, y, reemplazando estos valores en la Ec.(3-21) resulta que

con lo que se puede trabajar en la Fig.3-39, en la que

$$\frac{Z'}{1-Av} = \frac{62K \,\Omega}{1+9300} = 6.67 \,\Omega \qquad (Z'/(1-Av)//hi \, 2 \, \frac{Z'}{1-Av}$$

puesto que hi es muy grande en comparación con el paralelo.

$$vin = vsx \frac{Z'}{(1-Av)(Z+Z'/(1-Av))} = \frac{vs.Z'}{Z(1-Av) + Z'}$$

$$como vo = vin.Av vin = vo/Av de donde$$

$$\frac{vo}{vs} = \frac{Av.Z'}{Z' + Z(1-Av)}$$

(3-22)

Cuando Z = R1 : Z' = Rf Fig.3-37 y suponiendo que R1=  $62K\Omega$ ; Rf =  $62K\Omega$  y haciendo uso de la Ec.(3-22) se tiene:

$$\frac{\text{vo}}{\text{vs}} = \frac{-9.300\text{x}62\text{x}10^3}{62\text{x}(1+9300)/_{10}^{-3}} \approx ^{-1}$$

$$\text{vo } \approx -\text{vs} \qquad \text{y como vs resulta ser v1}$$

$$\text{vo } \approx -\text{v1}$$

$$\text{Cuando } Z = \text{Rf/2} = 31\text{K} \text{s.tenemos}:$$

$$\frac{\text{vo}}{\text{v2}} = \frac{-9300 \times 62 \times 10^{3}}{62 \times 10^{3} + 31 \times 10^{3} (1+9.300)} \approx -2$$

$$\text{vo} \approx -2 \text{v2}$$

$$\text{Cuando Z = Rf/4 = 15.5K$ tenemos:}$$

$$\text{Z = R3 = 15.5K$ Rf = 62K$ $^{\circ}$}$$

$$\frac{\text{vo}}{\text{v3}} = \frac{-9.300 \times 62 \times 10^{3}}{62 \times 10^{3} + 15.5 \times 10^{3} (1+9.300)} \approx -4$$

$$\text{vo} \approx -4 \text{v3}$$

De los últimos tres resultados se nota que cuando Rf/R1=

1, la salida vo es de igual magnitud que v1 pero con signo negativo; cuando Rf/R3 = 2, la salida vo = -2v2 y cuando Rf/R3

= 4, la salida vo = -4v3, cumpliéndose de este modo con el reque

rimiento propuesto en la Fig.2-22. El circuito hasta el momento

diseñado, es el de la Fig.3-41, que por lo deducido anteriormente, se constituye en un amplificador operacional usado como su mador en el que se puede aplicar la Ec.(3-18) y ademas, si v1; v2; y v3 son señales del tipo mostradas en la Fig.2-19a,b,c respectivamente pero con valores negativos, se tendrá una salida vo

como la indicada en la Fig.2-20d defasado 180°; con lo que se ha

cumplido con el diseño del amplificador operacional y el uso de

éste como sumador, dando como resultado el generador de tensión

tipo escalera.

En la Fig.3-41 por no existir resistencias comerciales de 31K y 15.5K , se usan los potenciómetros P1 y P2 con el obje to de poder ajustar a los valores requeridos y también para la -calibración del generador tomando como base a la señal v1 de -5v.

Fig. 3-41 Amplificador operacional usado como sumador y que genera una tensión tipo escalera.

El potenciómetro P3, está representado como tal, pero - prácticamente es un sistema de resistencias que controlarán la corriente de base del transistor de prueba y que para el peor - de los casos que es el diseñado será de  $5k\Omega$

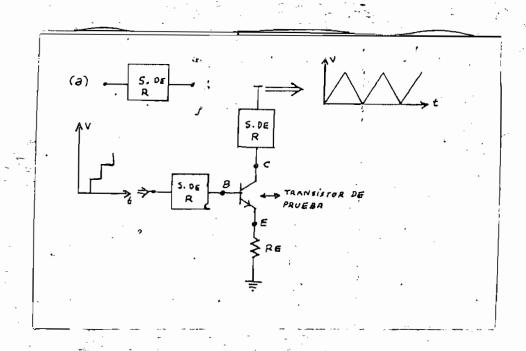

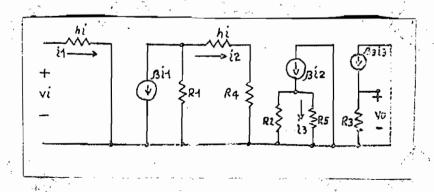

## a.- 17 DISEÑO DE LOS CIRCUITOS RESISTIVOS PARA CONTROL DE CORRIENTE.

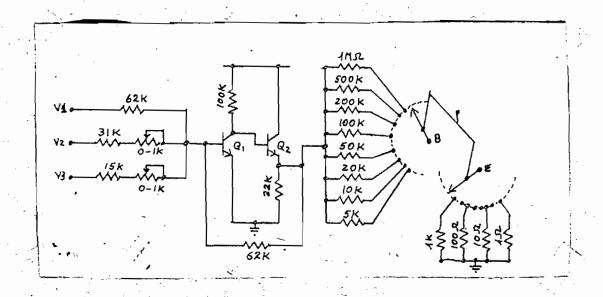

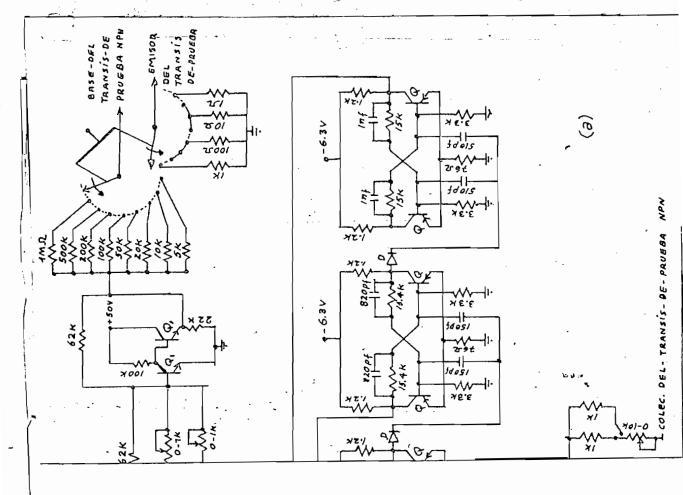

De acuerdo al diagrama ilustrado en la Fig.2-31, el generador de tensión tipo escalera, está unido a la base del transistor en prueba a través de un sistema de resistencias de cuyo diseño nos ocuparemos.

Estudiando el circuito de la Fig.3-41, se concluye que: tratándose de transistores de Si o Ge, en los que el VBE(sat) - es 0.7v y 0.3v respectivamente, se puede limitar la corriente de colector Ic.máx a 200mA y determinar las resistencias R1;R2; ....R8 Fig.3-42 de la siguiente manera:

Fig. 3-42 Circuito que orienta o ilustra la manera de controlar la corriente de base.

Puesto que no se conoce las características del transis tor a probarse, es necesario partir del plano de las suposicio nes y para comenzar diremos que se asume un V'BE promedio porque tampoco se sabe si el componente de prueba (transistor) es de Si o de Ge; consecuentemente:

$$V'BE = \frac{VBE(Si) + VBE(Ge)}{2} = \frac{0.7 + 0.3}{2} = 0.5v$$