# ESCUELA POLITECNICA NACIONAL FACULTAD DE INGENIERIA ELECTRICA

# INTERFASE MICROCOMPUTADOR - MAQUINA VIP DE TARJETAS UNIVAC

IVAN ENDARA

TESIS PREVIA A LA OBTENCION DEL

TITULO DE INGENIERO ELECTRICO EN

LA ESPECIALIZACION DE ELECTRONI

CA Y TELECOMUNICACIONES

Certifico que el presente trabajo ha sido realizado en su totalidad por el s $\underline{e}$ ñor Iván Endara Prieto

ING. HERBERT JACKOBSON

31 Jawbsm M

DIRECTOR DE TESIS

A DIOS;

A MIS PADRES.

# AGRADECIMIENTO

A la Escuela Politécnica Nacional, su alumnado y personal docente; en especial a los Ingenie ros Herbert Jackobson y Malachy J. Foley que han hecho posible la realización de este trabajo.

# · I N D I C E

|         |                                                                  | Pág.       |

|---------|------------------------------------------------------------------|------------|

| INTRODU | CCION: MICROCOMPUTADORES E INTERFASES                            | 1          |

| CAPITUL | O I: ESTUDIO DE LA MAQUINA PERFOVERIFICADORA DE TARJETAS UNIVAC. |            |

| 1.1.    | Modos de funcionamiento                                          | 5          |

| 1.1.1.  | Interruptores                                                    | 6          |

| 1.1.2.  | Teclas                                                           | 7          |

| 1.1.3.  | Indicadores                                                      | 8          |

| 1.2.    | Diagrama general de bloques y flujo de señales-                  | 9          |

| 1.3.    | Memoria                                                          | 14         |

| 1.3.1.  | •                                                                | 14         |

| 1.3.2.  | Direccionamiento                                                 | 15         |

| 1.3.3.  | Habilitación                                                     | <u>1</u> 6 |

| 1.4.    | Transferencia de señales entre memorias y regi <u>s</u>          |            |

|         | tros                                                             | 21         |

| 1.4.1.  | Introducción de datos desde el teclado                           | 22         |

| 1.4.2.  | Verificación y carga de datos desde la estación                  |            |

|         | de lectura                                                       | 23         |

| 1.4.3.  | Secuencia automática de salida de datos                          | 25         |

| 1.5.    | Primera fase de la secuencia automática de sal <u>i</u>          |            |

|         | da de datos                                                      | 27         |

| 1.5.1.  | Flujo                                                                        | 27  |

|---------|------------------------------------------------------------------------------|-----|

| 1.5.2.  | Períodos importantes                                                         | 3 ] |

| 1.6.    | Diagrama de tiempos                                                          | 3 2 |

| 1.7.    | Referencia para la simbología utilizada                                      | 3 3 |

| 1.7.1.  | Zonas de la máquina                                                          | 36  |

| 1.7.2.  | Ubicación de las placas                                                      | 3 7 |

| 1.7.3.  | Clases de elementos                                                          | 38  |

| 1.7.4.  | Tecnología RTL y niveles lógicos                                             | 40  |

| 1.7.5.  | FLIP-FLOPS                                                                   | 4 4 |

| 1.7.6.  | Representación en las láminas del manual                                     | 4.7 |

| CAPITUL | O II: ESTUDIO DEL MICROPROCESADOR Z-80 DESDE EL PUNTO DE VISTA DE INTERFASES | 51  |

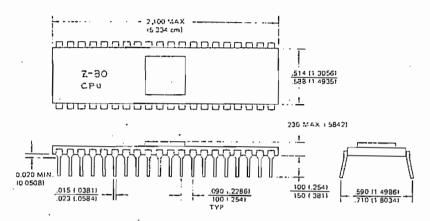

| 2.1.    | Descripción de los pines de Z80-CPU                                          | 53  |

| 2.2.    | Características eléctricas                                                   | 50  |

| 2.2.1.  | Características en DC                                                        | 6 1 |

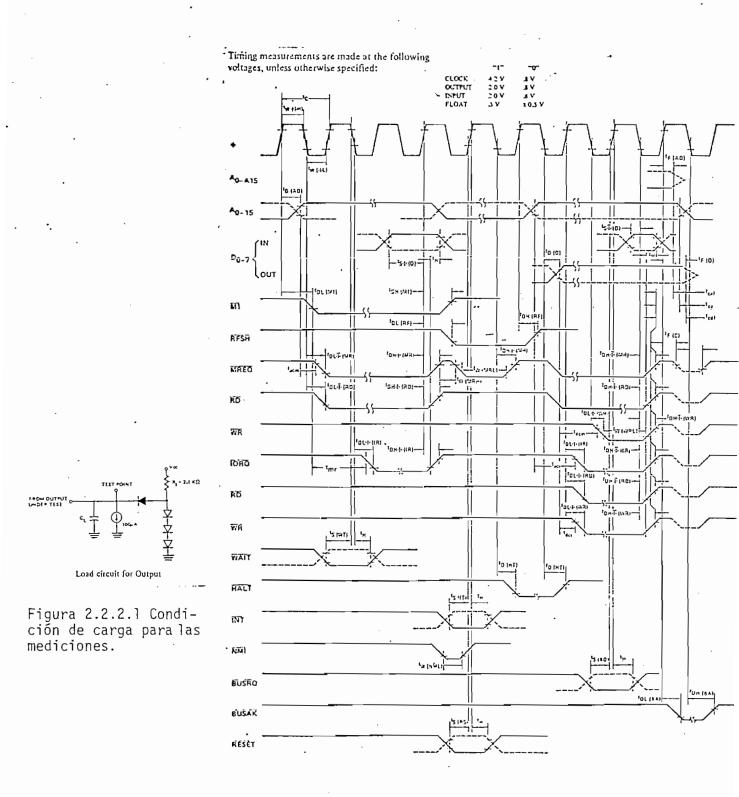

| 2.2.2.  | Características en AC                                                        | 63  |

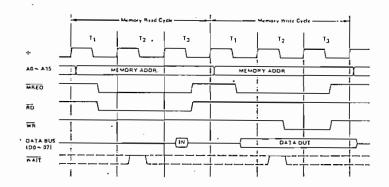

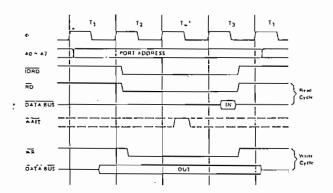

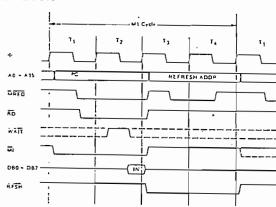

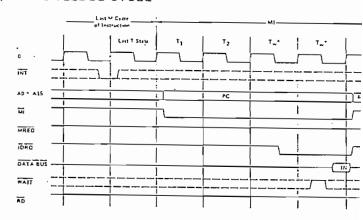

| 2.3.    | Diagramas de tiempo para los ciclos de entrada                               |     |

|         | y salida de datos                                                            | 67  |

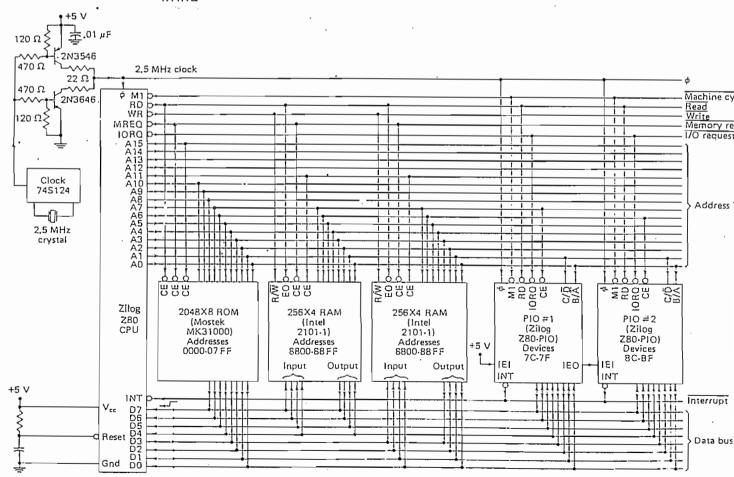

| 2.4.    | Soportes en Hardware para Z80-CPU                                            | 69  |

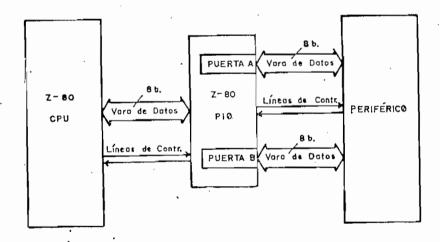

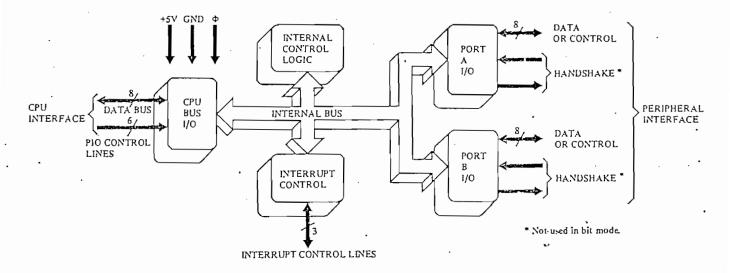

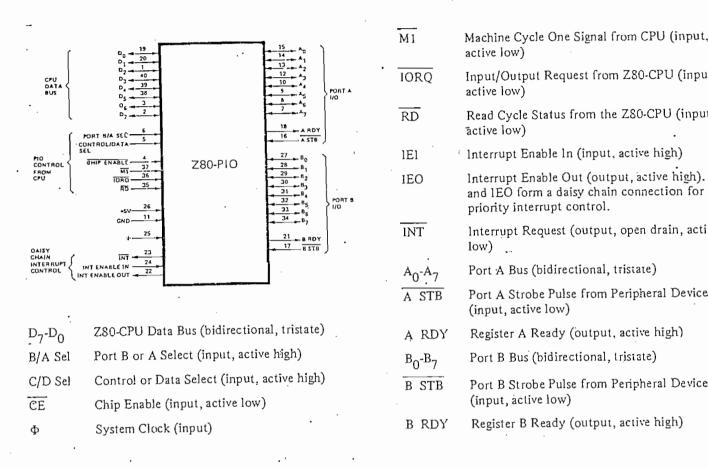

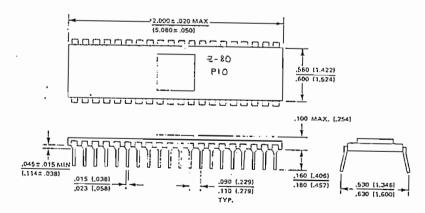

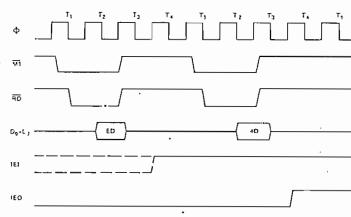

| 2.5.    | El circuito integrado PIO                                                    | 70  |

| 2.5.1.  | Funcionamiento de PIO                                                        | 71  |

| 2.5.2.  | Ventajas de PIO                                                              | 73  |

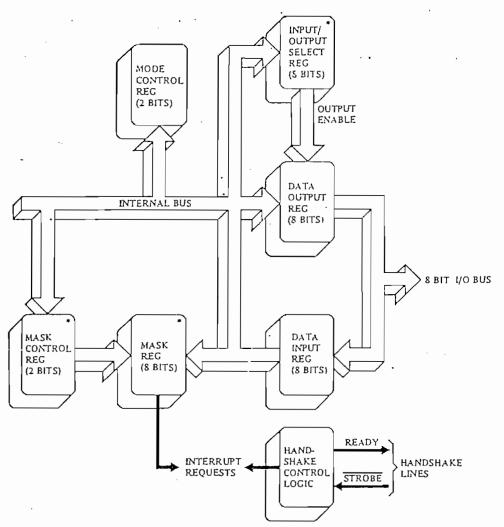

| 2.3.3.   | Descripcion interna                              | 7.5  |

|----------|--------------------------------------------------|------|

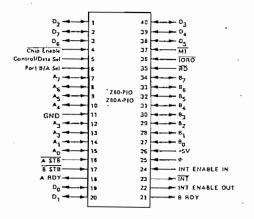

| 2.5.4.   | Pines                                            | 78   |

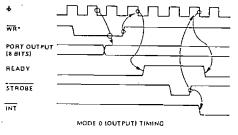

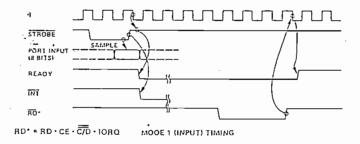

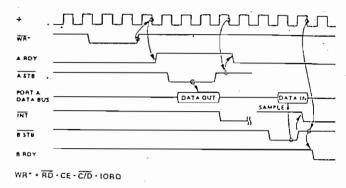

| 2.5.5.   | Diagramas de tiempo                              | 80   |

| 2.5.6.   | Características eléctricas; rangos máximos       | 8.4  |

| CAPITULO | O III: INTERFASE                                 |      |

| 3.1.     | Diversas posibilidades para el Interfase         | 8.8  |

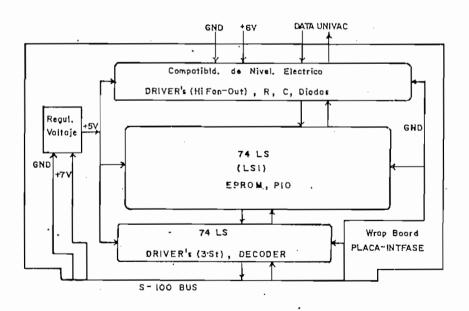

| 3.2.     | Diagrama de bloques para el método escogido      | 9:5  |

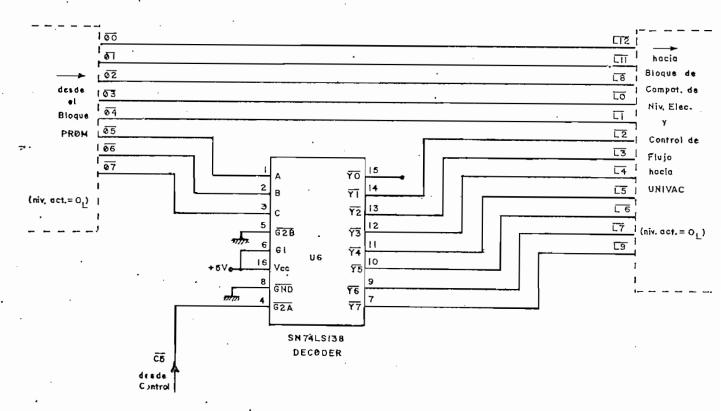

| 3.3.     | Funcionamiento de cada bloque                    | 97   |

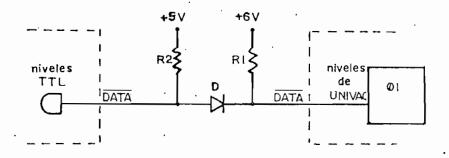

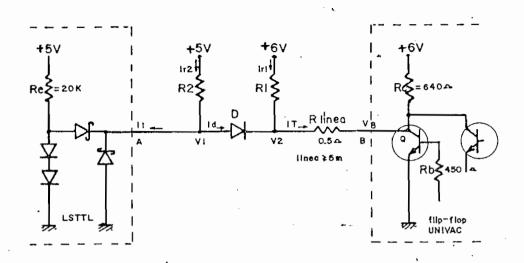

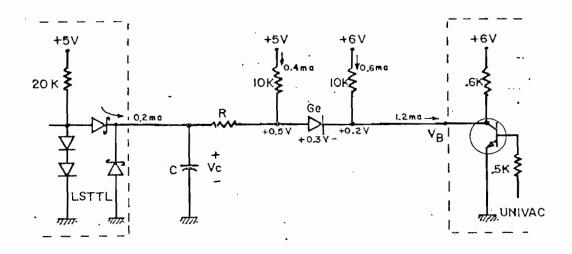

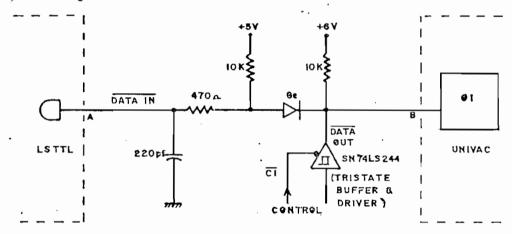

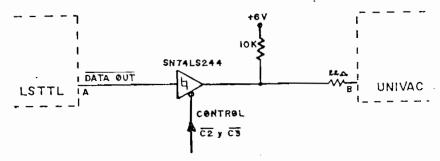

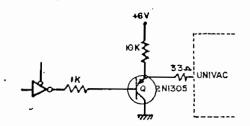

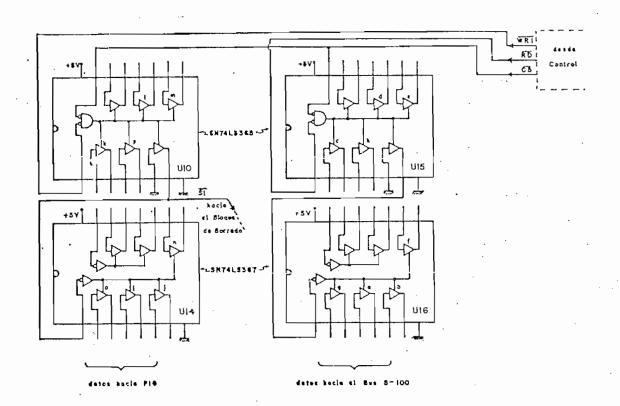

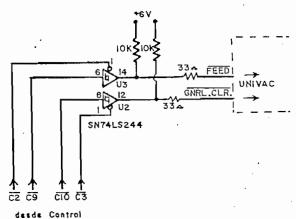

| 3.3.1.   | Bloque de compatibilidad de niveles eléctricos y |      |

|          | control de flujo de datos hacia UNIVAC           | 98   |

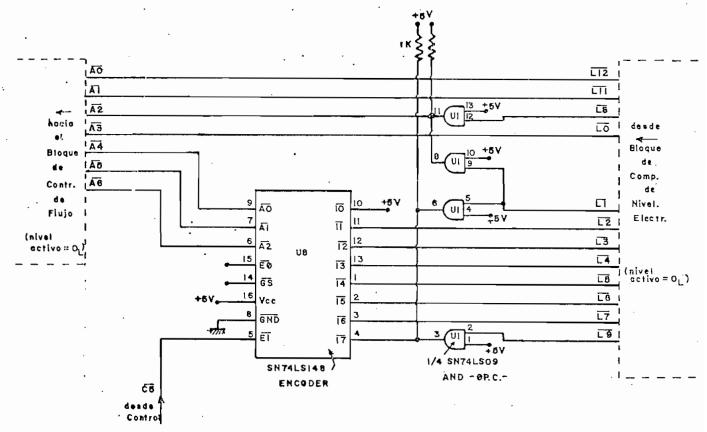

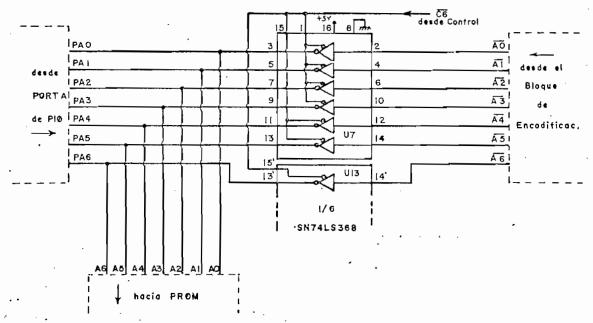

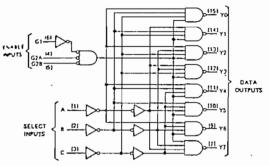

| 3.3.2.   | Bloque de encodificación                         | 106  |

| 3.3.3.   | Bloque de decodificación                         | 112  |

| 3.3.4.   | Bloque de control de flujo A/DE Z80-CPU y den-   |      |

|          | tro del Interfase                                | 114  |

| 3.3.4.1  | Bloque de control de flujo de datos desde el     |      |

|          | bloque de encodificación a PROM                  | 114  |

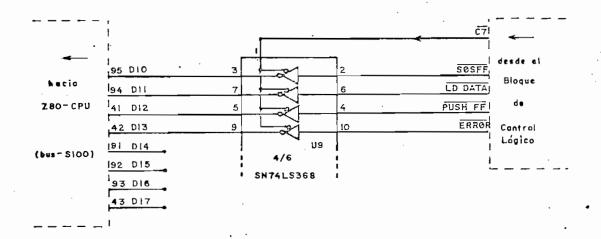

| 3.3.4.2  | Bloque de control de flujo desde el bloque de    |      |

|          | control Lógico a Z80-CPU                         | 115  |

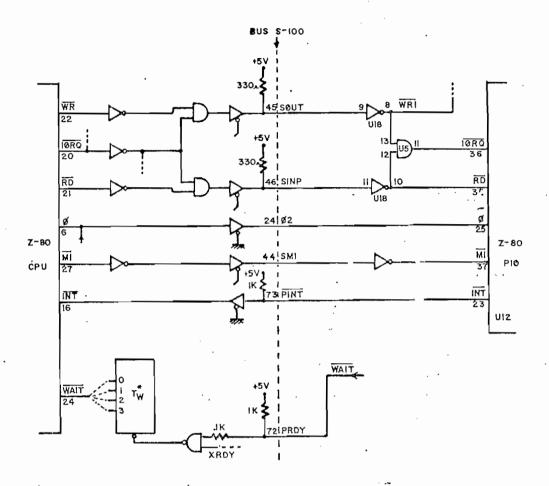

| 3.3.4.3  | Bloque de control de flujo de datos entre Z80 -  |      |

|          | CPU y PIO                                        | 1 1% |

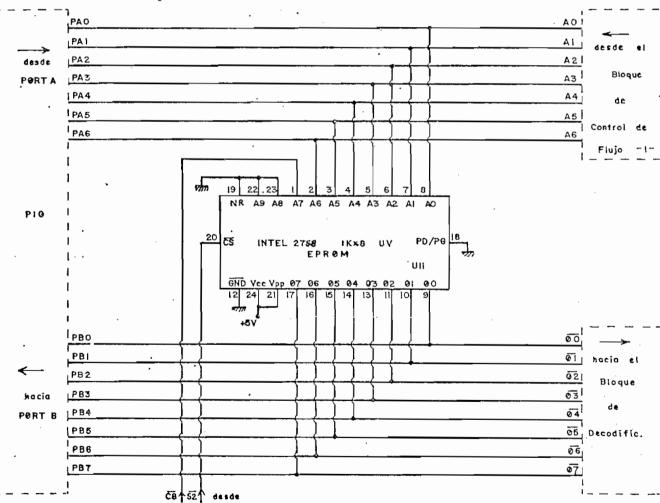

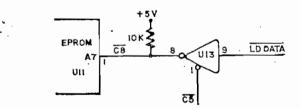

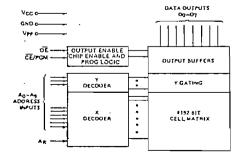

| 3.3.5.   | Bloque PROM                                      | 1 19 |

| 3.3.6.   | Bloque para el borrado del registro de entrada |     |

|----------|------------------------------------------------|-----|

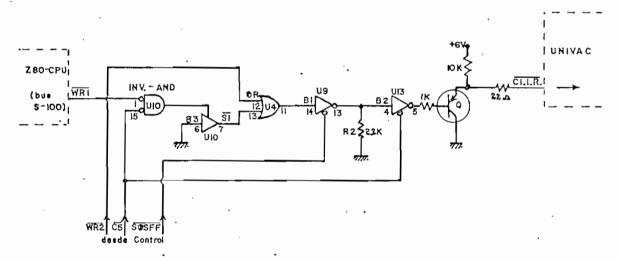

|          | de UNIVAC                                      | 122 |

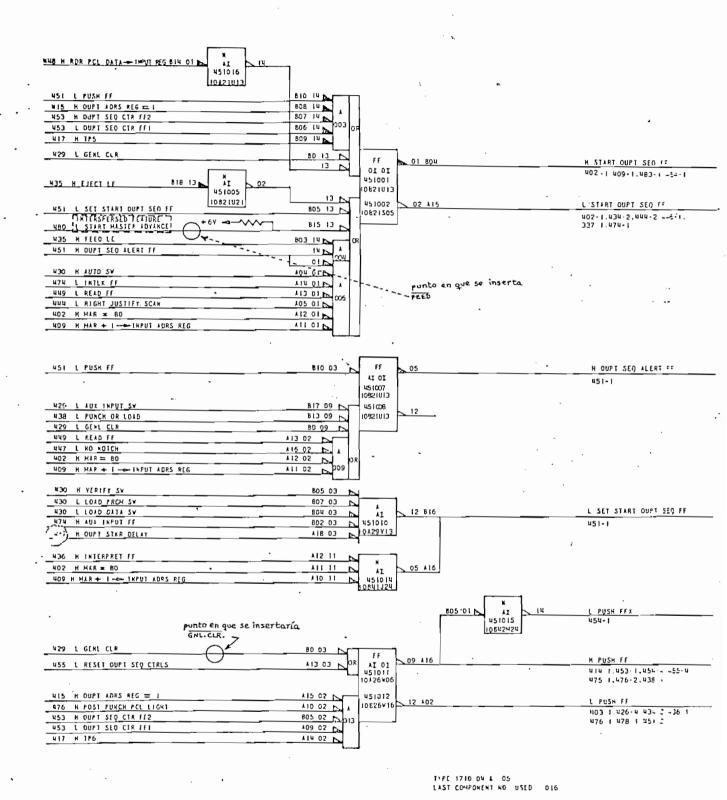

| 3.3.7.   | Bloque de alimentación de nueva ficha y de bo  |     |

| •        | rrado general                                  | 127 |

| 3.3.8.   | Bloque PIO                                     | 128 |

| 3.3.9.   | Bloque de control lógico                       | 131 |

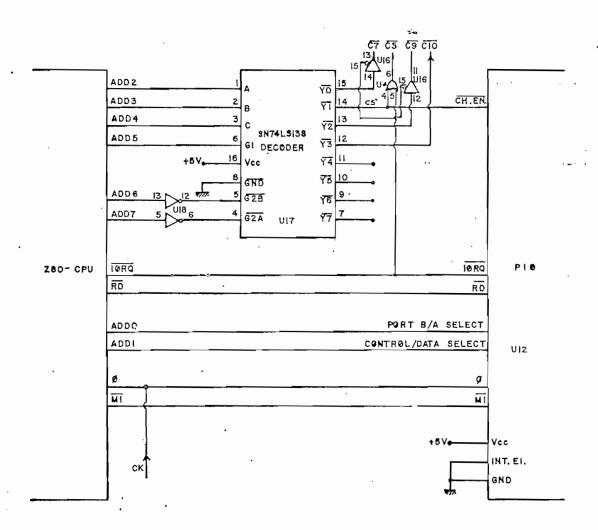

| 3.3.9.1  | Señales provenientes de Z80-CPU                | 131 |

| 3.3.9.2  | Direcciones del Interfase                      | 132 |

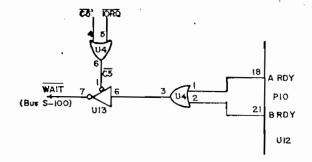

|          | Imposición del estado de espera                | 134 |

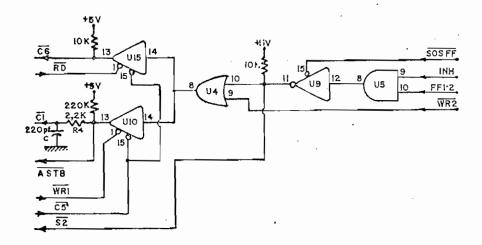

| 3.3.9.4  | Habilitaciones señaladas por UNIVAC            | 135 |

| 3.4.     | Interconexión de bloques                       | 139 |

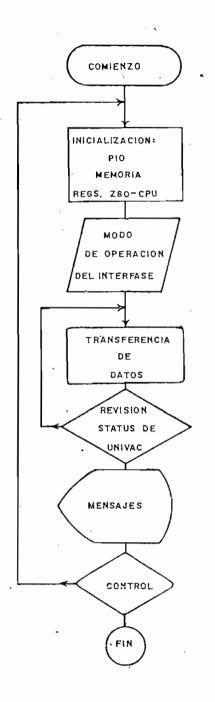

| 3.5.     | Programación                                   | 139 |

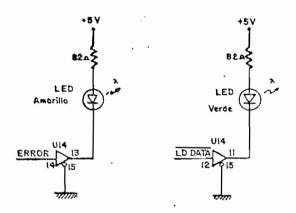

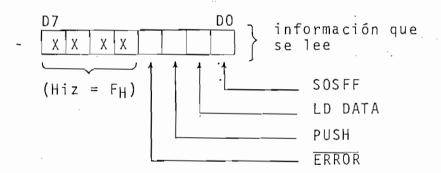

| 3.5.1    | El status de UNIVAC                            | 143 |

| CAPITULO | O IV: CONSTRUCCION PRACTICA                    |     |

| 4.1.     | Ventajas del WIRE-WRAP                         | 145 |

| 4.2.     | Distribución de los elementos en la PLACA INT  |     |

|          | FASE                                           | 147 |

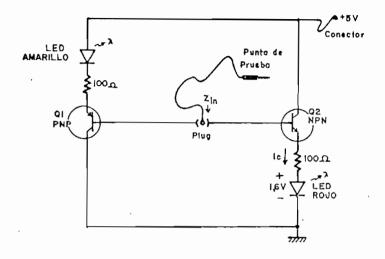

| 4.3.     | Extender card y probador lógico                | 149 |

| 4.4.     | Instalación                                    | 151 |

| 4.4.1.   | Ruido e interferencia                          | 151 |

| 4.4.2.   | Alimentación y puesta a tierra                 | 154 |

| 4.4.3.   | Conectores y enchufes                          | 157 |

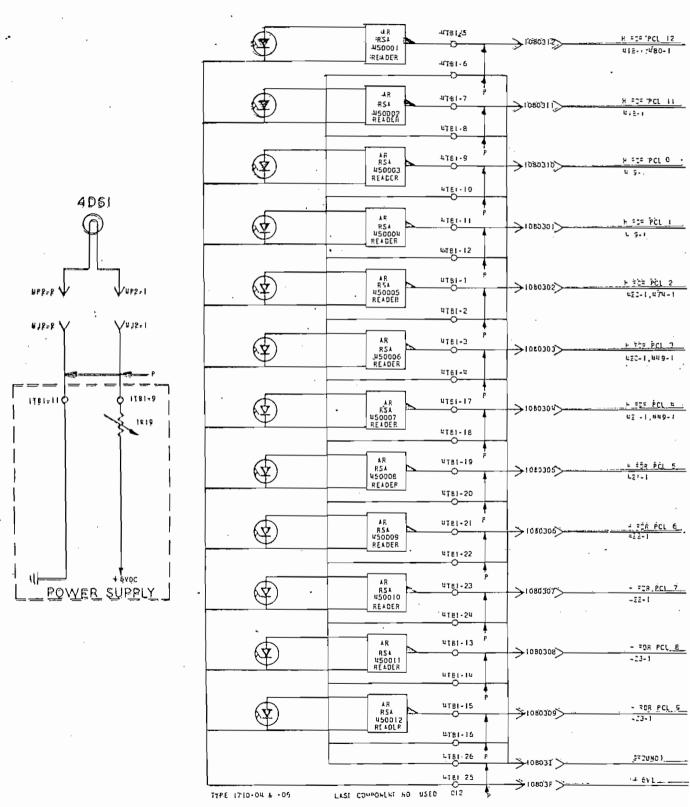

| 4.4.4.   | Las 24 señales en UNIVAC                           | 159 |  |  |  |

|----------|----------------------------------------------------|-----|--|--|--|

| 4.5.     | Pruebas                                            | 162 |  |  |  |

| 4.5.1.   | Pruebas con UNIVAC                                 | 163 |  |  |  |

| 4.5.2.   | Pruebas con Z80-CPU y la PLACA-INTFASE             | 163 |  |  |  |

| 4.5.3.   | Pruebas con todo el sistema interconectado         | 165 |  |  |  |

| 4.6.     | Funcionamiento                                     | 166 |  |  |  |

| 4.7.     | Software                                           |     |  |  |  |

| 4.8.     | Mantenimiento general                              | 170 |  |  |  |

| 4.9.     | Costos                                             | 171 |  |  |  |

| CAPITULO | . O V: COMENTARIOS, RECOMENDACIONES Y CONCLUSIONES |     |  |  |  |

|          |                                                    |     |  |  |  |

| 5.1.     | Comentarios                                        |     |  |  |  |

| 5.2.     | Recomendaciones                                    |     |  |  |  |

| 5.3.     | Conclusiones                                       | 180 |  |  |  |

| Anexo -  |                                                    | 183 |  |  |  |

| Biblioa  | rafía                                              | 226 |  |  |  |

# INTRODUCCION

#### MICROCOMPUTADORES E INTERFASES.

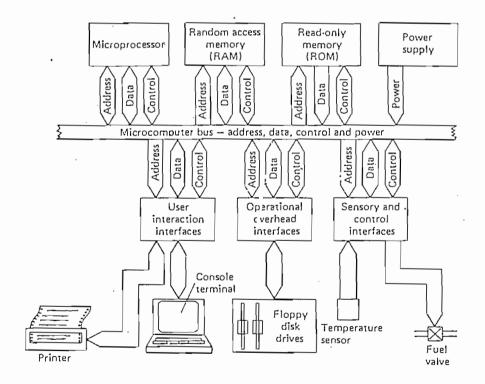

Los microcomputadores son sistemas electrónicos construídos para el procesamiento de cualquier tipo de información, y se componen de un microprocesador, cierta cantidad de memoria y uno o varios "termínales" o "sistemas periféricos" que sir ven para efectuar la entrada/salida de datos en una forma a propiada.

La utilización de los microcomputadores en muchos campos de la vida diaria se ha vuelto común y a veces, imprescindible. Dos factores que han contribuído para que esto suceda son:

- 1. Su relativa facilidad de adquisición;

- 2. Su enorme flexibilidad, que está dada por su capacidad de aceptación y comando de terminales periféricos por medio de lcs "Interfases" o entre-fases.

Se puede, entonces, conformar sistemas de procesamiento de información con características acordes a casi todo propósito. Esta es la finalidad que persigue el diseño de un Interfase.

En forma general se clasifican a los Interfases en cuatro categorías:

a) Interfases Independientes, que permiten el acceso a di<u>s</u>

cos, cintas, memorias masivas en general.

- b) Interfases Interactuantes, para manejo de impresoras, con solas de teclado y video.

- c) Interfases Sensores, utilizados en la adquisición de datos que provienen de algún proceso físico como puede ser, la detección de presión y temperatura de un horno dentro de una fábrica, etc. Estas señales son de naturaleza ana lógica en su mayoría.

- d) Interfases de Control, que se utilizan en el manejo automático de switches, válvulas, generadores de señales, etc.

Figura I.1.1. Esquema de un sistema típico: Microcomputador-Interfases.

Se distinguen dos aspectos en el Interfase:

- 1. El aspecto funcional, que involucra la forma como actúan los distintos elementos que lo constituyen, principalmen te los circuitos integrados y su funcionamiento lógico; así como también el desempeño global del conjunto: y,

- 2. El aspecto eléctrico o de niveles voltamperimétricos, que involucra los requerimientos de corrientes y voltajes pa ra dichos elementos de acuerdo con sus características; aquí se topan asuntos como la correcta alimentación, tiem pos de retardo, ruido, etc.

Estos dos aspectos anotados han sido considerados en el des<u>a</u> rrollo del presente trabajo.

El Interfase aquí tratado cae dentro del grupo de los Interfases Interactuantes y acopla a dos sistemas electrónicos de funcionamiento y características diferentes, cuales son:

- Un microcomputador basado en el microprocesador Z80A (designado Z80-CPU para objeto de simplificación a lo largo del presente); y,

- Una máquina perfoyerificadora de tarjetas con impresión 1710 VIP UNIVAC (designada UNIVAC).

El Interfase permitirá una comunicación bidireccional de da tos, de modo que UNIVAC pueda actuar como terminal de entra da de datos (sea como lectora de tarjetas o por medio de te clado) y/o como terminal de salida de datos en forma de tar jetas perforadas; todo ésto, bajo control automático.

El control automático está determinados por el "sostware" in troducido al microcomputador, en estrecha vinculación con las señales que se produzcan en el mismo Interfase.

Se estudian en primera instancia y por separado ambos sistemas, UNIVAC y Z80-CPU en los capítulos I y II; luego, conociendo sus características particulares y sabiendo de sus funcionamientos, se procede propiamente al diseño del Interfase en el capítulo III.

El capítulo IV considera su construcción práctica.

## CAPIIULO I

# ESTUDIO DE LA MAQUINA PERFOVERIFICADORA DE TARJETAS UNIVAC

El estudio de la máquina perfoverificadora de tarjetas con interpretación ( $\underline{V}$ erifier  $\underline{I}$ nterpret  $\underline{P}$ uncher, VIP) UNIVAC 1710 ha resultado muy interesante, como podrá notarse a través de los diferentes puntos de este capítulo.

Con estos puntos se va profundizando gradualmente en el examen de UNIVAC, para que así, la comprensión de su funcionamien to no ofrezca mayores dificultades.

UNIVAC es una máquina que no ha sido construída para trabajar con Interfases, por ello ha sido necesario analizar la forma cómo podría ser aprovechada justamente para ésto y de ahí el detenimiento que se ha hecho en su estudio.

# 1.1. MODCS DE FUNCIONAMIENTO

Los modos de funcionamiento que tiene UNIVAC son:

- Como perforadora de tarjetas;

- como verificadora de tarjetas;

- como interpretadora de tarjetas.

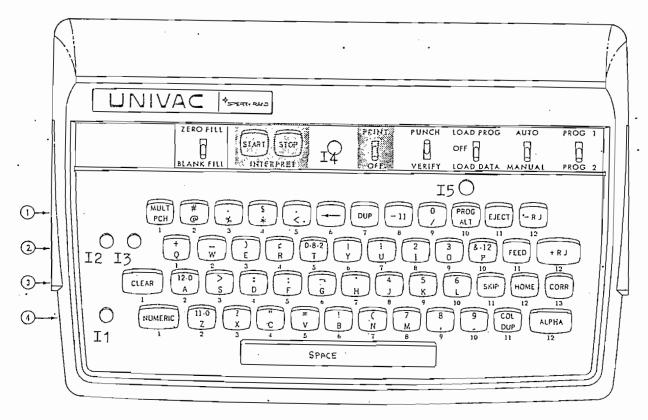

Para ello cuenta con una serie de interruptores, teclas e i<u>n</u>

dicadores, los mismos que se ven en la figura 1.1.

fig. 1.1. TECLADO DE LA 1701 VP Y 1710 VIP

PARA LA LINEA UNIVAC 9000

Solamente en la VIP

# 1.1.1. INTERRUPTORES

- ZERO FILL/BLANK FILL: determina si las columnas a la izquierda de un campo con justificación a la derecha\* deberán ll<u>e</u> narse con ceros ó con espacios en blanco.

- PRINT/OFF: sirve para conectar o desconectar la unidad impresora, de modo que la impresión pueda o no tener lugar, tan

<sup>\*</sup> Se recomienda leer el Manual del Operador de UNIVAC.

to si se está perforando como si se está verificando.

- PUNCH/VERIFY: según la posición de este interruptor, la máquina operará como Perforadora o como Verificadora.

- LOAD PROG/OFF/LOAD DATA: permite al operador cargar programas o datos en memoria a partir de fichas\*. Para empezar a perforar es necesario que este interruptor se encuentre en la posición de OFF.

- AUTO/MANUAL: hace que la máquina realice, bajo control manual o bajo control automático, funciones tales como las de salto, duplicación y alimentación.

- PROG 1/PROG 2: mediante este interruptor el operador puede hacer el cambio de un programa a otro con sólo variarlo de posición.

#### 1.1.2. TECLAS

Se explica brevemente el funcionamiento de algunas teclas  $e\underline{s}$  peciales.

- INTERPRET START/STOP: inician o detienen la interpretación de fichas perforadas; para ello, el interruptor de impresión

<sup>\*</sup> Se utilizan indistintamente las palabras "tarjeta" o "ficha", para referirse a las conocidas tarjetas Hollerith.

deberá estar situado en posición de PRINT.

- MULT PUNCH: permite la perforación múltiple de cuantos datos se deseen en una misma columna.

- COL. DUP: duplica los datos de la memoria, sin afectarla.

- SKIP: permite saltar hasta la primera columna del siguiente campo, borrando las anteriores.

- PROG. ALT.: escoge uno de los dos programas de memoria, esta<u>n</u> do UNIVAC en el modo automático.

## 1.1.3. INDICADORES

Hay cinco indicadores luminosos que dan información sobre las condiciones o status de UNIVAC durante su funcionamiento; és tos son:

- Il: indicador de condición general de error.

- I2: indicador de disparidad o diferencia de caracteres durante la verificación.

- I3: indicador de error luego del tercer intento en la verificación de una columna.

- I4: indicador de modo alfabético o numérico de los datos que se digitan.

- I5: indicador de programa principal o alterno.

Ahora, en orden a indagar cómo ejecuta UNIVAC la serie de operaciones anteriores, se trae a continuación el diagrama de bloques de sus circuitos.

# 1.2. DIAGRAMA GENERAL DE BLOQUES Y FLUJO DE SEÑALES

La figura 1.2. muestra el diagrama general de bloques y fl $\underline{u}$  jo de señales de UNIVAC.

Se da a continuación una idea de lo que es cada bloque.

- READER PHOTOCELL DATA: estación lectora de tarjetas.(Se  $\underline{a}$  precia en la Fig. 3.1.c.).

- READER SPROCKET COUNTER: detector de tarjetas para el sin cronismo de la lectura con los ciclos de la máquina.

- READ-VERIFY LOAD DATA OR PROGRAM: circuito lógico que determina el funcionamiento de UNIVAC como lectora, verifica dora ó alimentadora de datos - cambién programas -.

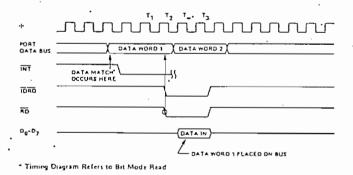

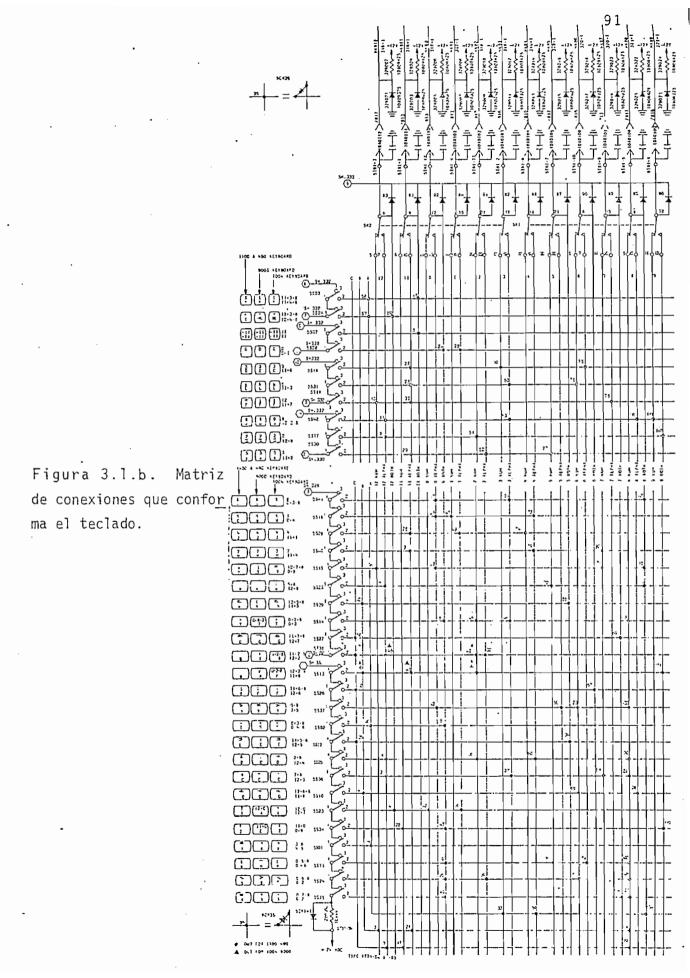

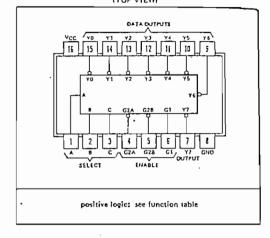

- TRANSLATOR: codificador de caracteres tecleados, en doce lineas que corresponden a las doce zonas en que se divide la tarjeta Hollerith. Se detalla en la Fig. 3.1.b.

- ALPHA: indicador de entrada de caracteres en modo alfabét<u>i</u> co.

- SKIP: salto de columnas en blanco.

- DUPLICATER: duplicador de columnas.

- OPERATIONAL CONTROL: control operacional lógico que automatiza el funcionamiento del flujo de datos de acuerdo al programa alimentado previamente a UNIVAC.

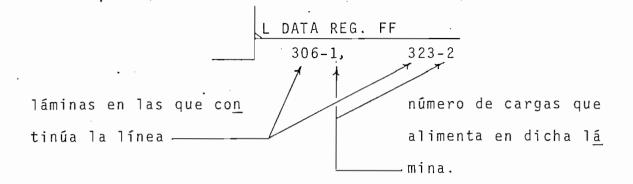

- INPUT REGISTER 12 BITS: registro de 12 bits en para?elo, que almacena un carácter que puede provenir del teclado, de la estación lectora ó de DATA REG, de acuerdo con el ciclo que esté tomando lugar en UNIVAC.

- DATA REGISTER 12 BITS: registro de 12 bits para almacenar un carácter que puede provenir de INPUT REG., de la Memoria de Entrada ó de la Memoria de Salida.

- COMPARATOR: comparador de los caracteres que se encuentran en DATA REG e INPUT REG en un momento dado. Sirve en verificación.

- MISMATCH CHARACTER CONTROL: indicador de caracteres iguales, que actúa una vez realizada la comparación mencionada.

- VERIFY NOT CHARACTER CONTROL: indicador para que se realice o no la comparación de caracteres.

- OUTPUT SEQUENCE COUNTER: contador automático utilizado para indicar las diferentes fases que se suceden en la "Secuencia de Salida de Datos".

- PUNCH SPROCKET: sincronizador de la perforación de tarjetas

- con los ciclos de la máquina.

- CARD MOTION CONTROL: control del desplazamiento de tarjetas.

- PUNCH ODD: perforador de columnas impares.

- PUNCH EVEN: perforador de columnas pares.

- PROGRAM REGISTER: registro que contiene la información de los programas cargados en UNIVAC; dicha información dá el comportamiento que debe tener OPERATIONAL CONTROL para ca da columna de la tarjeta cuando UNIVAC se encuentra en modo automático.

- MEMORY CONTROL: controlador del flujo de datos entre OUTPUT

MEMORY Ó INPUT MEMORY con DATA REG.

- OUTPUT MEMORY: memoria que contiene los datos de la última ficha leida o perforada; estos datos salen luego hacia DATA REG. Contiene también la información del programa 1.

- INPUT MEMORY: memoria que almacena los datos nuevos pro/ $\underline{e}$  nientes de DATA REG. Contiene también la información del programa 2.

- MEMORY SELECTION CONTROL: seleccionador de una de las dos memorias que posee UNIVAC.

- MEMORY ADDRESS REGISTER: Registro que posee la dirección de una localidad de memoria.

- COLUMN INDEX DISPLAY: indicador que permite la lectura en

#### 1.3. MEMORIA

En primera instancia, un estudio sobre la memoria de UNIVAC resulta conveniente, puesto que de esta forma se va a adquirir una idea más clara de las capacidades y limitaciones que presenta esta máquina.

#### 1.3.1. CAPACIDAD

UNIVAC posee dos bloques de memoria como se ha visto en la figura 1.2. El primero, OUTPUT MEMORY o Memoria de Salida de Datos, contiene los datos que saldrán hacia DATA REG. y de allí hacia las bobinas de perforación y registros de impresión. El segundo, INPUT MEMORY o Memoria de Entrada de Datos, almacena los datos que provienen desde el teclado ó la estación lectora. Se los denomina abreviadamente como OUT. MEM. e IN. MEM.

Cada bloque tiene una capacidad de almacenamiento de 80  $p\underline{a}$   $\ell ab \pi as$  \* de 16 bits cada una, con un total de 2.560 bits  $e\underline{n}$  tre ambos.

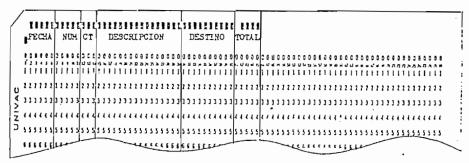

Siendo que una tarjeta contiene 80 columnas, entonces toda su información puede ser introducida a memoria.

Cada bit está construído físicamente por un núcleo de ferr<u>i</u>

<sup>\* &</sup>quot;palabras", "words" o "bytes".

ta, siendo el dato almacenado ahí, no volátil.

Los 16 bits de cada palabra se distribuyen así:

- 12 bits son utilizados para almacenar un carácter alfanumérico. Esto es, los datos contenidos en la memoria, se encuen tran codificados de acuerdo al Código IBM para tarjetas Hollerith (en este código, la tarjeta es dividida en 12 zonas, de manera que cualquier columna de dato equivale a una combinación determinada de estas 12 zonas).

Cuando UNIVAC se halla en el modo de Verificación, el bit de la zona 12 del bloque OUT. MEM. es utilizado para guardar el resultado de la comparación efectuada entre los datos que estan siendo verificados.

- 4 bits son utilizados para almacenar una columna de programa. En dichos 4 bits se codifican las operaciones que debe realizar OPERATIONAL CONTROL cuando UNIVAC se encuentra en el modo automático. En OUT. MEM. se almacena el programa 1 y en IN. MEM. el programa 2.

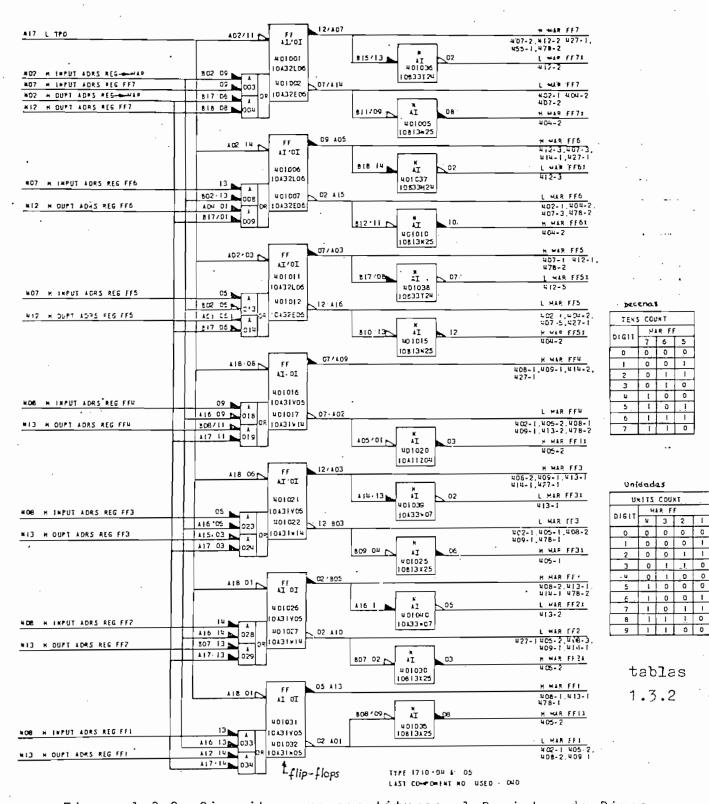

#### 1.3.2. DIRECCIONAMIENTO

Las 80 localidades que posee cada bloque de memoria son direccionadas en una forma especial.

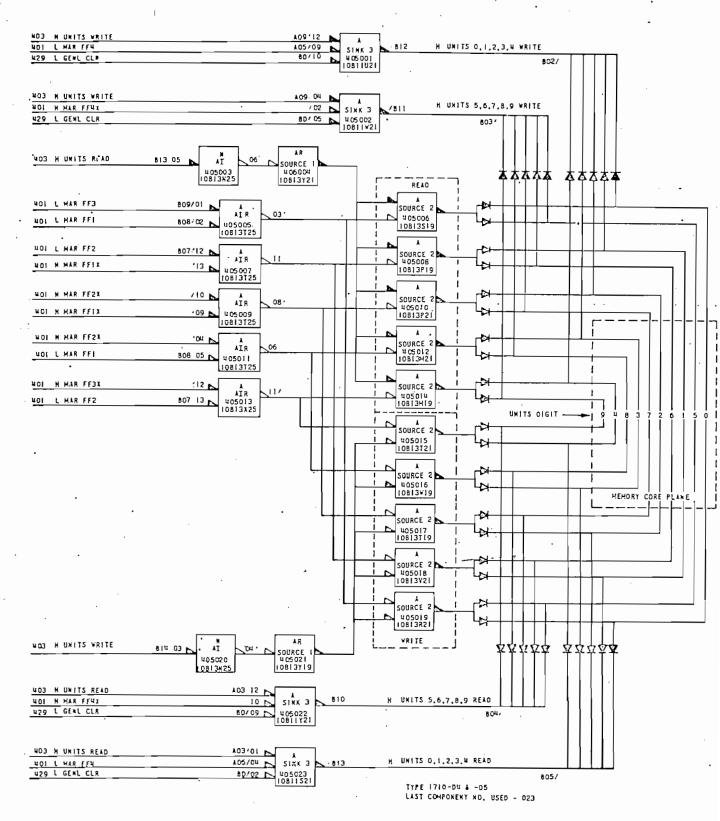

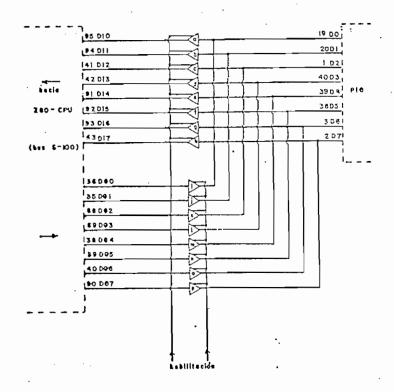

La figura 1.3.2. representa al Registro de Direccionamiento - de la Memoria con sus circuitos\*. Pueden allí verse a los 7 flip-flops utilizados para realizar el direccionamiento, así como algunas señales adicionales que sirven de control y que son generadas en concordancia con las secuencias automáticas que toman lugar en UNIVAC. También se incluyen dos tablas que muestran los estados de los 7 flip-flops para el direccionamiento, tanto de los dígitos de las unidades como de las decenas.

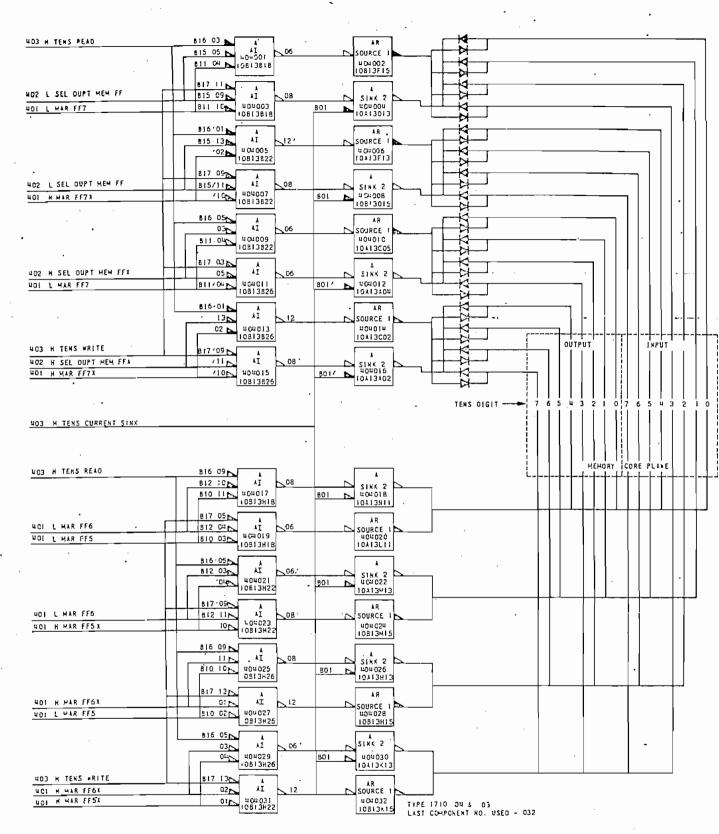

#### 1.3.3. HABILITACION

Cada memoria posee 8 grupos -decenas- que son habilitados en forma individual y, a su vez, cada grupo contiene 10 unidades que son habilitadas en grupos de 5 (figuras 1.3.3.1-2). Las líneas que habilitan a tales grupos y unidades dependen de algunas señales de control y temporización.

Se muestra finalmente la ruta de los 12 bits de datos a través de la memoria en la figura 1.3.3.3. donde se observan cier tos bloques que son los que regulan la intensidad de corriente que pasará a través de los núcleos de ferrita señalando los datos.

<sup>\*</sup> En el punto 1.7. se da una referencia para la simbología empleada en es tas figuras. Por el momento no se requiere ahondar en ello.

Figura 1.3.2. Circuitos que constituyen el Registro de Dire<u>c</u> cionamiento de la Memoria de UNIVAC.

Figura 1.3.3.1. Direccionamiento de los grupos de las decenas de la Memoria.

Figura 1.3.3.2. Selección de las direcciones de unidades de la Memoria.

Figura 1.3.3.3. Ruta de los datos a/de Memoria -habilitación-

En conclusión puede decirse que el acceso directo a la memoria de UNIVAC no es muy sencillo. El lograr artificialmente el direccionamiento y la habilitación de la memoria resulta ser una tarea algo complicada, por lo cual conviene más bien estudiar la forma en que entran y salen los datos por los diferentes registros internos; ésto se lo ha hecho en el siguiente punto.

### 1.4. TRANSFERENCIA DE SEÑALES ENTRE MEMORIAS Y REGISTROS

El paso de los datos a través de los registros y memorias de UNIVAC se realiza en forma secuencial, siguiendo un orden preciso. Las operaciones se suceden principalmente con intervención de circuitos monoestables, biestables y contadores; estos circuitos se encuentran sincronizados en su mayoría con una se ñal maestra de reloj de UNIVAC.

En la figura 1.2. también se observan los dos registros de da tos que intervienen en la transferencia de señales conjuntamen te con la memoria, éstos son DATA REGISTER e INPUT REGISTER; am bos construídos a base de flip-flops y que resultarían ser un sitio muy favorable para lograr un acceso a los datos desde el exterior.

Algunas operaciones automáticas que se efectúan en UNIVAC ( y que se encuentran descritas en el Documento de Servicio de UNIVAC 1710) aclaran la forma como se efectúa la mencionada trans

ferencia de señales, siendo las de mayor interés las siguie<u>n</u> tes:

## 1.4.1. INTRODUCCION DE DATOS DESDE EL TECLADO

Al presionar una tecla, se da inicio a una serie de hechos que se cumplen en muy corto tiempo internamente en UNIVAC, sea para introducir el dato digitado en IN. MEM.,  $\acute{o}$ , si el modo en que se encuentra es el de Verificación, efectuar dicha verificación. En estas operaciones intervienen los registros de datos, de direccionamiento, contadores y los dos bloques de memoria.

La forma como se efectúen dichas operaciones, depende del modo en que se encuentre UNIVAC, esto es, en modo de Perforación  $\acute{o}$  en modo de Verificación.

a) En el modo de Perforación.- La operación de introducción de datos consta de dos "cíclos básicos de memoria" (un ciclo básico de memoria tiene 8 períodos de 5 μseg. cada uno, por lo tanto dura 40 μseg.)\*. El primer ciclo reemplaza el dato de IN. MEM. con el dato que acaba de ser digitado e incrementa en uno el indice de columnas; el segundo ciclo chequea el programa almacenado en la memoria cuando UNIVAC se encuentra en modo automáti

<sup>\*</sup>En el punto 1.6. se explica sobre el"ciclo básico de memoria"

co de operación (más detalles sobre esta operación constan en la tabla 3.1.).

b) En el modo de Verificación.- Utiliza también dos ciclos básicos de memoria; el prime ro realiza la comparación e incrementa el direccionamiento del registro; el segundo chequea el programa almacena do en memoria para el control automático de la operación. Si ocurriera una disparidad, entonces el direccionamiento del registro no es incrementado y son permitidas dos tentativas más para la verificación. Si luego de dichas dos tentativas persistiera el error, el carácter digitado reem plazará al dato que se encontraba en IN. MEM.

Si bien es cierto que los ciclos de memoria se suceden con mu cha rapidez, sin embargo el inicio de los mismos ocurre sola mente una vez que el circuito monoestable de retardo utiliza do para asegurar la estabilidad  $\dot{c}$ el dato digitado y así evi tar los problemas de redisparos, rebotes, sobretiros, etc., haya regresado a su estado original luego de unos 12 mseg. de haber sido presionada la tecla.

1.4.2. VERIFICACION Y CARGA DE DATOS DESDE LA ESTACION DE LE $\underline{c}$

En esta operación, los datos se introducen a través de los

fotodiodos de la estación de lectura y provienen de tarjetas perforadas que se desean verificar ó desde tarjetas perforadas cuyos datos se desean cargar a memoria para luego duplicarlos en otras tarjetas y/o interpretarlos.

En la operación de lectura se utilizan cuatro ciclos de memoria. El primero almacena en IN. MEM: el dato leído, realizan do previamente una comparación entre el dato guardado anteriormente en IN. MEM. con el dato que acaba de leerse; el se gundo almacena el resultado de dicha comparación en OUT. MEM. (sólamente en el modo de Verificación), incrementa la dirección de MEMORY ADDRESS REG. y establece el inicio de la operación de "control de post-lectura".

El control de post-lectura viene a ser una secuencia de conteo efectuada por medio de flip-flops, que toma inicio el momento en que ha atravezado por la estación lectora una colum na cualquiera de la tarjeta que está siendo leída.

El ciclo de memoria para la primera columna ocurre cuando el contador-sincronizador interno de UNIVAC alcanza la cuenta de 46 y los ciclos de memoria para las subsiguientes columnas ocurren cada vez que dicho contador alcanza la cuenta de 16.

Los ciclos básicos de memoria tercero y cuarto, son usados para generar 25 contabilizaciones adicionales de columnas lue go de que ya han sido leidas las 80 columnas de la tarjeta;

hasta que acabe de pasar ésta por la estación visible.

#### 1.4.3. SECUENCIA AUTOMATICA DE SALIDA DE DATOS

El momento en que se digita una de las teclas FEED ó EJECT, ocurre internamente en UNIVAC una secuencia que automáticamente transfiere todo el contenido de IN. MEM. a OUT. MEM., inicia la movilización de la tarjeta hacia la estación visible, luego continúa con su perforación, hasta acabar con la expulsión de la tarjeta hacia el cajetín de salida.

Dicha secuencia puede iniciarse automáticamente cuando UNI VAC se halla bajo el modo automático.

Se ha dividido a esta secuencia en cuatro fases que se des.criben a continuación.

a) La primera fase transfiere los datos de IN. MEM. ¿ OUT. MEM. para lo cual utiliza dos de los siete contadores bá sicos (flip-flops de conteo); y continúa ininterrumpidamente hasta que las 80 columnas han sido totalmente transferidas.

Esta fase opera en forma idéntica en los modos de Permon ración y de Verificación. Para la Interpretación, la trans ferencia puede darse desde IN. MEM. hacia OUTINEMEN. 1916 desde OUT. MEM. hacia OUT. MEM., dependiendo de la posición del switch PROGM/AUTO.

En el punto 1.5. se analiza a esta fase con más detenimiento.

b) La segunda fase se inicia inmediatamente después de com pletada la primera. Aquí, la tarjeta inicia su recorrido hacia la estación de lectura. La dirección del registro de salida es incrementada en uno cada vez que los contadores alcanzan la cuenta de 4. La dirección del registro de salida sirve a su vez de contador para determinar si una tarjeta se encuentra en la estación de lectura o no.

Esta fase se desarrolla a través de 4 ciclos básicos de memoria.

- c) La tercera fase sirve para sincronizar la perforación y la impresión de datos en la tarjeta que se desplaza a través de la estación visible. Los datos salen de OUT. MEM

- d) La cuarta y última fase toma lugar una vez finalizada la anterior. Sirve para remover la tarjeta desde la estación de perforación hasta el cajetín. Se desarrolla a través de 4 ciclos básicos de memoria.

# 1.5. PRIMERA FASE DE LA SECUENCIA AUTOMATICA DE SALIDA DE DATOS

Como ya se anotó, durante esta fase se vierte todo el contenido de la Memoria de Entrada en la Memoria de Salida.

Los datos van pasando uno a uno por entre los dos registros principales, en períodos predeterminados dentro de cada ciclo de memoria.

Se ofrece de esta manera una buena oportunidad para extraer datos o introducirlos en UNIVAC desde el Interfase, con el auxilio de algunas señales de sincronización provenientes de los registros que controlan esta fase.

Seguidamente se analiza más esta fase.

#### 1.5.1. FLUJO

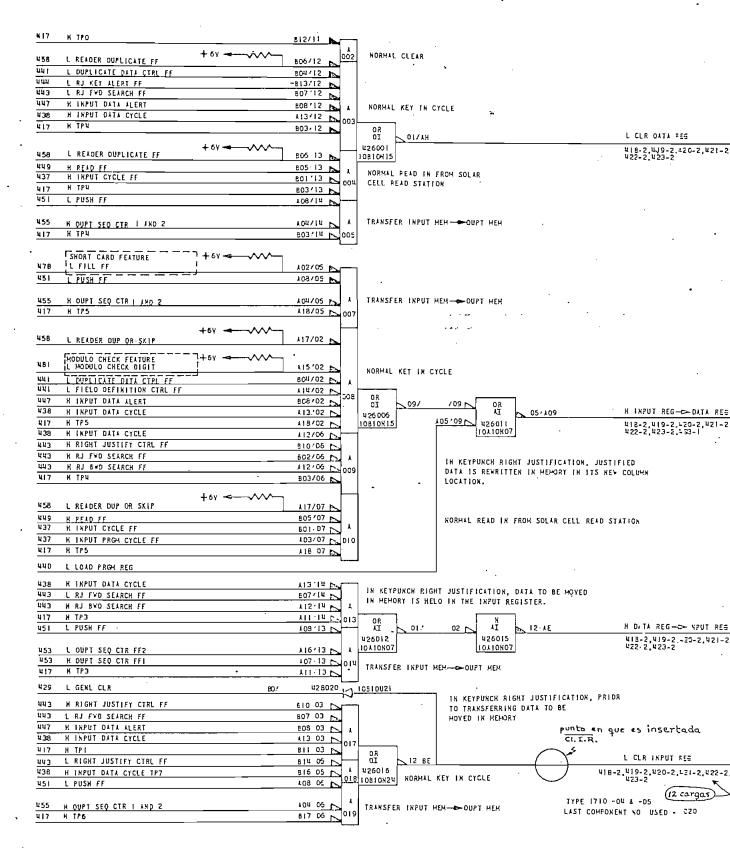

En la tabla 1.5.1. se describe el desarrollo de esta primera fase de la secuencia automática de salida, desarrollo que ha sido traducido en diagramas de bloques de más fácil comprensión, como se muestran en las figuras 1.5.1.1-2.

Los 10 diagramas ahí indicados equivalen a los 10 pasos que toman lugar durante esta fase; así:

|      | ,                                                                                                                         |                                                                                                                       |                                                                                |                                                                                                                                                                                                                  |                                                                                                                                       |                                                                                                                                       |

|------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

|      | 121 CICLE                                                                                                                 | 2MD CTCLE                                                                                                             | JRD CTCLE                                                                      | ASH CICLE                                                                                                                                                                                                        | FOOK THEYD CLCFE                                                                                                                      | DATA CYCLE                                                                                                                            |

| STA  | FEED OPERATION INITIATED BY<br>THE SETTIAN OF START OUR!<br>SEO FF (45);<br>ALL IMPUT OPERATIONS SUS-<br>PENOED (434-003) | ·                                                                                                                     | • .                                                                            |                                                                                                                                                                                                                  |                                                                                                                                       |                                                                                                                                       |

|      | DUPT SEO CIPS = ()<br>(452,453)                                                                                           | OUPT SEO CTAS = (1)<br>(452,453)                                                                                      | OUPT SED CTRS = (21)<br>(452,453)                                              | OUPT SEO CTRS = (2-)<br>(452,453)                                                                                                                                                                                | OUPT SEG CTR = (2-)<br>(452,453)<br>SET INPUT CICLE FF (437-011)                                                                      | OUPT SEC CTR = (<br>(457 453)<br>CLR INPUT CYCLE FF<br>CYCLE ILERT FF 15 C                                                            |

| T7 & |                                                                                                                           |                                                                                                                       |                                                                                |                                                                                                                                                                                                                  | (INITIATES LOOK AHEAD CTCLE)<br>(INITIATES ₩ER CTCLE<br>(403-004))                                                                    | CYCLE ALERT FF IS C<br>(437-010) AND THEN<br>10 FIRST CYCLE OF I<br>OR PERFORM AUTOMATI<br>OPERATIONS DETECTED<br>PREW LOOK AREAD CYC |

| TP 1 |                                                                                                                           | OUPT ADES REG TO MAR (407-027) (ADDRESSES INPUT WER FICEPT WHEN PREX SV SET TO PROX 1 DURING INTERPRET MODE (407-010) | OUFT ADRS REG TO MAR (4072-077) (ADDRESSES OUFT MEM (402-006)                  |                                                                                                                                                                                                                  | INPUT ADES REG TO MAR<br>(402-015)<br>CHECK PROF SW (430) FOR PROF<br>LOCATION (402-003)                                              |                                                                                                                                       |

| TF 2 |                                                                                                                           | GENERATE READ WEN'STROBE<br>(400-011)<br>IMPUT WEN TO DATA REG<br>(418 THRU 423)                                      | GENERATE READ BET STROBE<br>(403-011)                                          |                                                                                                                                                                                                                  | GENERATE READ MED STROBE (403-011) SELECTED PSCH MEN TO OATA MEG (418 THRU 423) AND PRCH MEG (438)                                    | _                                                                                                                                     |

|      |                                                                                                                           | DATA REG TO 1NPUT REG<br>(425-014)                                                                                    | INCREMENT DUPT ADRS REG<br>(415-004)                                           |                                                                                                                                                                                                                  |                                                                                                                                       |                                                                                                                                       |

| 17:3 |                                                                                                                           |                                                                                                                       |                                                                                |                                                                                                                                                                                                                  |                                                                                                                                       |                                                                                                                                       |

| T7 4 |                                                                                                                           |                                                                                                                       | CLR DATA REG (426-005)                                                         | RP NODE. INITIATE COL I PROM SEARCH THEN DUPT AD S REG = 1 (432-001) WHICK SETS INPUT CTCLE LLEFT FF (437-002) AND INPUT PROW CICLE FF (437-022)                                                                 |                                                                                                                                       |                                                                                                                                       |

| TP 5 |                                                                                                                           |                                                                                                                       | INPUT REC TO DATA REG<br>(426-007)                                             | CLR START DUST SEG FF SHEW<br>DUPT ADRS REG = 1 (451-003)                                                                                                                                                        | CIR PAGE OPERATIONAL CIRL . (441-001)                                                                                                 |                                                                                                                                       |

|      |                                                                                                                           |                                                                                                                       |                                                                                | SET PUSK FF THE" DUPT LORS                                                                                                                                                                                       | SENERATE *AITE *E* STROBE                                                                                                             | <u>.</u>                                                                                                                              |

| TPs  |                                                                                                                           | GENERATE WRITE WEM STROBE<br>(403-015)<br>(DATA TO IMPUT MER)                                                         | GENERATE WRITE NEW STROBE (403-015) (G1)A TC OUPT NEW) CLA IMPUT RES (425-015) | SEL TOSK IT THE SOUR AND AND ARE = 1 (451-019) ENERGITE THE PUNCH CLUTCH (476-009) AND ACTIVATE THE CARD PATTER (476-007)                                                                                        | COS-015) SET PROM OPERATIONAL CTRL (441) MHEX IN 4"/O MODE                                                                            |                                                                                                                                       |

| 17.7 | SET OUPT SEG CIR FF 1 AT<br>1 L. DI TF 7 (451-005.453-<br>016)<br>INITIATE RER CYCLE (403-<br>002)                        | SET DUP! SED CTR FF 2 AT<br>1.C DF TF 7 (454-005,<br>453-012)<br>CONTINUE ET = CYCLE                                  | CLR OUF1 SED CTR FF   AT<br>T.E. OF TP 7 (454-005.<br>453-015)                 | CLR DUPT SFO CTR FF 2 AT 1.E. OF TF 7 (454-005) 457-011) 17 PUSH FF IS CLEIRED FRO- CECO TO FIRST CTCLE OF THIS PHISE IF PUSH FIS SET. UUPT SED CTR FF 7 REMINS SET IND INK LODE, MALO CTCLE OF THIS FASE OCCURS | CLR IMPUT PROV CICLE FF AT<br>TE OF TP 7 (437-012)<br>CLR IMPUT CICLE ALEAT FF IF<br>TIELD DEFINITION CTRL FF IS<br>CLEARED (437-005) |                                                                                                                                       |

Tabla 1.5.1. Primera fase de la Operación Automática de Sal $\underline{i}$  da de Datos.

#### 1.5.2. PERIODOS IMPORTANTES

De entre los diez pasos anteriores, el décimo presta mayor facilidad para la transferencia de datos. Es en este momen to en que se escriben los datos en la Memoria de Salida.

Si el modo en que se encuentra UNIVAC es el de perforación, dichos datos son perforados en tarjetas; si se encuentra en el modo de carga de datos, entonces dichos datos son los que fueron leídos de la tarjeta anterior y almacenados en la Memoria de Entrada. Así pues, este paso (10) es tomado muy en cuenta para el diseño del Interfase.

Para el caso de introducción de datos desde el Interfase ha cia el Registro de Datos, es necesario que este registro se encuentre previamente borrado (todos sus bits iguales a ce ro) con el fin de evitar "choques" o interferencias entre da tos diferentes. Este borrado deberá ser efectuado artificial mente por el Interfase, ya que como se ha visto, queda car gado este registro con el contenido de la Memoria de Entra da en el paso 10.

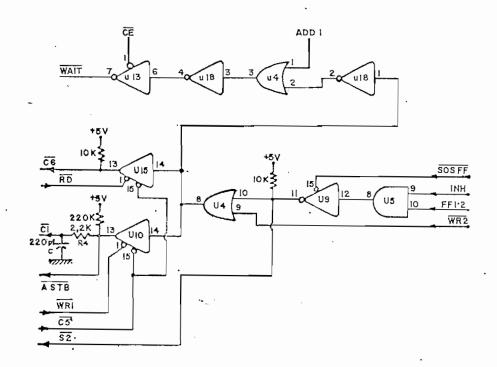

El período en que se tiene mayor facilidad para conseguir - el borrado del Registro de Datos cuando se desea introducir nuevos datos a través del Interfase, viene a ser el sexto (TP6 en la tabla 1.5.1.). Este período contiene a los pasos 4 y 10.

Durante este período se puede lograr el mencionado borrado sin alterar significativamente la normal realización de to da la secuencia, cosa que entrañaría mucho riesgo.

Si en el paso 4 se produjera el borrado del Registro de  $E_{\underline{n}}$  trada como se produce en el paso 10, entonces se obtendría en definitiva el borrado del Registro de Datos en el paso 10, como puede deducirse de la figura 1.5.1.2.

Para el caso de lectura de datos desde UNIVAC hacia el Interfase, no hace falta efectuar este borrado ni ninguna otra operación adicional.

# 1.6. <u>DIAGRAMA DE TIEMPOS</u>

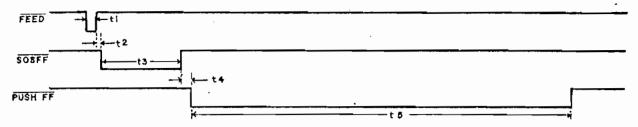

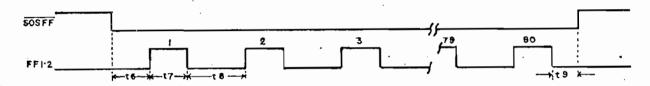

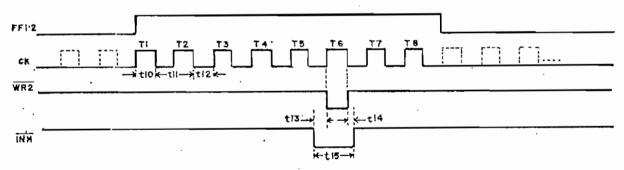

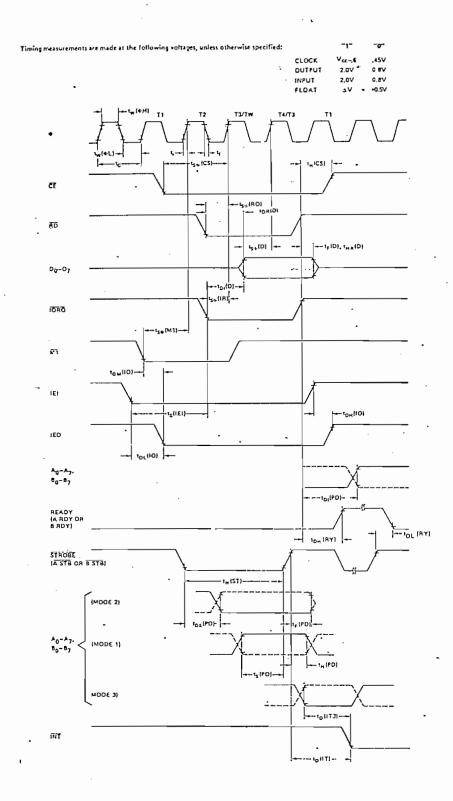

Los períodos y ciclos básicos de memoria a los que se hacia referencia en los puntos anteriores, pueden visualizarse en forma más clara en la figura 1.6.

En esa figura se tiene en la parte superior a la señal maes tra de reloj de UNIVAC denominada "H CLOCK", la cual es ge nerada por un circuito oscilador de frecuencia igual a 200 KHz. Este oscilador entrega pulsos cuadrados de 5 µseg. de período.

Un tren de 8 pulsos -desde tO hasta t7- constituye un "cí-

Inicio (FEED), desarrollo de la Primera Fase (SOSFF) y de las Fases 2-3 y 4 (PUSH FF) de la Secuencia Automática de Salida de Datos.

Desarrollo de la Primera Fase mostrando los Terceros Ciclos Básicos de memoria (FF1.2)

Tercer Cicio Básico de Memoria y escritura del dato en memoria (WR2)

$$t_1 \simeq 0.5 \ \mu s$$

$t_6 = 80 \ \mu s$   $t_{11} = 5 \ \mu s$   $t_2 = 0.03 \ \mu s$   $t_7 = 40 \ \mu s$   $t_{12} = 2.5 \ \mu s$   $t_3 = 12.79 \ ms$   $t_8 = 120 \ \mu s$   $t_{13} = 2.2 \ \mu s$   $t_4 = 5 \ \mu s$   $t_9 = 25 \ \mu s$   $t_{14} = 0.3 \ \mu s$   $t_5 \simeq 1.1 \ s$   $t_{10} = 2.5 \ \mu s$

Figuras 1.6.2. Diagrama de tiempos de ciertas señales generadas en la S $\underline{e}$  cuencia Automática de Salida de Datos de UNIVAC.

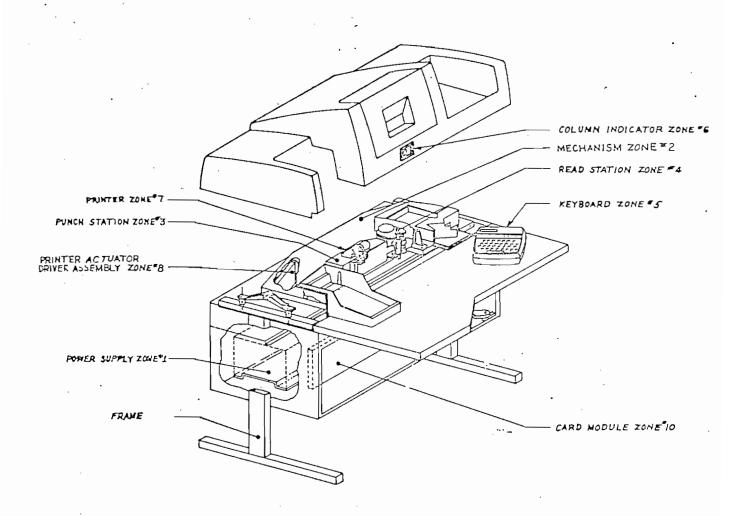

#### 1.7.1. ZONAS DE LA MAQUINA

Se muestran en la figura 1.7.1. En la zona 10 o "Módulo de  $Placas"^*$  es donde van a centrarse las conexiones del Interfase.

Figura 1.7.1. Localización de las zonas de la máquina UNIVAC 1710

<sup>\*</sup> Placas o cartas conteniendo a los circuitos electrónicos en este caso.

#### 1.7.2. UBICACION DE LAS PLACAS

La ubicación de las placas dentro del Módulo, así como el fun cionamiento específico de cada una de ellas, se muestra en la figura 1.7.2. Las placas encerradas en líneas cortadas son

| 1<br>2<br>3<br>4<br>5<br>6<br>7 | KEYEQARD C-BLE  UPPER: EYEN PUNCH CABLE  UPPER: ODD PUNCH CABLE  UPPER: COLUMN INDICATOR CABLE  UPPER: COLUMN INDICATOR CABLE  [3616924 SHORT CARD FEATURE] |  |  |  |  |  |  |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 3<br>4<br>5                     | UPPER: ODD PUNCH CABLE  UPPER: COLUMN INDICATOR CABLE  LOWER: PRINTER CABLE  3616924 SHORT CARD FEATURE                                                     |  |  |  |  |  |  |

| ц<br>5<br>6                     | UPPER: COLUMN INDICATOR CABLE LOWER: PRINTER CABLE                                                                                                          |  |  |  |  |  |  |

| 5<br>6                          | 3616924 SHORT CARD FEATURE                                                                                                                                  |  |  |  |  |  |  |

| 6                               | <del></del>                                                                                                                                                 |  |  |  |  |  |  |

|                                 | 6 3616906 INPUT. DATA, PUNCH REGISTERS (7-8-9)                                                                                                              |  |  |  |  |  |  |

| 7                               |                                                                                                                                                             |  |  |  |  |  |  |

|                                 | 3616906 INPUT, DATA, PUNCH REGISTERS (1-2-3)                                                                                                                |  |  |  |  |  |  |

| 8                               | 3616906 INPUT, DATA, PUNCH REGISTERS (0-5-6)                                                                                                                |  |  |  |  |  |  |

| . 9                             | 3616006 INPUT, DATA, PUNCH REGISTERS (12-11-4)                                                                                                              |  |  |  |  |  |  |

| 10                              | 5030394 DATA PATH CONTROLS                                                                                                                                  |  |  |  |  |  |  |

| 11                              | 3616502 MEMORY TIMING AND DRIVE                                                                                                                             |  |  |  |  |  |  |

| . 12                            | 3616501 MEMORY SENSE AND INHIBIT (9-16)                                                                                                                     |  |  |  |  |  |  |

| 13                              | 3616500 MEMORY STORAGE HODULE                                                                                                                               |  |  |  |  |  |  |

| 14                              | 3616501 HEMORY SENSE AND INHIBIT (1-8)                                                                                                                      |  |  |  |  |  |  |

| 15                              | 5030368 RIGHT JUSTIFY EKSP. SGL COL                                                                                                                         |  |  |  |  |  |  |

| 16                              | 5030588 OPERATIONAL CONTROLS                                                                                                                                |  |  |  |  |  |  |

| 17                              | 5030826 INTERSPERSED FEATURE                                                                                                                                |  |  |  |  |  |  |

| . 18                            | 23T49 Y11T2UL TK91R 8E30E04                                                                                                                                 |  |  |  |  |  |  |

| 19                              | 5030379 DATA ENTRY CONTROLS                                                                                                                                 |  |  |  |  |  |  |

| 20                              | 5032152 YERIFICATION ERROR CTRL. CLICK                                                                                                                      |  |  |  |  |  |  |

| . 21                            | 5030821 KB SPT. READ SPT. START O. S. C.                                                                                                                    |  |  |  |  |  |  |

| 22                              | 5030370 PROGRAM CONTROL                                                                                                                                     |  |  |  |  |  |  |

| 23                              | 5030324 TIMING                                                                                                                                              |  |  |  |  |  |  |

| 24                              | 3618174 PTR. SPT PRT RELAY DOD EVEN                                                                                                                         |  |  |  |  |  |  |

| . 25                            | 3615163 KE FEED, PUNCH CONTROL                                                                                                                              |  |  |  |  |  |  |

| 26                              | 3516905 OUPT SEQ CTR 1-4. AUX IN CTRLS                                                                                                                      |  |  |  |  |  |  |

| 27                              | 5030375 HEH. SEL. SHIFT, ADV. PATTER                                                                                                                        |  |  |  |  |  |  |

| 28                              | 3617485 FEED, INTERLOCK, PHOTOCELLS                                                                                                                         |  |  |  |  |  |  |

| 29                              | 3516917 CLUTCH, BRAKE, EJECT, PADDLE                                                                                                                        |  |  |  |  |  |  |

| 30                              | 3618161 OUTPUT SEQUENCE COUNTER 5-7                                                                                                                         |  |  |  |  |  |  |

| 31                              | 3616902 UNITS ADDRESS RIGISTER .                                                                                                                            |  |  |  |  |  |  |

| 32                              | 3616903 TENS ADDRESS REGISTER                                                                                                                               |  |  |  |  |  |  |

| 33                              | 3615922 OUTPUT ADDRESS REGISTER                                                                                                                             |  |  |  |  |  |  |

| 34                              | 3616926 READ CTRL, OUPT ADRS REG CTRL                                                                                                                       |  |  |  |  |  |  |

| 35                              | 5032382 PRINT CONTROLS AND DELAYS (ODD)                                                                                                                     |  |  |  |  |  |  |

| 36                              | 5032382 PRINT CONTROLS AND DELAYS (EYEN)                                                                                                                    |  |  |  |  |  |  |

| . 37                            | 3616921 PRINTER COMPARITOR (000)                                                                                                                            |  |  |  |  |  |  |

| . 38                            | 3616921 FRINTER COMPARITOR (EVEN)                                                                                                                           |  |  |  |  |  |  |

| 39                              | 3616929 PTR XLATE, DATA REC 0, PUN FF                                                                                                                       |  |  |  |  |  |  |

| 40.                             | 3616930 PTR CTR. CONSTANT DATA CTRLS                                                                                                                        |  |  |  |  |  |  |

| 41                              | 3618162 READ CTR. INTERPRET CONTROLS                                                                                                                        |  |  |  |  |  |  |

| Ч2                              | 361816B OUTPUT CTRLS                                                                                                                                        |  |  |  |  |  |  |

| . 43                            | 3618158 POD CHECK ACCUMULATOR, CONTROLS                                                                                                                     |  |  |  |  |  |  |

| ដូច                             | 3618166 POD CHECK MULTIPLICAND, CONTROLS                                                                                                                    |  |  |  |  |  |  |

| ¥5°                             | 3618149 HOD CHECK MULTIPLIER, CONTROLS                                                                                                                      |  |  |  |  |  |  |

| 46                              | 3618152 (3616933) MOD 10 (11) CHECK DIGIT DUTPUT                                                                                                            |  |  |  |  |  |  |

| ¥7                              | F E.O. DIACNOSTIC MODULE LOCATION A                                                                                                                         |  |  |  |  |  |  |

| пв                              | F.E.D. DIAGNOSTIC MODULE LOCATION B                                                                                                                         |  |  |  |  |  |  |

Figura 1.7.2. Ubicación de las Tarjetas en el "Bus"

opcionales, esto es, pueden ser insertadas o no en el "bus" del Módulo y cumplen funciones especiales.

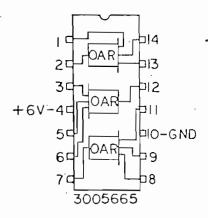

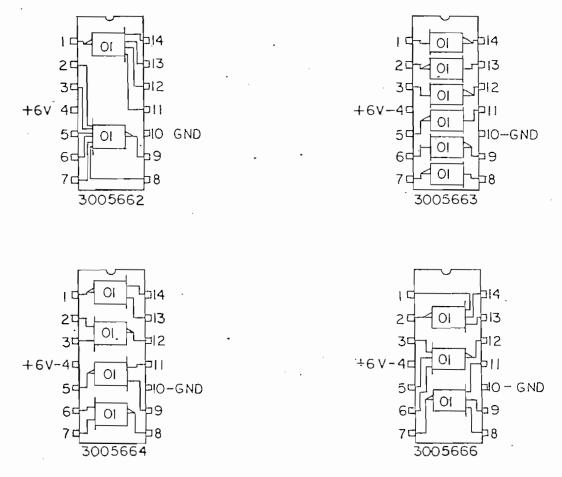

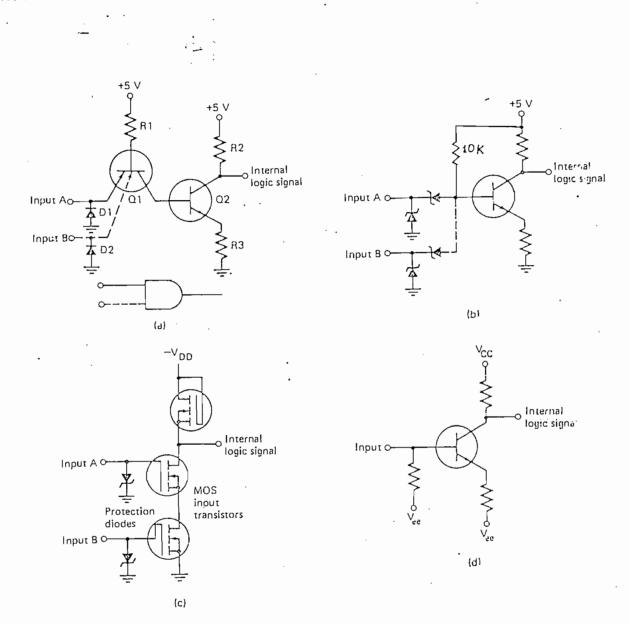

#### 1.7.3. CLASES DE ELEMENTOS

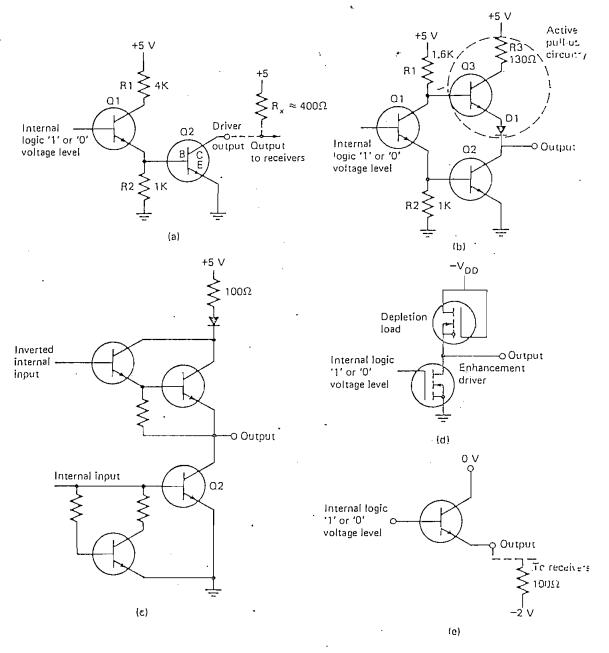

En las placas se tienen circuitos discretos e integrados. Los circuitos integrados son casi en su totalidad de la primera generación, es decir, son construídos en base a la tecnología RTL (Resistor Transistor Logic).

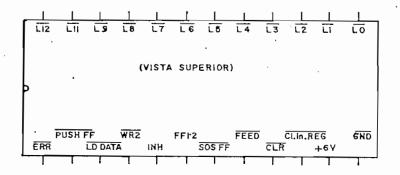

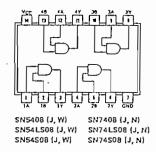

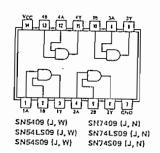

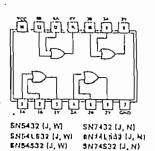

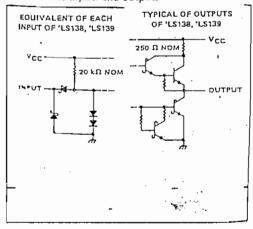

Los seis tipos fundamentales de "chips"\* que existen en UNI VAC se muestran en la figura 1.7.3.1. Nótense los pines de alimentación  $V_{CC}$  y GND; así también el valor de  $V_{CC}$  = +6 V.

<sup>\* &</sup>quot;chips"., I.C., o circuitos integrados, son palabras que se usan indistintamente.

NOTE: I. ALL SCHEMATICS ARE SHOWN TOP VIEW

Figura 1.7.3.1. Clases de circuitos integrados utilizados en UNIVAC

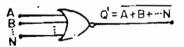

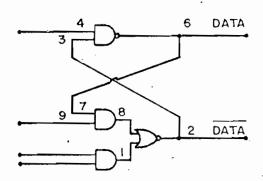

Los bloques nominados "OI" que se aprecian en dicha figura, tienen su equivalencia en una compuerta NOR - ver figuras 1.7.3.2 y 1.7.3.3.

Figura 1.7.3.2. Circuito equivalente al bloque OI

Figura 1.7.3.3. Compuerta NOR equivalente al circuito anterior.

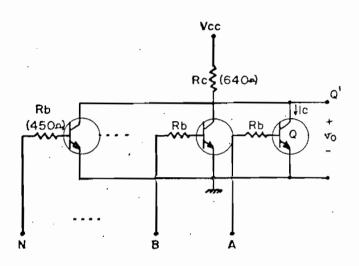

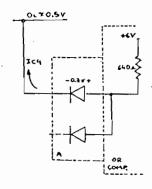

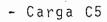

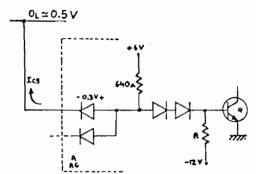

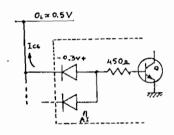

# 1.7.4. TECNOLOGIA RTL Y NIVELES LOGICOS

Como se ha visto, los chips de UNIVAC giran en torno al transistor y la resistencia.

Se han tratado de obtener en forma experimental los valores

numéricos del circuito equivalente al bloque OI de la figura 1.7.3.1. llegándose a la conclusión -ya expuesta- de que se trata de un circuito perteneciente a la tecnología RTL y con valores de resistencias aproximados a los que se encuentran entre paréntesis en la figura 1.7.3.2.

El valor de los niveles lógicos teóricamente es:

Los valores de corrientes se mantienen relativamente altos en comparación con los de la tecnología TTL utilizada más comunmente.

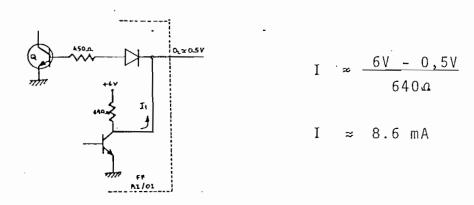

De la figura 1.7.3.2., para Q en saturación - ON - :

$$I_{c} = \frac{V_{cc} - V_{ce}}{R_{c}}$$

$$I_C \simeq \frac{6V - 0.15V}{640}$$

$$I_C \simeq 9.1 \text{ mA}$$

para Q abierto - OFF -:  $I_C \simeq 0 \text{ mA}$

De algunas mediciones realizadas dentro de las placas en ple

no funcionamiento, se han sacado en promedio los siguientes resultados:

$$5.7V \le V_{OH} \le 5.9V$$

$7 \text{ mA} \le I_{OH} \le 12 \text{ mA}$

$0.1V \le V_{OL} \le 0.2V$

$--- \le I_{OL} \le ---$

Las diferentes funciones aritmético-lógicas que efectúan las compuertas AND, CR, NAND; las funciones de los flip-flops, registros, etc., son realizadas por circuitos construidos sóla mente en base a los chips mencionados, conectándose a ellos elementos discretos externos como son resistencias, diodos y condensadores.

Puede anotarse que, utilizando la tecnología TTL por ejemplo, podría reducirse considerablemente el número de placas, el consumo de potencia y además, simplificarse mucho su construcción.

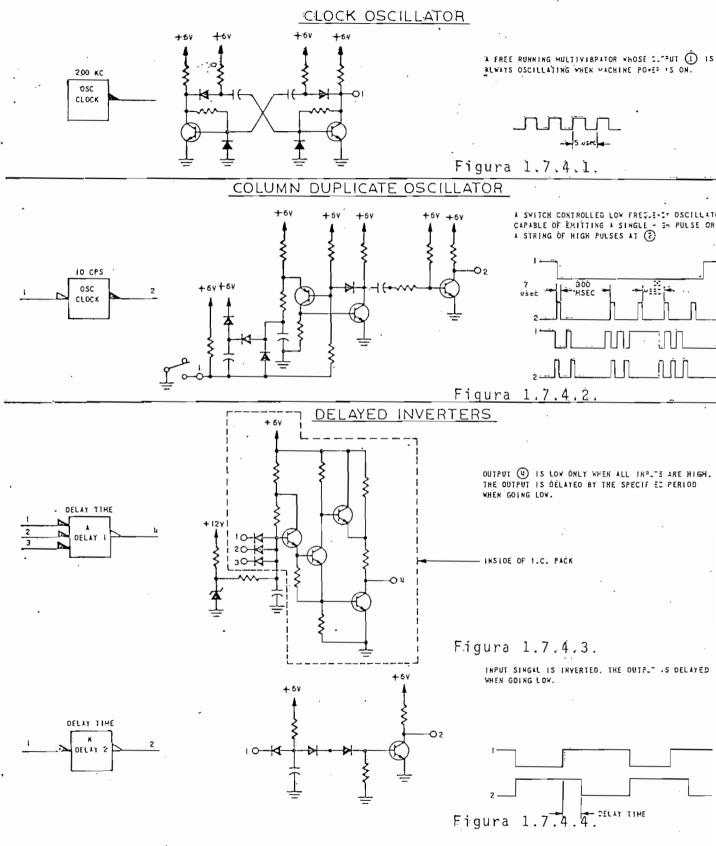

Los circuitos que conforman al "oscilador-reloj maestro", al "oscilador secundario para duplicación automática de columnas" y a los "inversores con tiempos de retardo" largo y corto, se dan a continuación.

Elementos usados en UNIVAC

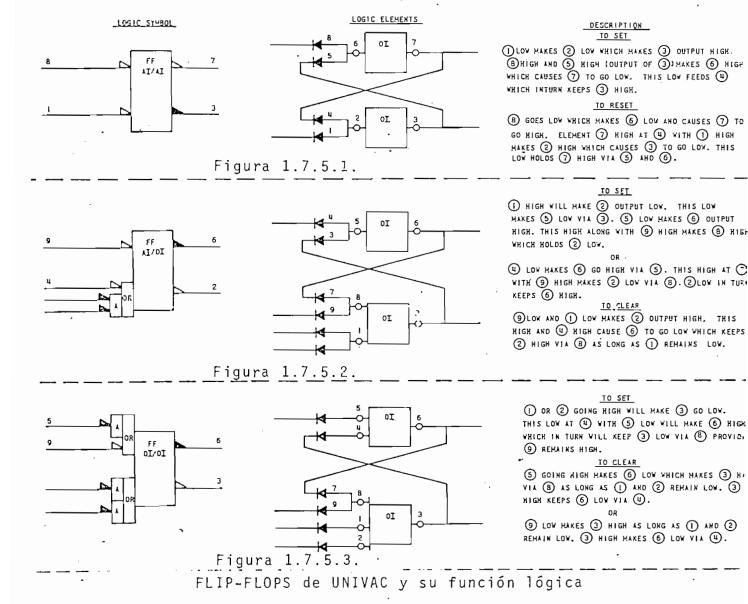

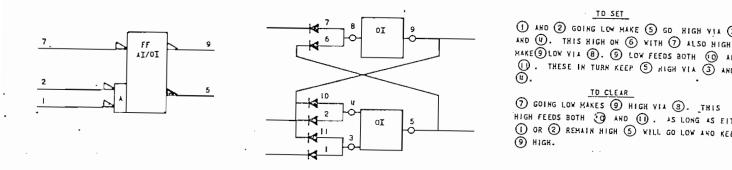

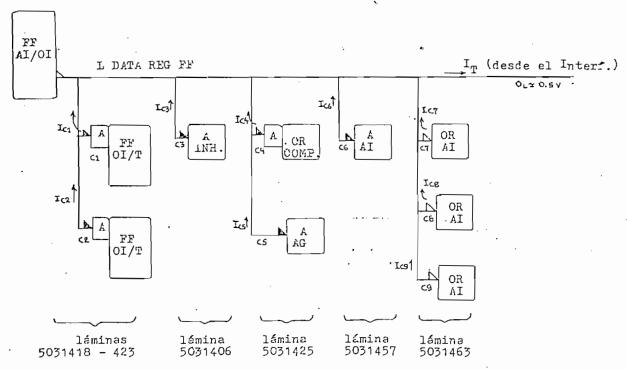

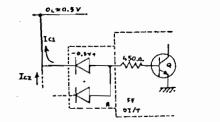

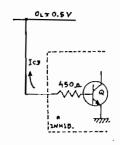

#### 1.7.5. FLIP - FLOPS

Como se aprecia en las figuras 1.7.5.1-4, los flip - flops son construídos a partir de los chips mencionados, con algunos diodos externos conectados a sus pines.

El flip-flop FF AI/OI de la figura 1.7.5.2., es utilizado para formar los Registros de Datos y de Entrada.

Figura 1.7.5.4. FLIP-FLOPS de UNIVAC y su función lógica

Se explica a continuación su funcionamiento con más detalle. Para ello se ha dibujado un circuito equivalente al flip-flop, que utiliza compuertas AND, NAND y NOR.

Figura 1.7.5.5. Circuito equivalente al flip-flop de la figura 1.7.5.2.

- a) Para poner en DATA un 1 lógico:

- Poner en las lineas 1 y 9 un 1 lógico; cualquier trans<u>i</u>

ción posterior no afectará el estado del flip-flop.

- Otra forma es poner en 9 un 1 lógico y efectuar una tra $\underline{n}$  sición positiva en 4.

- . Si pasa 9 desde 1 lógico a 0 lógico cuando 1 está en bajo, puede cambiar el estado del flip-flop.

- b) Para poner en DATA un O lógico:

- Poner la linea 1 en O lógico, 4 en 1 lógico y efectuar  $\underline{u}$  na transición positiva en 9.

Cambia el estado del flip-flop con el cambio de cualquie ra de las lineas 1 o 4.

En resumen, para "cargar artificialmente" un dato en el flipflop, debe observarse lo siguiente:

Si se desea poner en DATA un 1 lógico, puede conseguirse és to simplemente haciendo que la línea 2 alcance un nivel de voltage correspondiente a 0 lógico; para cualquier estado previo del flip-flop.

En cambio, para poner en DATA un O lógico, deberán cumplirse ciertas condiciones previas en algunas líneas del flip-flop,

lo cual complica esta operación.

Por ello es conveniente <u>poner</u> <u>sólamente</u> <u>los datos correspondientes a l lógico</u>, <u>borrando previamente el contenido</u> <u>del flip-flop</u>, para evitar el caso de que éste posea un l lógico en DATA sin que se haya escrito ningún dato desde el exterior.

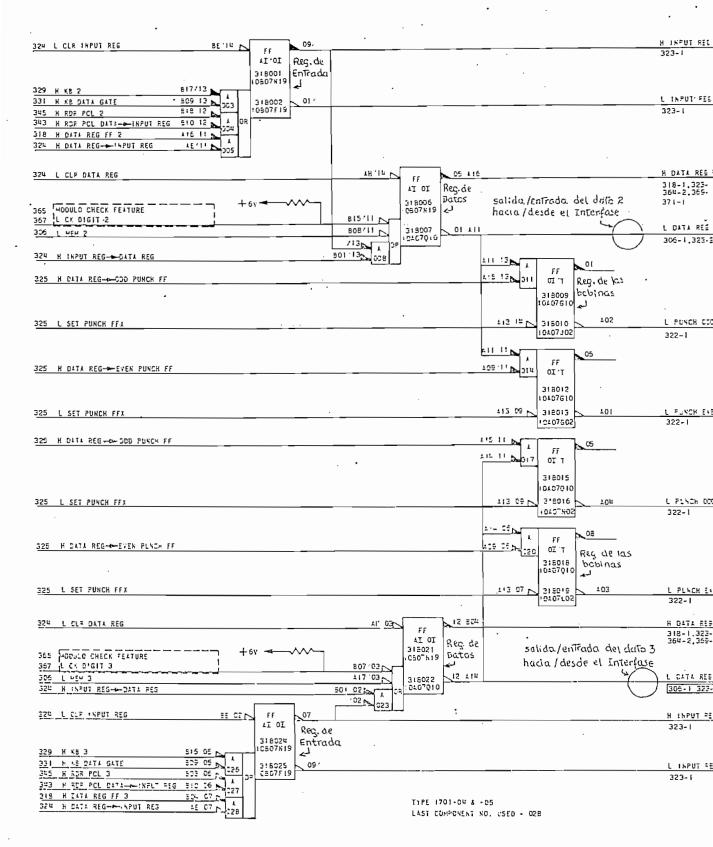

#### 1.7.6. REPRESENTACION EN LAS LAMINAS DEL MANUAL

Todos los elementos existentes en UNIVAC son perfectamente identificados en las láminas del Manual de Servicio. Esta identificación incluye, como se encuentra indicado en las figuras 1.7.6.1-3, los siguientes aspectos:

- tipo de elemento; dado por el grupo de letras mayúsculas que están en la parte superior del bloque;

- número de la lámina en que se halla dibujado; que son los 3 números de la izquierda ubicados bajo el grupo de letras mencionado anteriormente;

- número con el que consta dentro de dicha lámina; que son los 3 números a continuación de los anteriores;

- su ubicación física en la máquina, dado por los siguientes items:

narlo con los niveles activos de las demás líneas que entran o salen del elemento.

Low

► Hi

- Los dos grupos de letras y números a la entrada de un bloque, señalan el pin correspondiente en la tarjeta y el pin del chip; de igual manera con las letras y números ubicados a la salida del bloque.

Para concluir este capítulo, cabe decir que se ha logrado  $\underline{a}$  barcar en éste lo más útil en lo que concierne al sistema  $\underline{e}$  léctrico y a la estructuración de UNIVAC; sin topar el aspe $\underline{c}$  to mecánico.

Lo escrito hasta aquí, permite proseguir con certeza en el logro del Interfase con UNIVAC. Toca seguidamente hacer lo propio con el microprocesador Z-80.

# CAPIIULQ II

# <u>ESTUDIO DEL MICROPROCESADOR Z-80 DESDE EL PUNTO DE VISTA DE</u> INTERFASES

El microprocesador Z-80\* es en materia de microprocesadores, uno de los más avanzados que se han construído últimamente..

Su diseño parte del microprocesador INTEL 8080 poseyendo sin embargo sobre éste, muchas ventajas, así:

- 158 instrucciones básicas;

- frecuencia de reloj de hasta 4.5 MHz en el modelo Z-80A;

- 5 líneas dedicadas a la comunicación con sistemas perifér $\underline{i}$  co;

- alimentación simple de 5 V/90 mA;

- capacidad de realizar el "refresh" o refresco para memorias dinámicas;

- excelentes soportes en software como en hardware; etc.

- \* En realidad se ha realizado en la práctica el Interfase con Z-80A que es la versión más veloz del Z-80 aunque en todo lo demás muy similar a este.

La capacidad que tiene Z80-CPU para aceptar interfases es a $\underline{m}$  pliada enormemente por la serie de chips que se han constru $\underline{i}$  do expresamente para tal fin y que se describen en el punto 2.4.

Un estudio a fondo de este microprocesador no viene al caso, mas bien se ha pretendido dar en este capítulo una somera visión de cómo se podría utilizar a Z80-CPU en el diseño y construcción de Interfases.

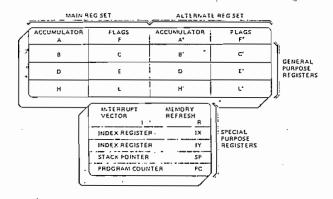

En el anexo, punto A.2.3, se incluyen las 158 instrucciones b $\underline{\acute{a}}$  sicas de Z80-CPU y otros datos de importancia. De esta forma, este capítulo se dedica únicamente al aspecto del hardware.

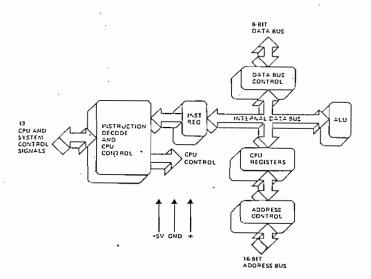

Figura 2.a. Diagrama en bloques de Z80-CPU

Figura 2.b. Los 22 registros de Z80-CPU

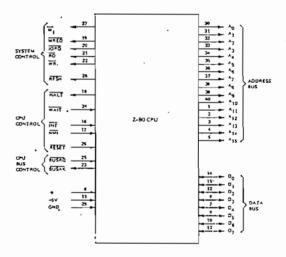

#### 2.1. DESCRIPCION DE LOS PINES DE Z80-CPU

La descripción de los pines que tiene el chip Z80-CPU ofrece rá una idea panorámica de los dotes de este microprocesador al mismo tiempo que un conocimiento certero sobre la natura leza de las señales que entran y salen de él, de manera que se tendría ya la información suficiente para juzgar cuáles se ñales podrían ser utilizadas en el Interfase y cuáles son sus garacterísticas funcionales.

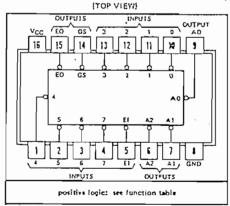

Los 40 pines o patas que posee el circuito integrado Z80-CPU se muestran en las figuras 2.1.1-2. En ellas se indica la no tación de cada una de las 40 señales de entrada/salida de CPU así como también el número de pin que ocupan.

Figura 2.1.1. El circuito integrado Z80-CPU

Figura 2.1.2. Pines de Z80-CPU agrupados según sus funciones

Seguidamente se explican las señales:

- AO-A15 : (address Bus); son 16 líneas que constituyen la vara o bus de direccionamiento de 16 bits en parallelo con una capacidad de hasta 64Kbytes de direc

cionamiento directo de memoria.

Son lineas "tristate"\* de salida de CPU y lógica positiva - se activan en "High" (ver  $V_{OH}$  en la table 2.2.1.1) - .

- DO-D7 (Data Bus); son 8 líneas que constituyen la vara de datos. Sirven para el intercambio de palabras (bytes) de 8 bits con memoria y/o periféricos.

Son líneas tristate bidireccionales y de lógica positiva.

- M1 (Machine Cycle one); indica que el ciclo de máquina que está tomando lugar cuando se activa -se pone en "Low" (ver Vol en la tabla 2.2.1.1)- es el correspondiente al inicio de una nueva instrucción.

La señal sale de CPU y tiene lógica negativa.

-  $\overline{\text{MREQ}}$  (Memory Request); indica que la vara de direccionamien

<sup>\*</sup> Las palabras "tristate" o "three-states" se usan para indicar que la  $1\dot{1}$  nea o pin que sale del chip puede pasar a un estado de alta impedancia (high Z) que no es ni  $1_{\rm L}$  ni  $0_{\rm L}$ .

to posee una dirección válida para la lectura o e<u>s</u> critura en memoria.

Es tristate, de salida de CPU y lógica negativa.

- TORQ (Input/Output Request); indica que la mitad inferior de la vara de direccionamiento contiene una di rección válida de entrada/salida para una operación de lectura o escritura en algún terminal periférico\*. Se activa también cuando una interrupción está siendo reconocida, para indicar que puede ser colocado en la vara de datos un vector de respuesta a interrupciones.

Es tristate, de salida de CPU y lógica negativa.

- RD (Memory Read); indica que CPU se dispone a leer un dato desde la memoria o desde algún periférico (es ta línea debería ser utilizada para realizar la habilitación del elemento requerido).

Es tristate, de salida de CPU y lógica negativa.

-  $\overline{WR}$  (Memory Write); indica que la vara de datos conti<u>e</u>

<sup>\*</sup> Pueden estar conectados hasta 256 (28) terminales periféricos:

ne un dato válido para ser almacenado en memoría ó escrito en algún periférico.

Es tristate, de salida de CPU y lógica negativa...

- RFSH (Refresh); indica que los 7 bits inferiores de la vara de direccionamiento contienen una dirección de memoria que va a ser "refrescada"\* y que la señal-MREQ debería ser usada para realizar una lectura de refresco a todas las memorias dinámicas.

La señal sale de CPU y tiene lógica negativa.

HALT (Halt state); indica que CPU ha ejecutado una instrucción dada por software de "alto" ("Halt") y que se encuentra aguardando una interrupción "no enmas canada" (cuando la máscara está habilitada) antes que la operación pueda concluirse. Mientras está aguardando, CPU ejecuta ciclos de "no-operación" para mantener la actividad del negresh o refresco de memorias:

La señal sale de CPU y tiene lógica negativa.

<sup>\*</sup> esto es, los mismos datos son sobreescritos para evitar su pérdida (oca sionada en las memorias dinámicas por una degradación de sus niveles a lo largo del tiempo).

- WAIT

(Wait); indica a Z80-CPU que la memoria o periféri co direccionado no se encuentra listo para la transferencia de datos. CPU entonces entra a un estado de espera que durará tanto como dure la actividad de ésta y durante todo este tiempo no podrá ejecutar ninguna operación.

La señal entra en CPU y tiene lógica negativa.

- <u>INT</u>

(Interrupt Request); esta señal es generada por al gún periférico y es atendida al término de la instrucción que está siendo ejecutada si el "flip-flop de habilitación de interrupciones controlado por software" se encuentra habilitado y la señal de BUSRQ no está activada.

La señal INT entra en CPU y tiene lógica negativa.

- NMI

(Non Maskable Interrupt); esta señal tiene mayor prioridad que INT y es siempre reconocida al final de la instrucción en curso, independientemente del status del flip-flop de habilitación de interrupciones. Cuando esta señal ha ocurrido, Z80-CPU se ubica automáticamente en la localidad 0066<sub>H</sub>.

La señal entra en CPU y tiene lógica negativa.

- RESET (Reset); señal que inicializa a CPU de la siguiente manera:

- vuelve a su estado original al flip-flop de habilitación de interrupciones;

- encera al contador del programa (registro PC), así como a los registros I y R;-y

- pone el modo de interrupción como en 8080A.

Durante el tiempo de "reset", las varas de datos y direccionamiento pasan a un estado de alta impedan cia y todas las señales de control que salen de CPU pasan al estado inactivo, de suerte que otros periféricos puedan ganar el control de estas varas y señales.

La señal RESET entra en CPU y tiene lógica negativa.

- BUSRQ (Bus Request); es usada cuando algún periférico ne cesita ganar el control de las varas de datos y cireccionamiento así como también de las señales de control tristate de salida. Todas ellas pasan a un estado de alta impedancia cuando esta señal se ha activado.

La señal entra en CPU y tiene lógica negativa.

- BUSAK (Bus Acknowledge); es la señal de reconocimiento de CPU que sirve para indicar al periférico que ha activado la línea BUSRQ, que en ese momento se encuentran ya las varas en su estado de alta impedancia y que el periférico puede empezar a controlarlas.

La señal sale de CPU y tiene lógica negativa.

- $\phi$  (Clock); es la señal de reloj que debe ser introde ducida a CPU hasta 4.5 MHz para Z-80A -.

- +5V, GND son las señales de alimentación del chip.

Hasta aqui la descripción de los 40 pines de Z80-CPU en su parte funcional. Empero, es necesario además saber sus carac terísticas eléctricas y rangos máximos para sus conexiones. Esto se precisa en el siguiente punto.

# 2.2. CARACTERISTICAS ELECTRICAS

Para completar el estudio iniciado sobre los pines de Z80 - CPU, es indispensable, sobre todo si se lo enfoca desde el punto de vista de la construcción del Interfase, el poseer la necesaria seguridad en el plano eléctrico, es decir, ana lizar las características eléctricas, rangos mínimos, máxi

mos y típicos y, en lo posible, tolerancias y capacitancias en la carga.

Como se entenderá, este análisis hecho cabalmente podría ll<u>e</u> var muchas páginas; pero puede también hacerse en forma co<u>n</u> cisa, agrupando a los principales parámetros con sus rangos, en cuadros que sean válidos para cualesquiera de los 40 pines que posee Z80-CPU.

En lo que se refiere a las características eléctricas que poseen los pines, éstas pueden ser agrupadas en:

- a) Características en DC o para el estado estable;

- b) características en AC o para el estado transitorio.

#### 2.2.1. CARACTERISTICAS EN DC

Las características en DC para Z80-CPU se resumen en la ta bla 2.2.1.1 en la que pueden observarse también los rangos mínimos, típicos y máximos.

Los diferentes parámetros voltamperimétricos de los pines de Z80-CPU resultan ser totalmente compatibles con los niveles TTL. Los pines, sin embargo, poseen un reducido "{an-out"\*

<sup>\*</sup> El "fan-out" es una característica de los IC's que da el número máx $\underline{i}$  mo de circuitos similares que pueden ser alimentados por una misma  $\underline{i}$  nea de salida.

# Absolute Maximum Ratings

Temperature Under Bias Storage Temperature Voltage On Any Pin with Respect to Ground Power Dissipation 0°C 10 70°C -65°C 10 +150°C -0.3V 10 +7V

1.5 W

11 250 mA para 280A 12 250 neeg, pora 2-80A

#### \*Comment

Stresses above those listed under "Absolute Maximum Rating" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may after device reliability.

#### D.C. Characteristics

TA = 0°C to 70°C. Vcc = 5V = 5% unless otherwise specified

| Symbol           | Parameter .                               | Min.                | Тур. | Max.            | Unit | Test Condition                           |

|------------------|-------------------------------------------|---------------------|------|-----------------|------|------------------------------------------|

| VILC             | Clock Input Low Voltage                   | -0.3                |      | 0.45            | ٧    |                                          |

| , AIHC           | Clock Input High Voltage                  | V <sub>ce</sub> [1] |      | V <sub>cc</sub> | ٧    |                                          |

| v <sub>IL</sub>  | Input Low Voltage                         | -0.3                |      | 0.8             | ν    |                                          |

| v <sub>IH</sub>  | Input High Voltage                        | 2.0                 | •    | Vec             | ٧    |                                          |

| <sup>V</sup> OL  | Output Low Voltage                        |                     |      | 0,4             | V    | l <sub>OL</sub> =1.5mA                   |

| V <sub>OH</sub>  | Output High Voltage                       | 2.4                 |      |                 | v    | l <sub>OH</sub> = -100μ <sub>A</sub> t   |

| lcc              | Power Supply Current                      |                     | 90   | 200             | nιA  | t <sub>c</sub> = 400nsec 12              |

| I <sub>LI</sub>  | Input Leakuge Current                     |                     |      | 10              | μΑ   | V <sub>IN</sub> =0 to V <sub>ec</sub>    |

| 1 <sub>LOH</sub> | Tri-State Output Leakage Current in Float |                     |      | 10              | μА   | V <sub>OUT</sub> =2.4 to V <sub>cc</sub> |

| LOL              | Tri-State Output Leakage Current in Float |                     |      | -10             | μА   | OLT=0.4/                                 |

| l <sup>LD</sup>  | Data Bas Leakage Current in Input Mode    |                     |      | =10             | μΑ   | 0 < V <sub>IN</sub> < V <sub>cc</sub>    |

Tabla 2.2.1.1. Características en DC de Z80-CPU

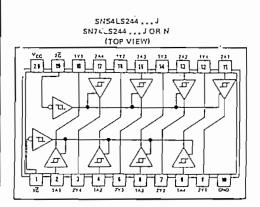

siendo por ello conveniente el conectarlos a buffers de mane ra de poder conseguir el tener conectado a las varas un mayor número de cargas.

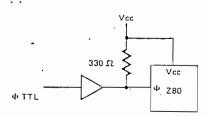

El valor máximo de capacitancia que tienen las líneas en DC se resume en la tabla 2.2.1.2.; y en la figura 2.2.1. se mues tra la forma más conveniente de realizar la conexión para la señal de reloj  $\phi$  en Z80-CPU.

T<sub>A</sub> = 25°C, f = 1 MHz, unmeasured pins returned to ground

| Symbol            | Parameter          | Max. | Unit |  |

|-------------------|--------------------|------|------|--|

| СФ                | Clock Capacitance  | 20   | pF   |  |

| c <sup>IM</sup> . | Input Capacitance  | 5 .  | pF   |  |

| c <sub>out</sub>  | Output Capacitance | 10   | рŀ   |  |

Tabla 2.2.1.2. Capacitancia en los pines de Z80-CPU

Figura 2.2.1. Circuito que cumple los requerimientos para la señal  $\phi$  en A.C. y D.C.

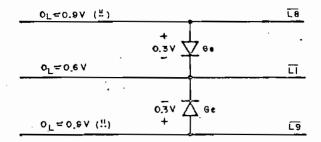

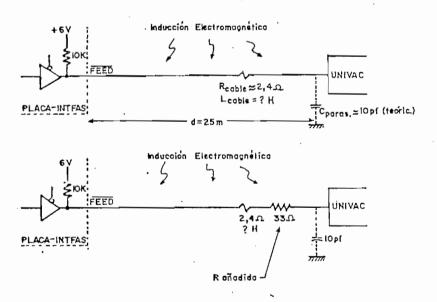

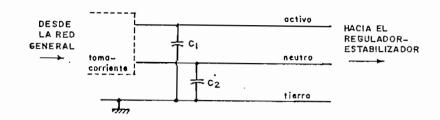

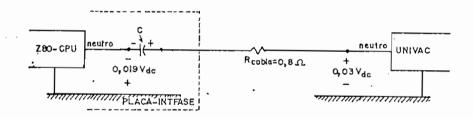

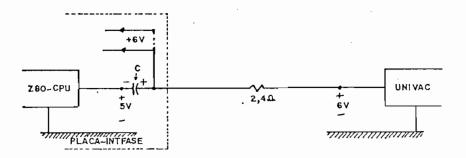

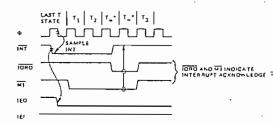

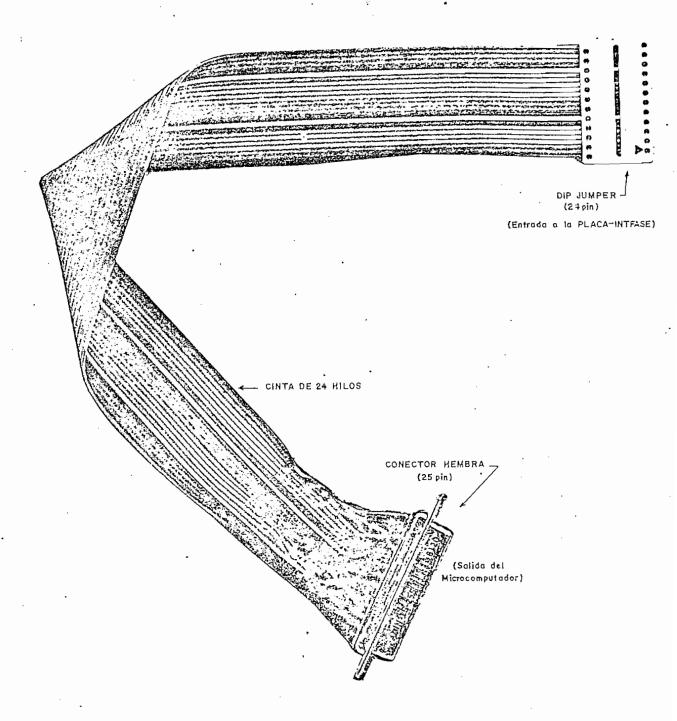

#### 2.2.2. CARACTERISTICAS EN AC