# ESCUELA POLITÉCNICA NACIONAL

## ESCUELA DE INGENIERIA EN ELECTRÓNICA Y TELECOMUNICACIONES

DISEÑO Y CONSTRUCCIÓN DE UN OSCILADOR CONTROLADO POR VOLTAJE CON SELECCIÓN DE FRECUENCIA

PROYECTO PREVIO A LA OBTENCIÓN DEL TITULO DE INGENIERO EN ELECTRÓNICA Y TELECOMUNICACIONES

MAYRA ELIZABETH VACA PEREZ

DIRECTOR: ING. MARIO CEVALLOS

Quito, Noviembre 2001

## **DECLARACIÓN**

Yo Mayra Elizabeth Vaca Pérez, declaro que el trabajo aquí descrito es de mi autoría; que no ha sido previamente presentada para ningún grado o calificación profesional; y, que he consultado las referencias bibliográficas que se incluyen en este documento.

La Escuela Politécnica Nacional, puede hacer uso de los derechos correspondientes a este trabajo, según lo establecido por la Ley, Reglamento de Propiedad Intelectual y por la normatividad institucional vigente.

Mayra Vaca P

## CERTIFICACIÓN

Certifico que el presente trabajo fue desarrollado por Mayra Vaca Pérez, bajo mi supervisión.

Ing. Mario Cevallos

DIRECTOR DE PROYECTO

#### **AGRADECIMIENTOS**

Al Ing. Mario Cevallos por su acertada dirección en el presente Proyecto de Tesis por su paciencia y sus conocimientos.

Al Departamento de Geofísica por su apoyo económico para la realización del presente Proyecto de Titulación, y por sus enseñanzas de la ciencia con fin social.

Al Área de Electrónica del Departamento de Geofísica, por su respaldo, sus opiniones, sus consejos técnicos y por su amistad.

Al Fis. Ricardo Ascazubi y Fis. Omar Marcillo, por todo su apoyo en la programación y por compartir sus conocimientos.

Al personal del Departamento de Geofísica, mi segunda familia, por su amistad y apoyo durante todo este tiempo.

A mis padres, por su eterno amor su respaldo constante, y todas sus enseñanzas, que han permitido culmine mi carrera y sobre todo su enseñanza de moral y calidez humana.

A mis hermanos Sandra, María Elena y Hernán por todos los gratos momentos, respaldo, por sus sonrisas y el compartir diario.

A Marcelo por todo el amor, y los largos días de espera.

**DEDICATORIA**

A Daniela o Daniel.....

## CONTENIDO

| Contenido   |                                                       | i       |

|-------------|-------------------------------------------------------|---------|

| Introducció | n                                                     | V       |

| CAPITULO    | 1 GENERALIDADES                                       |         |

| 1.1 Descrip | oción de la Red Sísmica del Departamento de Geofísica | 1       |

| 1.2 Estacio | nes Sísmicas Remotas                                  | 4       |

| 1.2.1       | Sismómetro                                            | 4       |

| 1.2.2       | Oscilador Controlado por voltaje VCO                  | 5       |

| 1.2.3       | Equipo de transmisión                                 | 6       |

| 1.3 Estació | n Repetidora                                          | 6       |

| 1.4 Estació | n Base                                                | 7       |

| 1.4.1       | Receptores                                            | 7       |

| 1.4.2       | Discriminadores                                       | 7       |

| 1.4.3       | Registro Análogo                                      | 7       |

| 1.4.4       | Registro Digital                                      | 8       |

| CAPITULO    | 2 DISEÑO DE LAS ETAPAS CONSTITUVAS DEL                | SISTEMA |

| 2.1 Requeri | mientos del Sistema                                   | 12      |

| 2.2 Descrip | ción General                                          | 13      |

| 2.2.1       | Diagrama de bolques                                   | 13      |

| 2.2.2       | Polarización                                          | 14      |

| 2.2.3       | Etapa de preamplificación                             | 14      |

| 2.2.4       | Convertidor Análogo Digital                           | 15      |

|             | 2.2.4.1 Registros del AD7706                          | 16      |

|             | 2.2.4.1.1 Registro de Comunicaciones                  | 16      |

|             | 2.2.4.1.2 Registro de Configuración                   | 18      |

|             | 2.2.4.1.3 Registro de reloj                           | 20      |

|             | 2.2.4.1.4 Registro de Datos                           | 22      |

|             |                                                       |         |

| 2.2.4.1.5 Registro de prueba                               | 22 |

|------------------------------------------------------------|----|

| 2.2.4.1.6 Registro de Calibración                          | 22 |

| 2.2.4.2 Ventajas del uso del AD7706                        | 23 |

| 2.2.4.2.1 Mejoramiento de la resolución                    | 23 |

| 2.2.4.2.2 Frecuencia de muestreo                           | 24 |

| 2.2.4.2.3 Ganancia                                         | 25 |

| 2.2.4.2.4 Interfase serial                                 | 25 |

| 2.2.5 Microcontrolador                                     | 26 |

| 2.2.6 Generador de la onda sinusoidal                      | 28 |

|                                                            |    |

| 2.2.6.1 Operación del circuito realimentado como oscilador | 29 |

| 2.2.6.2 Oscilador controlado por voltaje                   | 31 |

| 2.2.6.2.1 VCO con oscilador Colpitts                       | 31 |

| 2.2.6.2.2 VCO con osciladores de base común                | 35 |

| 2.2.6.2.3 VCO con oscilador de relajación                  | 35 |

| 2.2.6.2.4 VCO con osciladores de anillo                    | 37 |

| 2.2.6.2.5 VCO con multiplicador de cuadratura              | 37 |

| 2.2.6.2.6 VCO de alto nivel                                | 40 |

| 2.2.6.3 Oscilador enganchado en fase PLL                   | 41 |

| 2.2.6.3.1 Enganche y captura                               | 43 |

| 2.2.6.3.2 Captura transitoria                              | 44 |

| 2.2.6.3.3 Efecto del filtro pasa bajo                      | 46 |

| 2.2.6.3.4 Procedimiento general de diseño del filtro       | 46 |

| 2.2.6.4 Aplicaciones                                       | 50 |

| 2.2.6.4.1 Demodulación de frecuencia                       | 50 |

| 2.2.6.4.2 Síntesis de frecuencia                           | 51 |

|                                                            |    |

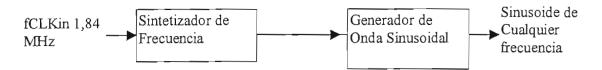

| 2.2.6 Generador de la onda sinusoidal                      | 52 |

| 2.2.6.1 Síntesis de frecuencia                             | 53 |

| 2.2.6.2 Generador de onda sinusoidal digital               | 54 |

| 2.2.6.3. Prototino inicial para generación de frecuencias  | 56 |

|   | • |  |

|---|---|--|

| 1 | 1 |  |

| 1 | 1 |  |

| 2.2.7 Terminal de comunicaciones                                     | 61 |

|----------------------------------------------------------------------|----|

| 2.2.8 Sumador y salida al radio                                      | 62 |

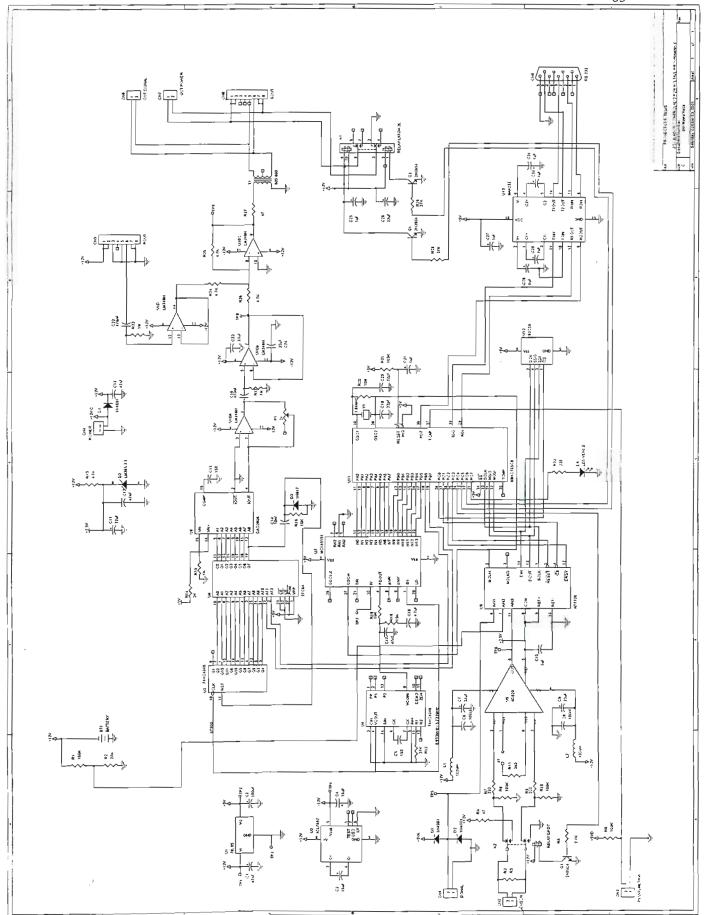

| 2.29 Esquema de la tarjeta diseñada                                  | 62 |

| CAPITULO 3 REQUERIMIENTOS DE SOFTWARE                                |    |

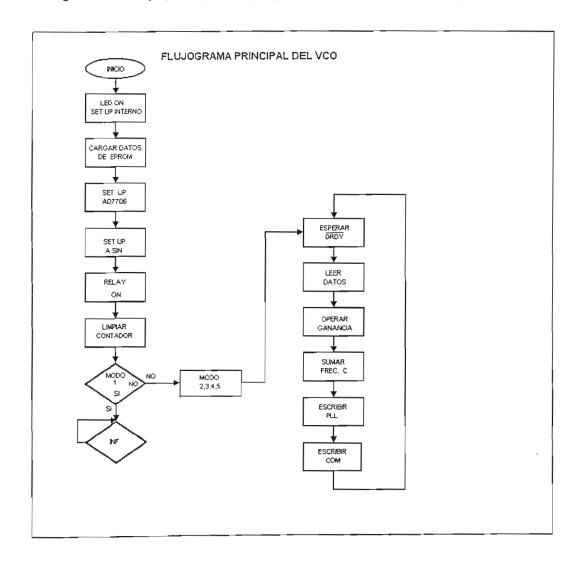

| 3.1 Programa para el Microcontrolador MC68HC705C8A                   | 65 |

| 31.1 Requerimientos Generales                                        | 65 |

| 3.1.2 Estructura general del programa                                | 66 |

| 3.1.2.1 Programa principal                                           | 66 |

| 3.1.2.2 Desarrollo del software                                      | 69 |

| 3.1.2.2.1 Asignación de Pórticos                                     | 69 |

| 3.1.2.2.2 Asignación de Registros                                    | 70 |

| 3.1.2.2.3 Asignación de Variables                                    | 72 |

| 3.1.2.2 Desarrollo de Subrutinas en Assembler                        | 74 |

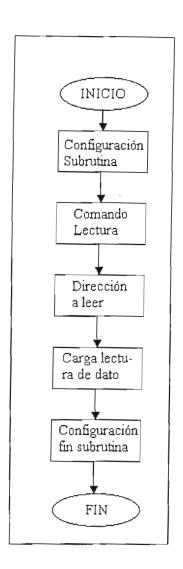

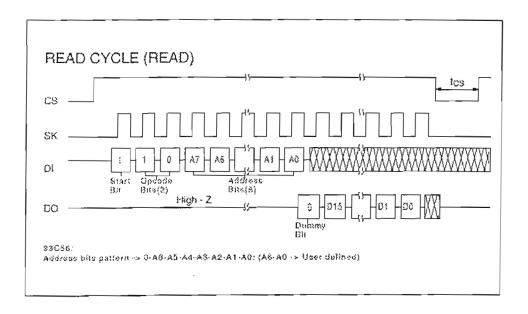

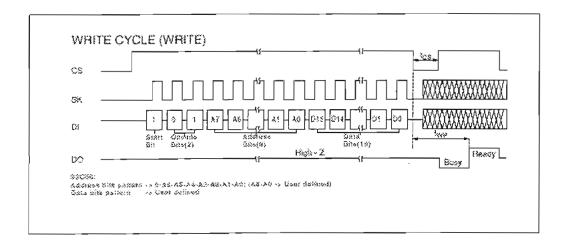

| 3.1.2.2.1 Subrutina REEPROM                                          | 74 |

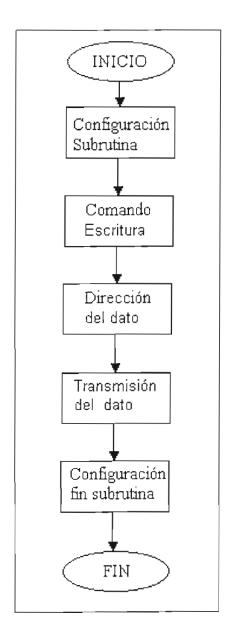

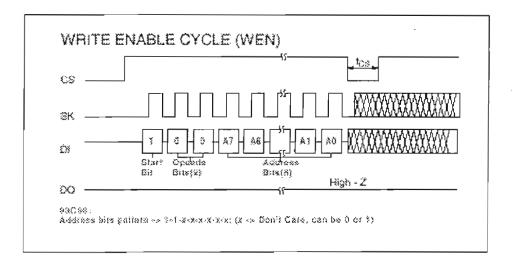

| 3.1.2.2.2 Subrutina WEEPROM                                          | 77 |

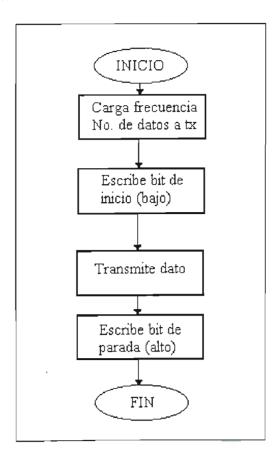

| 3.1.2.2.3 Subrutina TX_DATA                                          | 80 |

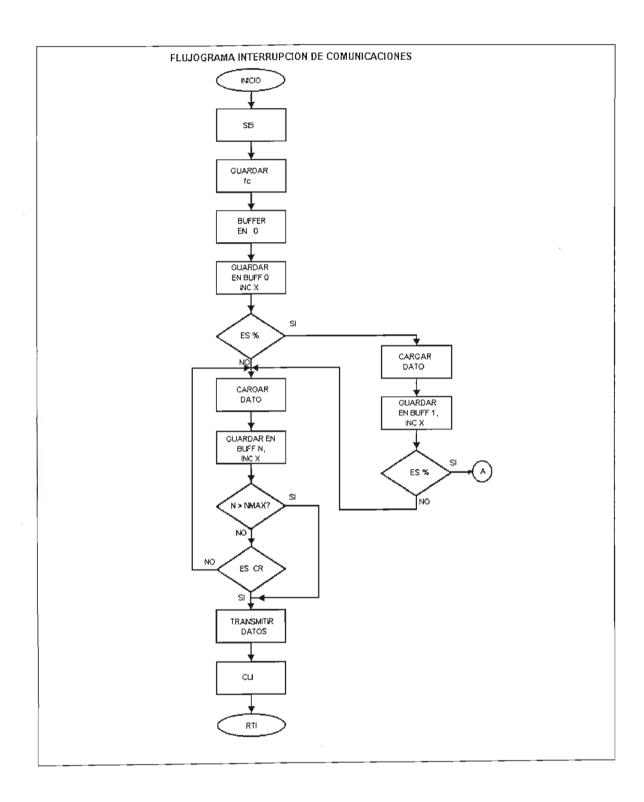

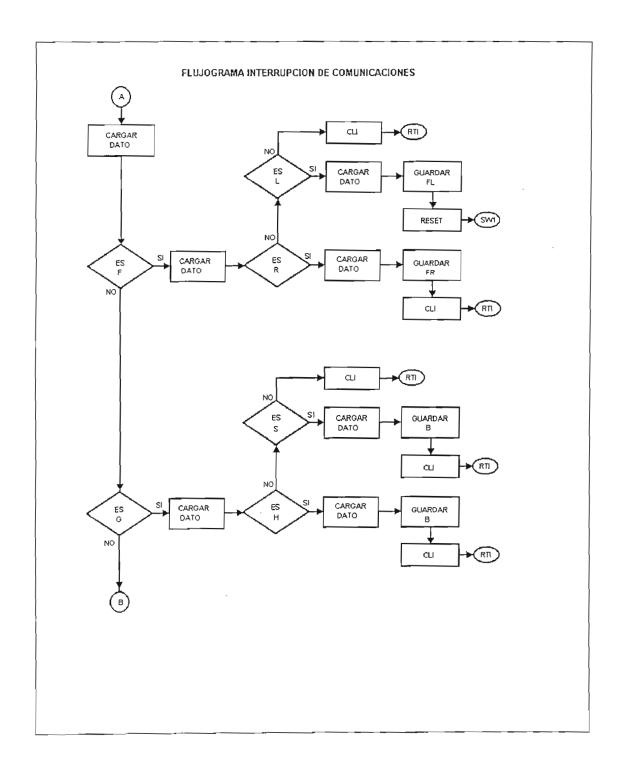

| 3.1.2.3 Desarrollo de Interrupciones en Assembler                    | 81 |

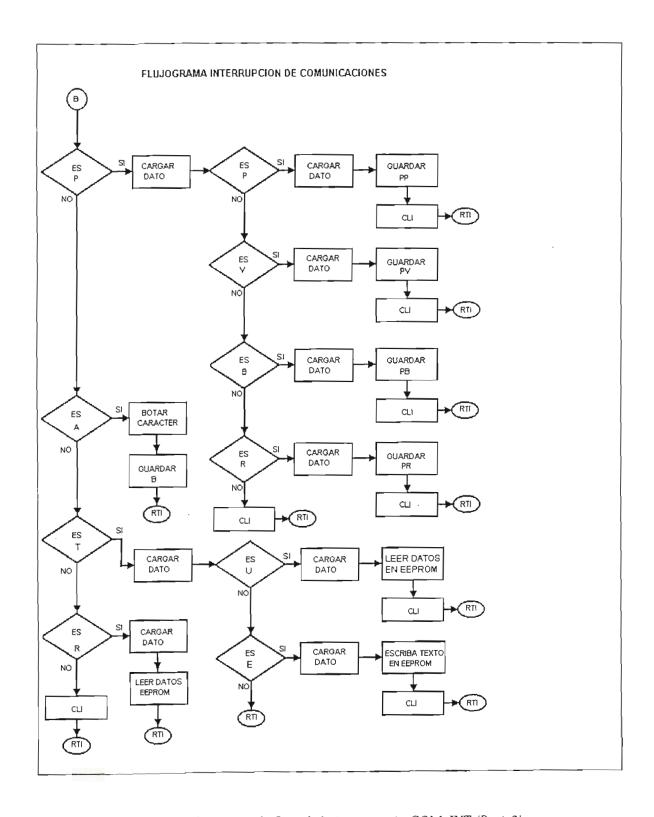

| 3.1.2.3.1 Interrupción COM _INT                                      | 81 |

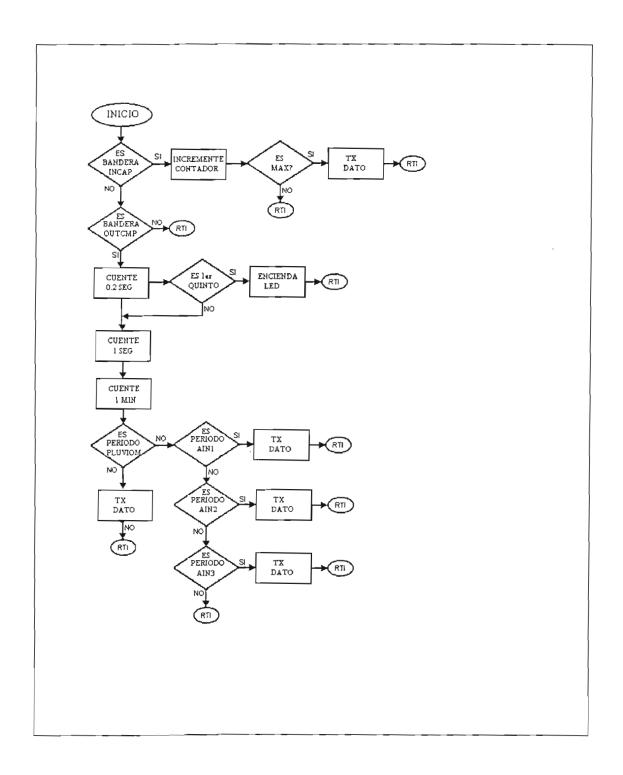

| 3.1.2.3.2 Interrupción TIMER_INT                                     | 88 |

| 3.1.2.3.3 Interrupción SPI_INT                                       | 90 |

| 3.1.2.3.4 Interrupción IRQ_INT                                       | 90 |

| 3.1.2.3.5 Interrupción SWI_INT                                       | 90 |

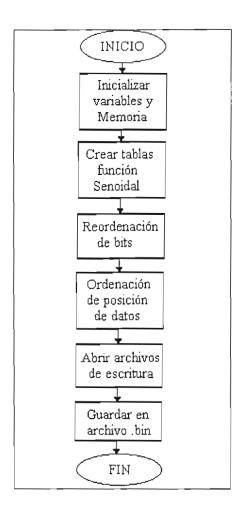

| 3.2 Programa para el almacenamiento de la función seno en la memoria |    |

| EPROM                                                                | 91 |

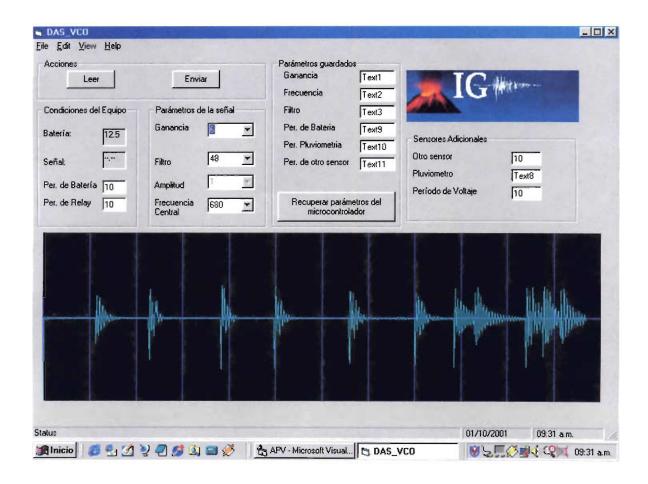

| 3.3 Programa para Comunicación con el Usuario                        | 92 |

| CAPITULO IV ASPECTOS CONSTRUCTIVOS                                   |    |

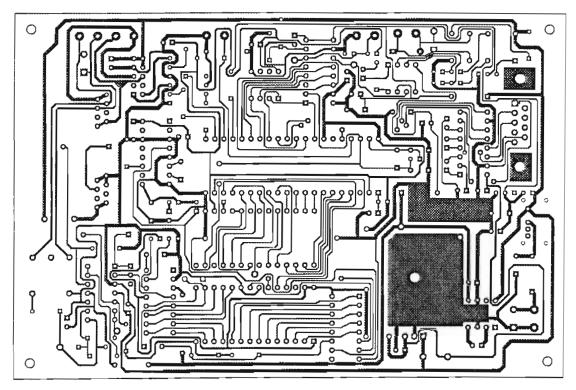

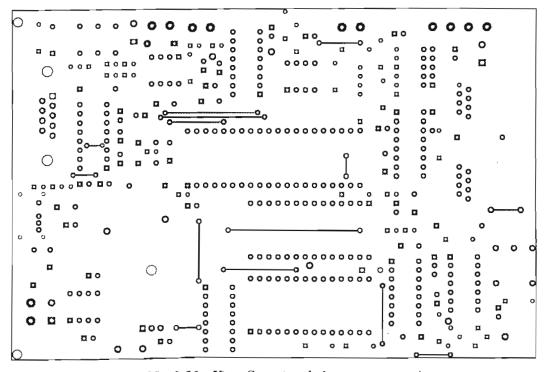

| 4.1 Ensamblaje de la tarjeta                                         | 95 |

| 4.2 Características I | Físicas                                  | 98        |

|-----------------------|------------------------------------------|-----------|

| 4.3 Análisis Técnico  | Económico                                | 99        |

| 4.3.1 Alcand          | e y limitaciones del equipo              | 103       |

|                       |                                          |           |

| CAPITULO V            | PRUEBAS EXPERIMENTALES Y R               | ESULTADOS |

| 5.1 Operación del S   | Sistema                                  | 105       |

| 5.2 Comparación co    | n otros VCOs comerciales                 | 113       |

| CONCLUSIONES Y F      | RECOMENDACIONES                          | 119       |

| REFERENCIAS BIBL      |                                          | 122       |

| ANEXOS                | 70 070 11 707.10                         | 122       |

| Anexo 1               |                                          |           |

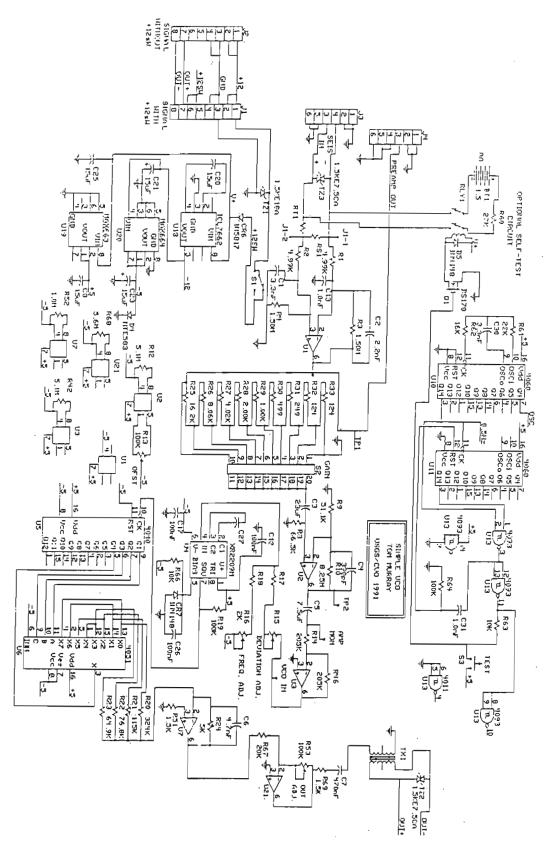

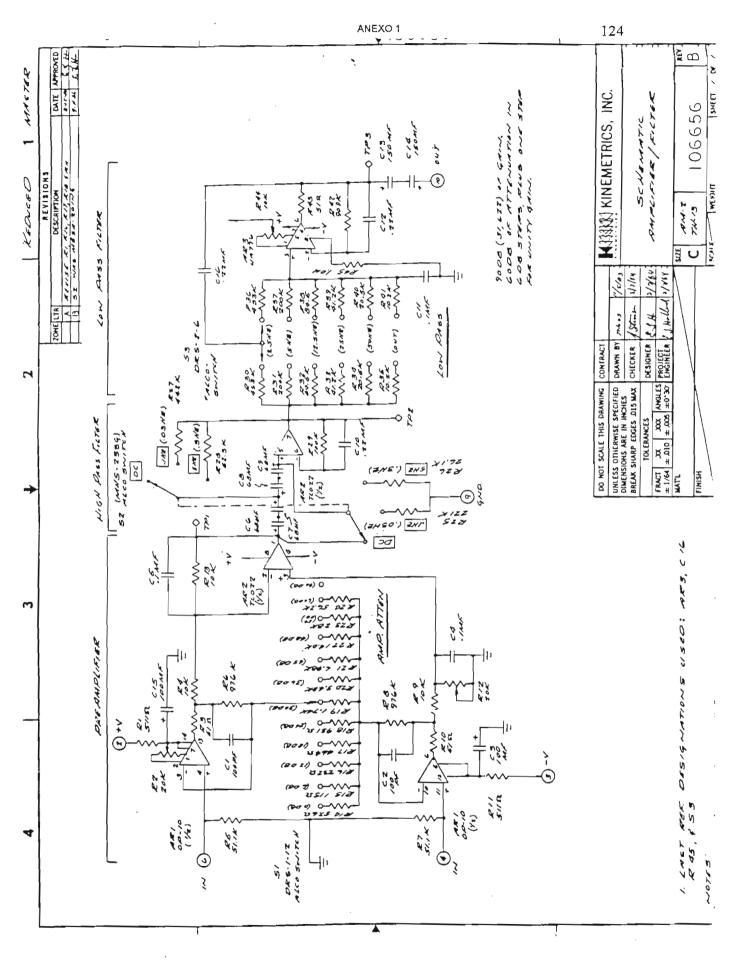

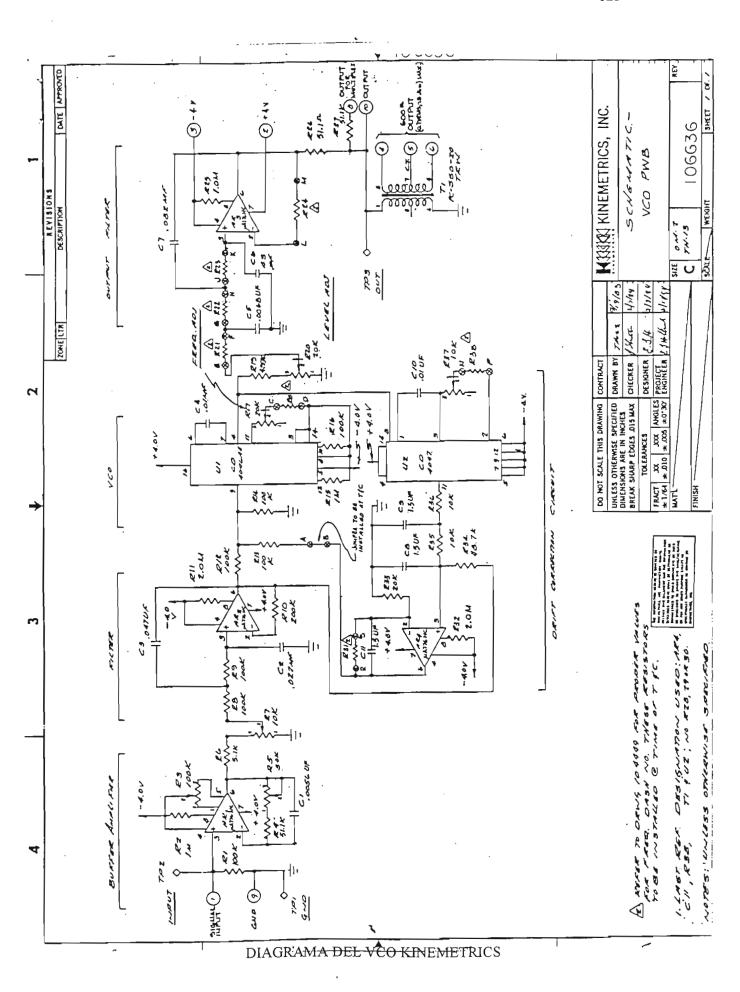

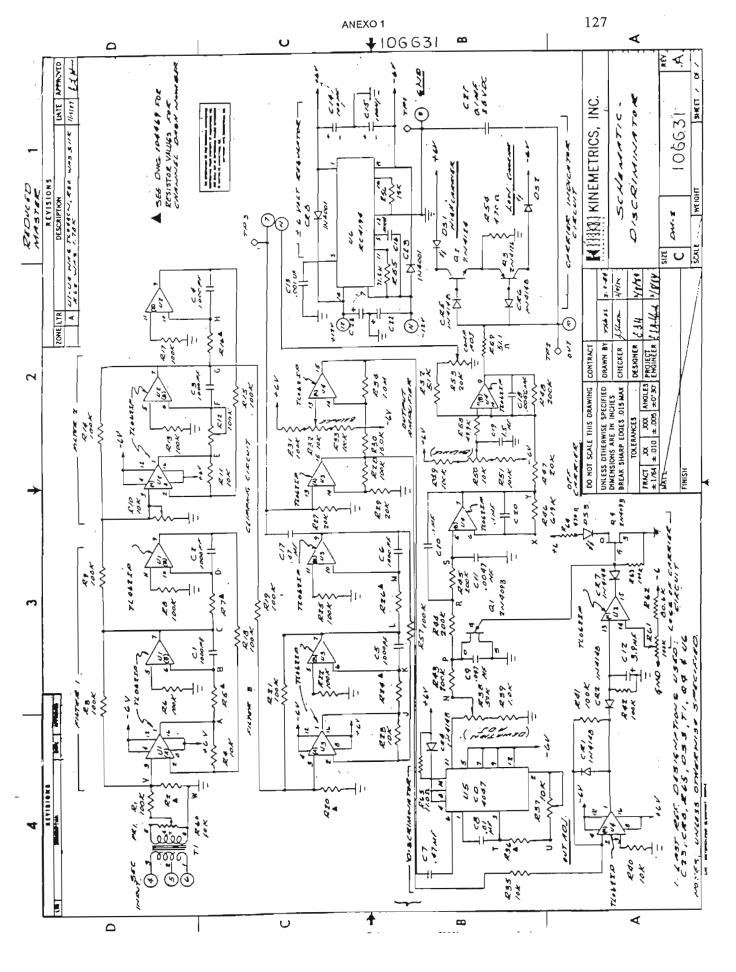

| Diagrama del cir      | cuito del VCO (Diseño USGS)              | 123       |

| _                     | tarjeta amplificadora (VCO Kionemetrics) | 124       |

| Diagrama del V(       | CO Kinemetrics                           | 125       |

| Diagrama del dis      | scriminador (Diseño USGS)                | 126       |

| Diagrama del dis      | scriminador Kinemetrics                  | 127       |

| Anexo2                |                                          |           |

| Data Sheet AD6        | 20                                       | 128       |

| Data Sheet AD7        | 706                                      | 132       |

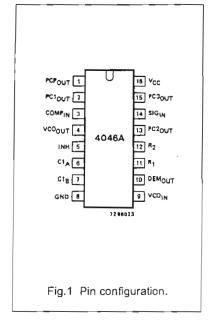

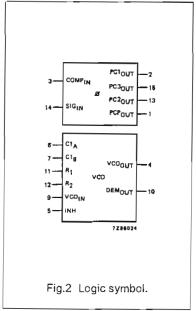

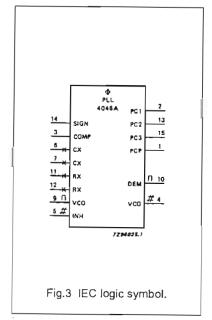

| Data Sheet 74H        | C4046                                    | 139       |

| Data Sheet MC1        | 45151-2                                  | 144       |

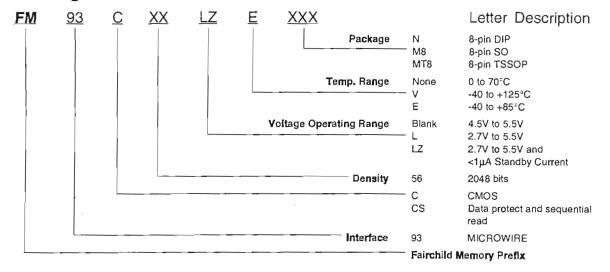

| Data Sheet FM9        | 3C56                                     | 150       |

| Anexo 3               |                                          |           |

| Programa en en        | samblador para el MC68HC705CA            | 154       |

| Programa de inv       | ersión de datos para la función seno     | 186       |

| Anexo 4               |                                          |           |

Manual de usuario

iv

188

#### INTRODUCCION

El Departamento de Geofísica de la Escuela Politécnica Nacional, se encarga del Monitoreo Sísmico y Volcánico del país. Desde 1983, fecha de su creación se ha incrementando el número de estaciones dedicadas a esta labor, conforme se han conseguido los implementos necesarios para las mismas, a través de la ejecución de proyectos de investigación con otras instituciones u organismos tanto nacionales como internacionales.

Con la finalidad de dar una respuesta adecuada ante cualquier evento sísmico, se requiere realizar este monitoreo en tiempo real, por lo que el Área Técnica del Departamento de Geofísica se encarga de que las señales provenientes de las estaciones sísmicas lleguen a la estación central utilizando el sistema telemétrico.

Actualmente la Red Nacional de Sismógrafos, Acelerógrafos y Observatorios Volcánicos cuenta con mas de 50 estaciones instaladas a lo largo del país.

Debido a la topografía de la región interandina, se ha ido dificultando cada vez mas el poder llegar con las señales hasta la estación base ubicada en la Escuela Politécnica Nacional en Quito, lo que ha significado un incremento de trabajo, en especial en lo referente al mantenimiento y ubicación de la Red.

Para poder llevar las señales sísmicas de las diferentes estaciones hasta el Departamento de Geofísica se utiliza la forma de transmisión telemétrica y uno de los equipos principales es el Oscilador Controlado por Voltaje (VCO) por lo que se vio en la necesidad de diseñar un oscilador con selección de frecuencia que ayudaría a las labores de mantenimiento de la Red, además se podrá adecuar para realizar cambios hacia la transmisión digital y de esta manera llegar a un mejoramiento del equipo electrónico. Además se constituiría en un equipo inicial para empezar una serie de diseños propios para aplicaciones geofísicas.

Por este motivo en el presente proyecto de tesis se ha desarrollado el diseño y la construcción de un Oscilador Controlado por Voltaje con selección de frecuencia. Para ello se presenta en el Capitulo I una breve descripción de la Red Sísmica que dispone el Departamento de Geofísica.

En el Capitulo II se detalla el diseño realizado en el presente proyecto, cada una de las etapas especificadas claramente, así como también se incluyen los conceptos teóricos asociados al tema.

En el Capitulo III, se presenta en detalle el software desarrollado, tanto para el microcontrolador utilizado en el presente diseño, así como la explicación del programa para manejo del equipo.

En el Capitulo IV y V se indican las pruebas realizadas, el costo del equipo y también se pone en consideración las conclusiones y recomendaciones que se han obtenido al finalizar el presente trabajo.

Adicionalmente en los Anexos respectivos se incluye toda la información referente a los diversos componentes utilizados en el diseño con la finalidad de que sea un medio de consulta para quienes deseen utilizarlos en otras aplicaciones.

#### GENERALIDADES

## 1.1 DESCRIPCIÓN DE LA RED SÍSMICA DEL DEPARTAMENTO DE GEOFÍSICA

En forma general, se puede decir que los sismos constituyen la manifestación de la liberación repentina de la energía acumulada en la tierra durante largos intervalos de tiempo. Las ondas sísmicas generadas se propagan desde el hipocentro del sismo en todas las direcciones, a través de la corteza terrestre. Dichas ondas viajan largas distancias y son detectadas por elementos sensitivos, llamados sismómetros, que se hallan ubicados en las proximidades de la superficie terrestre. Las ondas sísmicas pueden además ser registradas en diversos medios: archivos en disco de computador, bandas de papel ahumado, película fotográfica, etc.

Para realizar estudios e investigaciones sismológicas, es necesario tener una red de sismómetros altamente sensitivos. Esta red se denomina red sísmica, y puede ser operada ya sea por el envío de las señales sísmicas telemétricas hacia un sitio central de almacenamiento o en cada estación individual. Dependiendo de la aplicación, del trabajo particular deseado y de los recursos humanos y técnicos disponibles, la red puede tener desde algunas estaciones hasta cientos de ellas.

Las redes sísmicas constituyen herramientas muy útiles para el estudio de la naturaleza y el estado de los procesos tectónicos. Algunas de sus aplicaciones tienen que ver con el monitoreo de sismicidad para propósito de predicción sísmica, mapeo de fallas activas, para evaluación de peligros volcánicos,

exploración de recursos geotermales, investigación de la estructura de la corteza terrestre, entre otras cosas.

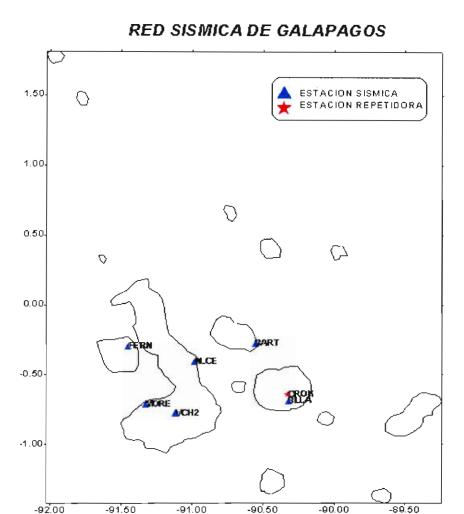

La Red Sísmica que posee el Departamento de Geofísica, en la actualidad consta de 53 estaciones sísmicas remotas que se hallan distribuidas dentro del callejón interandino, en la costa norte, en el norte del oriente ecuatoriano y en las Islas Galápagos, que además de monitorear los volcanes que se encuentran activos, permite controlar la actividad sismotectónica del país.

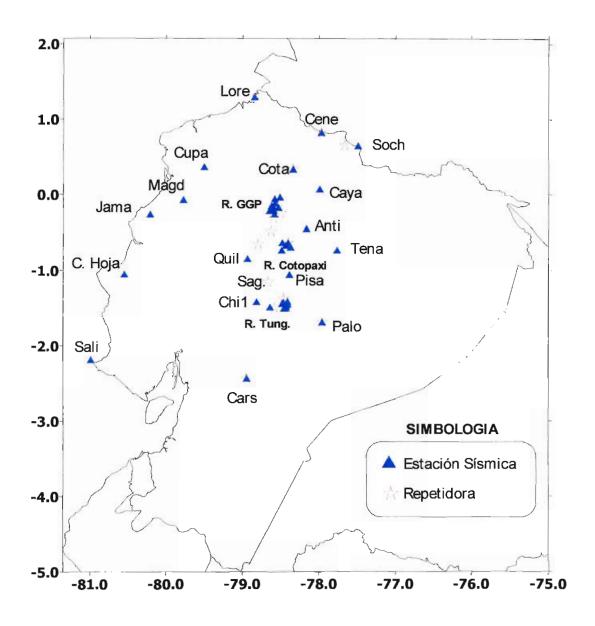

La red posee un sistema de transmisión de radioenlace que envía la señal desde las estaciones sísmicas remotas hasta la estación base localizada en el sexto piso del edificio de Ingeniería Civil en la Escuela Politécnica Nacional, en donde se poseen sistemas de registro analógico y digital en tiempo real, para el respectivo procesamiento de la señal sísmica. Para que esto sea posible se han colocado 17 repetidoras en sitios estratégicos con la finalidad de llegar con la señal hasta la estación base. Ocasionalmente en el mismo sitio se tiene también una estación sísmica y repetidora como se pude observar en las Fig. No.1.1 y Fig. No.1.2

Fig No. 1.1 Red Sísmica Continental del Departamento de Geofisica

#### Fig. No.1. 2 Red Sísmica Insular del Departamento de Geofísica

## 1.2.- ESTACIONES SÍSMICAS REMOTAS

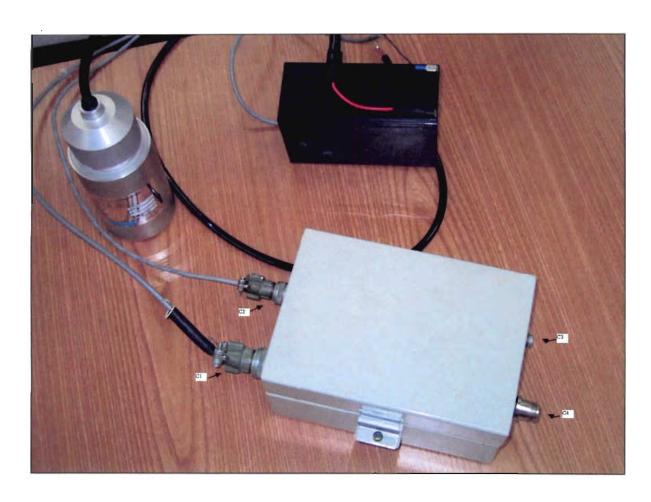

Una estación sísmica remota esta conformada básicamente por los siguientes elementos: sismómetro, oscilador controlado por voltaje (V.C.O.), radio transmisor, antena y sistema de alimentación.

#### 1.2.1.- SISMÓMETRO.-

Es el principal elemento de la estación sísmica, por cuanto detecta las vibraciones del suelo, ondas sísmicas y las transforma en impulsos eléctricos.

El de mayor uso se basa en el principio de la inercia, Sismómetro de Péndulo, que consiste esencialmente de una masa inercial suspendida por elementos elásticos dentro de una armadura rígida. Ante el paso de las ondas sísmicas se altera el equilibrio de la armadura, y la inercia de la masa reacciona contra las fuerzas transmitidas a través de la suspensión, produciéndose un movimiento relativo entre la masa y la armadura. Estos movimientos son detectados y amplificados por un sistema electromagnético en donde la salida es proporcional a la velocidad relativa de sus elementos.

En forma general los sismómetros se clasifican de acuerdo a su respuesta de frecuencia en: período corto (1 Hz), período largo o intermedio (entre 20 Hz y 40 Hz) y período ultra largo o instrumentos de banda ancha (alrededor de 100 Hz). El Departamento de Geofísica dispone de sensores de periodo corto L4C (Mark Products) y Ranger SS1 (Kinemetrics).

#### 1.2.2 OSCILADOR CONTROLADO POR VOLTAJE (VCO).-

La señal análoga proveniente del sismómetro es del orden de los milivoltios, por lo cual es necesario amplificarla, filtrarla y convertirla en una señal sinusoidal que posteriormente modulada pueda ser transmisible. Para realizar esta función se utiliza un amplificador y un oscilador controlado por voltaje (VCO), el cual a partir de una frecuencia central determinada produce una señal de salida sinusoidal, con una frecuencia proporcional al voltaje proveniente del sismómetro.

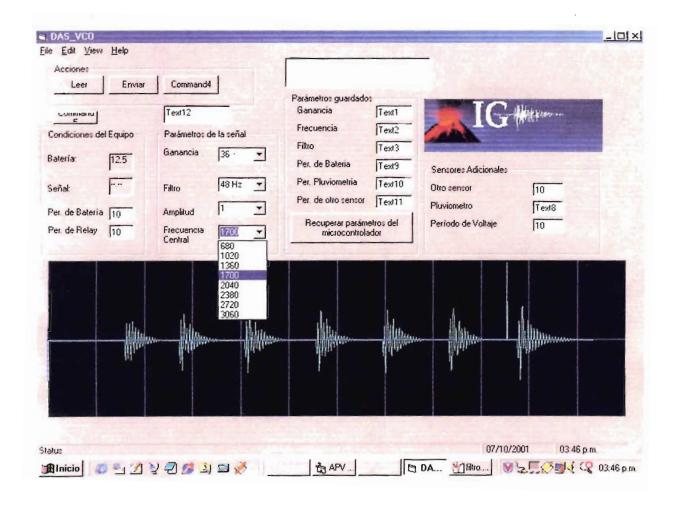

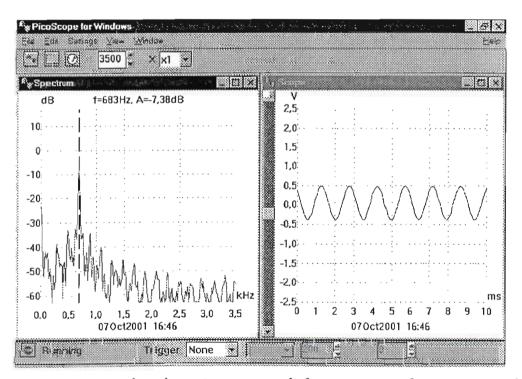

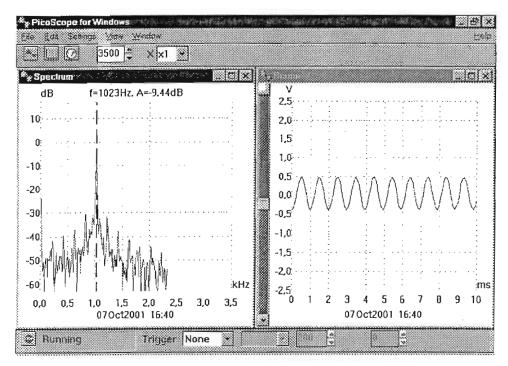

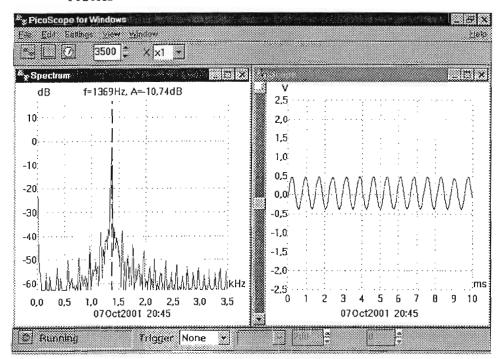

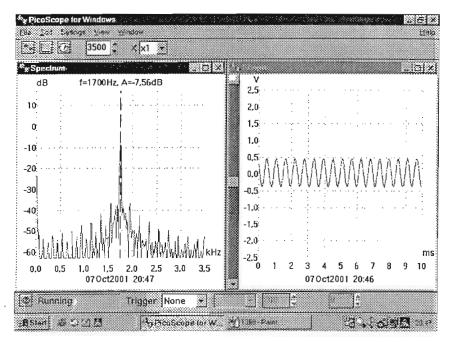

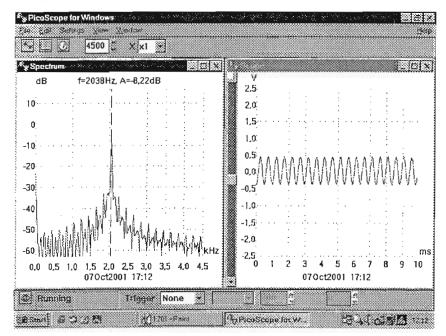

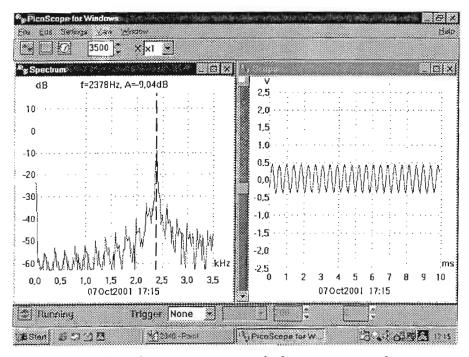

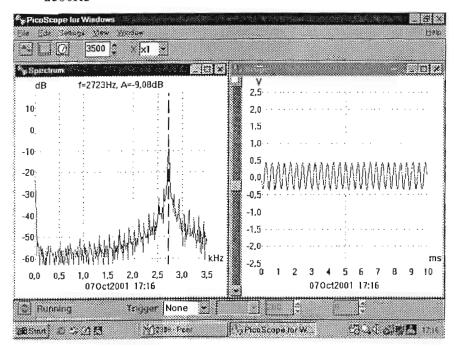

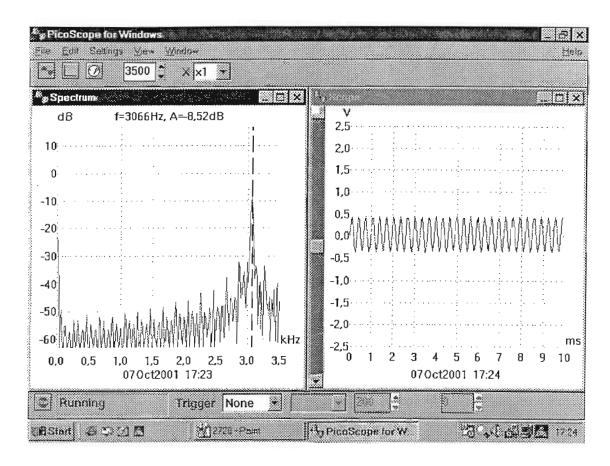

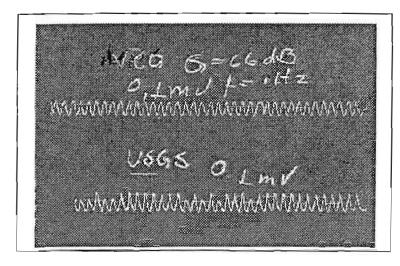

En el Departamento de Geofísica actualmente se utilizan dos tipos de VCO, el primero desarrollado y comercializado por la Kinemetrics y otro diseñado por United States Geologycal Survey USGS, cualquiera de ellos para una frecuencia central específica en los siguientes valores: 680 Hz, 1020 Hz, 1360Hz, 1700 Hz, 2040 Hz, 2380 Hz, 2720 Hz y 3060 Hz cubriendo todo el canal de audio, cada

6

portadora tiene un ancho de banda de 250 Hz, los diagramas correspondientes se adjuntan en el Anexo No. 1.

### 1.2.3.- EQUIPO DE TRANSMISIÓN.-

El envío de la señal desde la estación sísmica remota hacia la estación base se realiza por medio de radioenlaces en la banda de UHF. El transmisor es el elemento con la potencia necesaria que permite la transmisión de la señal a distancia. El Departamento de Geofísica utiliza los radios Monitron de 1 y 2 W de potencia. En la banda de 401.000 a 402.000 MHz.

Para este tipo de enlaces, se utilizan antenas Yagi Uda de las siguientes características:

Ganancia 11dB

SWR 1,3

Diagrama de radiación directivo

Para la alimentación de las estaciones sísmicas remotas se utilizan baterías de 12 Vdc. 60 Ah. Alimentadas por paneles solares de 43W.

### 1.3.- ESTACIÓN REPETIDORA.-

Debido a la condición geográfica del país, se han tenido que colocar estaciones repetidoras para enrutar los datos a la estación base.

Las estaciones repetidoras reciben la señal de una dirección y la encaminan hacia otra, básicamente esta conformada por: antena receptora, radio receptor, mezclador radio transmisor, antena transmisora y sistema de alimentación.

#### 1.4.- ESTACIÓN BASE.

La Estación base, ubicada en el Departamento de Geofísica en el sexto piso del edificio de Ingeniería Civil de la Escuela Politécnica Nacional, se encuentra conformada básicamente por los siguientes elementos: antenas receptoras, radios receptores, discriminadores, registradores analógicos, sistema digital de adquisición de datos, software de procesamiento.

#### 1.4.1.- RECEPTORES.-

El receptor recibe la señal de radiofrecuencia y la transforma en señal de audio, la misma que luego es discriminada, se dispone de receptores Monitron en el mismo rango de frecuencias que los transmisores.

#### 1.4.2.- DISCRIMINADORES.-

El discriminador, recobra la señal del geófono, es el elemento que desarrolla el proceso inverso del VCO, transforma la información que viene en términos de frecuencia a variaciones de voltaje DC. En el Departamento de Geofísica se cuenta con dos modelos diferentes el DM-2 de fabricación Kinemetrics y el J120d diseñado por el USGS, cuyos circuitos se encuentran en el Anexo No. 1.

Una vez que la señal ha sido discriminada pasa al registrador analógico y al digital.

#### 1.4.3.- REGISTRO ANÁLOGO.-

El registrador analógico se encarga de amplificar, filtrar y transformar el voltaje que sale del discriminador en un movimiento mecánico, que representa la traza

8

del sismograma. Estos registradores utilizan, para grabar la señal, papel ahumado de forma continua para las 24 horas del día. En el Departamento de Geofísica se dispone de los siguientes modelos de registradores analógicos:

PS2 Kinemetrics

MQ-800 Sprengnether

#### 1.4.4.- REGISTRO DIGITAL

La señal de salida del discriminador se convierte en señal digital para obtener un sistema digital de adquisición de datos, se utiliza una tarjeta de conversión analógica/digital, Data Translations, DT-2814 de 16 canales y 12 bits de resolución, frecuencia de muestreo programable y acceso directo a la memoria del computador, para ser aplicable al sistema de registro y procesamiento de datos en una computadora.

La tarjeta de adquisición posee un Controlador de Acceso Directo a Memoria DMA, que permite operar con la memoria RAM del computador (ya sea en tareas de lectura o escritura), sin que se haga necesaria la intervención del CPU del mismo. Esto brinda la posibilidad de utilizar la CPU en otras tareas como copiado y edición de archivos, impresión, etc., mientras el conversor A/D se mantiene permanentemente digitalizando y grabando la información sin perder ningún evento. En el Departamento de Geofísica se dispone de dos programas de adquisición de datos el ACQ (versión 2.7) y el EARTHWORM (versión 4.1).

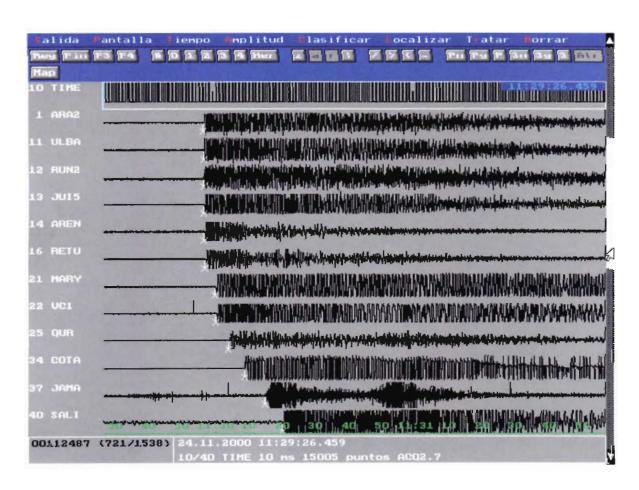

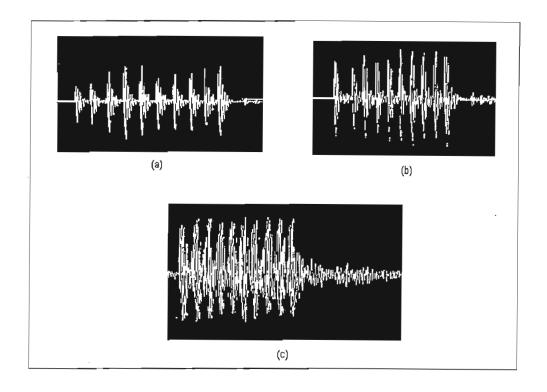

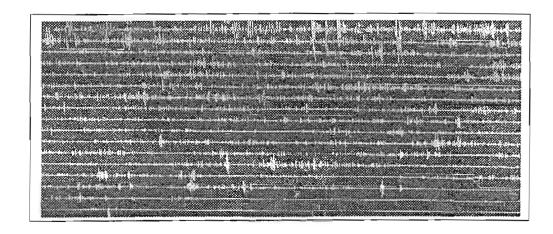

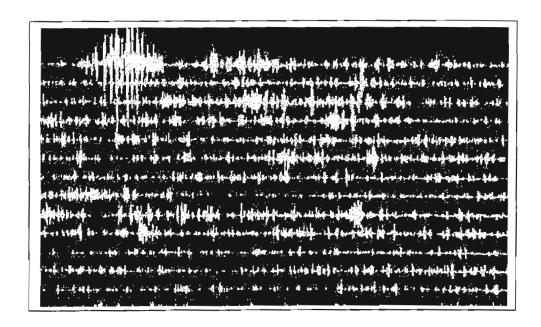

El programa de adquisición ACQ3 despliega en pantalla cada una de las señales sísmicas (48 estaciones disponibles). Cuando al menos n estaciones de la Red registran un sismo (actualmente n=3), estas disparan el programa, el mismo que en ese instante almacena en disco fijo el sismo registrado. Caso contrario, si no

se dispara el programa, las señales se muestran en pantalla pero no se graban Fig. No. 1.3.

A continuación estos datos son procesados con el programa Sismalp ver 3.0 que permite transformar al formato adecuado para realizar la correlación de trazas, ya que guarda por separado el listado de eventos con fechas y las trazas de eventos sísmicos en sí, una vez completado este proceso los datos están en código ASCII para su procesamiento.

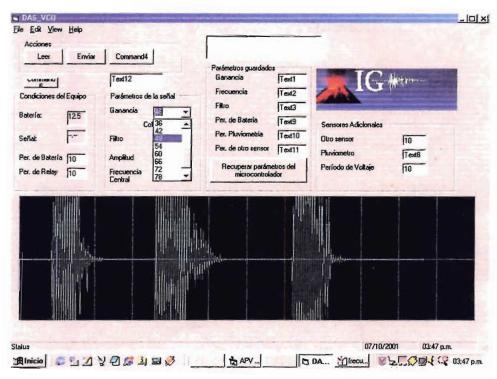

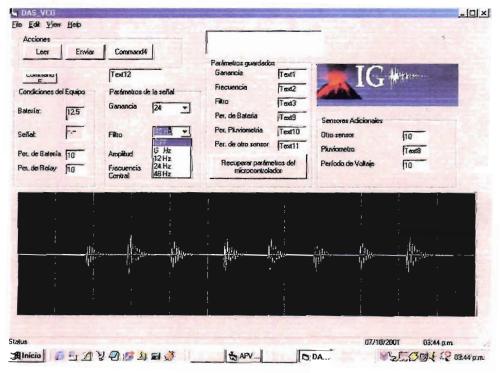

Fig. No. 1.3.- Señales sísmicas digitales, originadas por el programa ACQ3

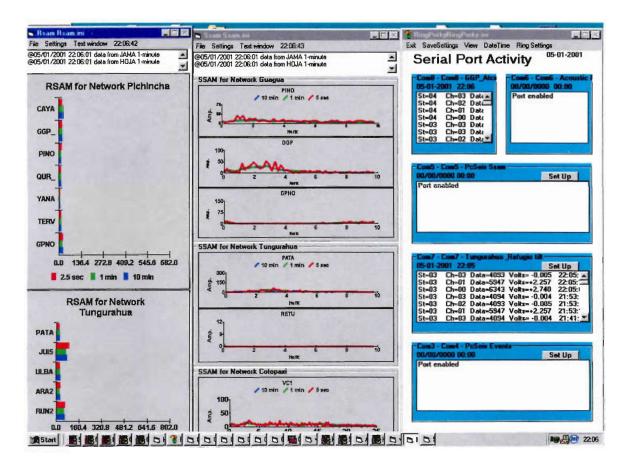

El programa Earthworm es un sistema de adquisición de un conjunto de datos sísmicos, este sistema en red puede combinar datos en tiempo real, aumentando la capacidad de monitoreo y de interpretación. Tiene numerosos módulos para

funciones específicas calcula los valores de la medida de la amplitud del espectro sísmico SSAM y la medida de la amplitud sísmica en tiempo real RSAM, almacenan los datos de las estaciones sísmicas con un número mínimo de disparo y también en subredes, es de aplicación especial para el monitoreo volcánico Fig. No. 1.4.

Luego se ejecuta el programa PCEQ, el cual permite ubicar las fases P (onda primaria o de compresión, hace vibrar una partícula en el sentido de propagación de las ondas) y S (onda secundaria o de cizalla, hace vibrar una partícula en sentido perpendicular a la trayectoria de las ondas) de la onda sísmica con lo que se determina el tiempo de arribo de la señal a cada estación de la red. Con esta información se puede ubicar el lugar de origen o el epicentro del sismo.

Fig. No. 1.4.- Señales sísmicas digitales, originadas por el programa Earthworm

La salida del programa PCEQ es un archivo en código ASCII Ilamado por defecto PHASE OUT.

Una vez que se ha realizado este proceso, la información contenida en el archivo phase out es analizado por uno de los dos programas localizadores de sismos: FASTHYPO, o HYPOCENTER, para encontrar el hipocentro más aproximado del sismo.

Al final, estos datos una vez procesados pasan a formar parte del "banco de datos sísmicos" clasificados en directorios de año y mes.

## DISEÑO DE LAS ETAPAS CONSTITUTIVAS DEL SISTEMA

#### 2.1.- REQUERIMIENTOS DEL SISTEMA

En el diseño del Oscilador Controlado por Voltaje, VCO por sus siglas en Inglés, para aplicaciones sísmicas y volcanológicas dentro del Departamento de Geofísica se tomó en cuenta cumplir con los siguientes parámetros, para conservar las mismas características de los VCO comerciales; y además otras características adicionales para control y ayuda con la finalidad de pronosticar tempranamente si existe un daño en la estación remota, estas son:

- Los VCOs para usos telemétricos se los hace en la banda de audio, y debe permitir seleccionar cualquier valor de entre las siguientes frecuencias centrales: 680Hz, 1020Hz, 1360Hz, 1700Hz, 2040Hz, 2380Hz, 2720Hz y 3060Hz. Valores que han sido acordados para estos usos.

- El ancho de banda será de 250 Hz para la variación de la señal del sensor mas un valor adicional por las caídas de los filtros da un total de 340 Hz para cada frecuencia.

- Debe permitir seleccionar el valor de ganancia desde 0 dB, (ganancia 1);

hasta 90 dB (31633 veces), en pasos de 6 dB.

- Se podrán interconectar una a otra las tarjetas para casos específicos como envío de señales de sensores de varias componentes, o en caso de requerirse para un mismo sensor dos valores de ganancia alto y bajo.

- Enviar señales de control como nivel de batería, prueba de la señal de sensor y comprobación del VCO, para facilitar la tarea de mantenimiento de la Red Sísmica.

- Permitir enviar señales de otros sensores como pluviómetros o inclinómetros suspendiendo momentáneamente la señal sísmica.

#### 2.2.- DESCRIPCIÓN GENERAL.-

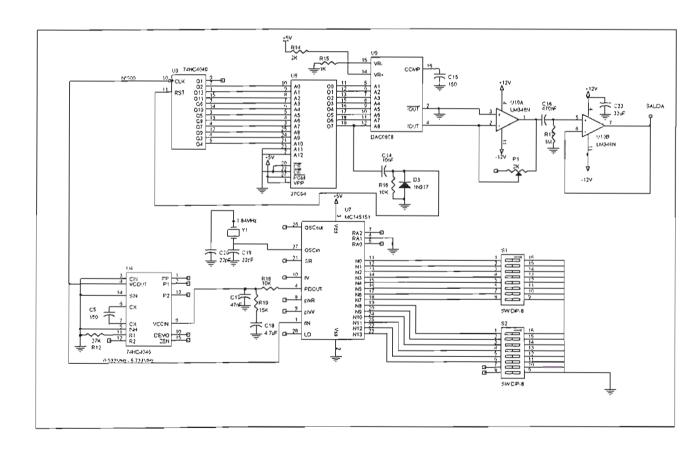

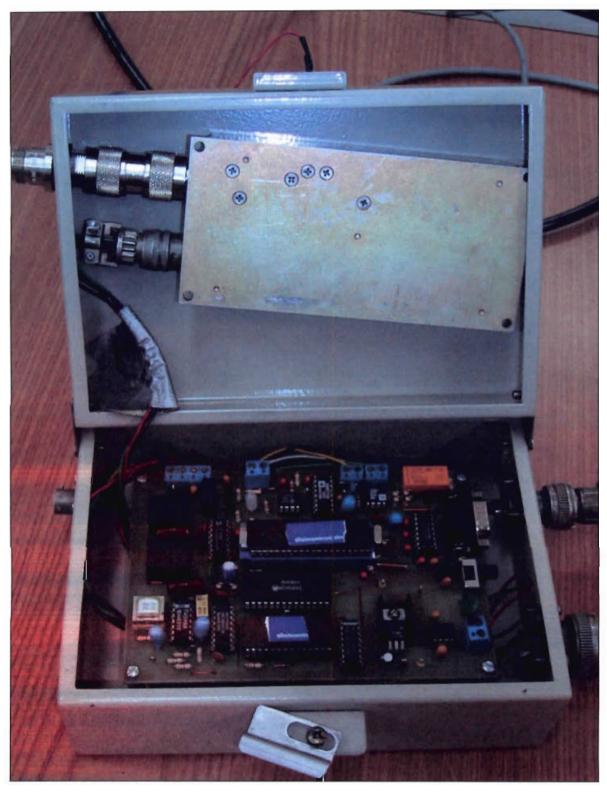

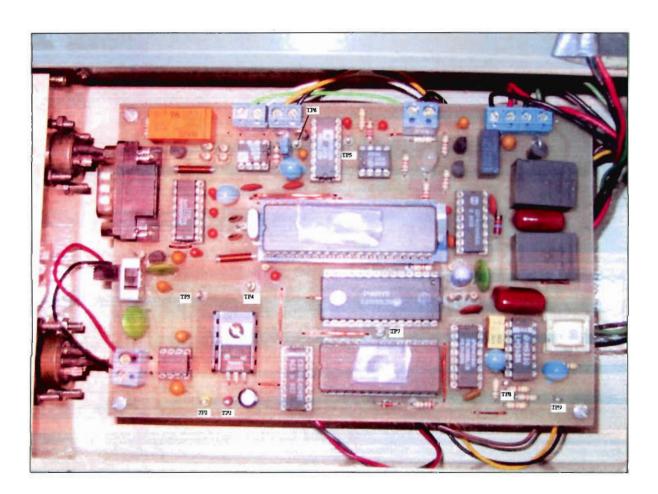

Para cumplir con los requerimientos anteriormente planteados se desarrollo el diseño de una tarjeta en base a un Microcontrolador MC68HC705C8A de la fabrica Motorola ya que se dispone del software necesario para su programación y a los PLL MC1451512 y 74HC4046. A continuación se dará una descripción detallada del diseño desarrollado

#### 2.2.1.- DIAGRAMA DE BLOQUES.-

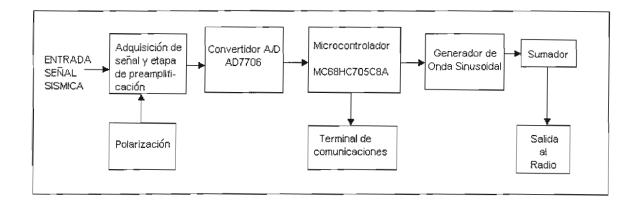

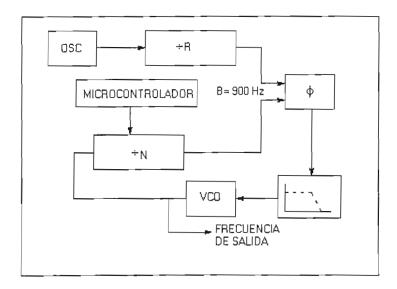

En la figura 2.1 se muestra el diagrama de bloques del sistema diseñado en el que se puede identificar las diferentes etapas del circuito:

Fig. 2.1 Diagrama de bloques del Oscilador Controlado por Voltaje con frecuencia y ganancia programable.

#### 2.2.2.- POLARIZACION.-

El VCO es parte fundamental del equipo que conforman las estaciones sísmicas, éstas generalmente se encuentran ubicadas en sitios remotos, donde no existe energía eléctrica; por lo cual el VCO se alimentará con baterías respaldadas por paneles solares. Esto obliga a usar como fuente de alimentación los niveles de una batería de 12 Vdc. Para conseguir los voltajes de polarización requeridos por la tarjeta se han incluido en el circuito un regulador de voltaje de 5 Vdc, 500 mA; el 78M05 y el inversor de voltaje ICL7662, para obtener –12 Vdc, con lo cual se cubren todos los voltajes de polarización necesarios en la tarjeta. Además se ha colocado un diodo para evitar la polarización inversa en la tarjeta, y un supresor de descargas eléctricas.

#### 2.2.3.- ETAPA DE PREAMPLIFICACIÓN.-

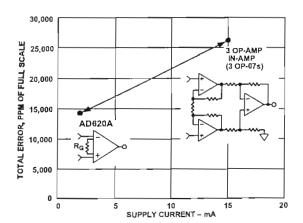

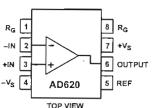

Esta conformada por el amplificador de instrumentación AD620 desarrollado por la Analog Device Inc. Este amplificador permite fijar la ganancia colocando una resistencia externa a su entrada, de acuerdo a la siguiente fórmula:

$$G = \frac{49.4k\Omega}{R_G} + 1$$

(ec 2.1 1)

Para el AD620 el valor de ganancia, puede ir de 1 a 1000. Para el presente diseño se ha escogido una resistencia de 390  $\Omega$  para obtener una ganancia de 127.66 es decir 42dB, cuando este colocado el jumper J1 en la tarjeta del VCO.

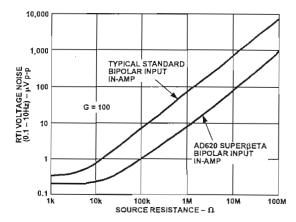

Internamente este amplificador operacional presenta seguidores de entrada de alta impedancia, bajo consumo de corriente (1.3 mA), y una reducción del voltaje de ruido a la entrada de 0.28 uV p-p en la banda de 0.1 Hz a 10 Hz.

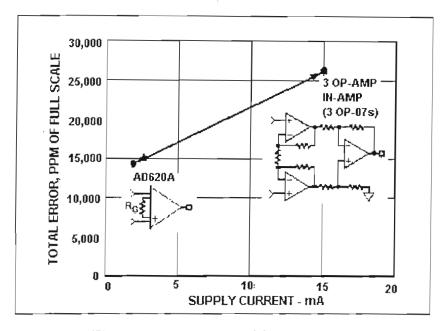

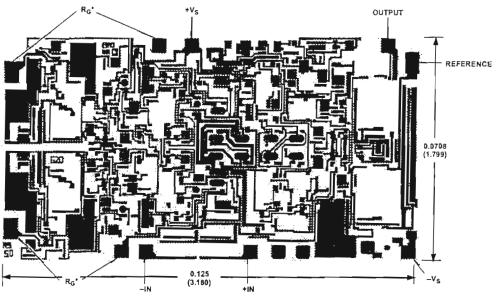

El AD620 nos proporciona un diseño con tres amplificadores operacionales en un arreglo de instrumentación, en un solo circuito como se muestra en la Fig. 2.2.

Posee un terminal de referencia lo cual nos permite colocar a la salida de la etapa preamplificadora un voltaje de 2.5V de referencia con el fin de centrar la señal alrededor de 2.5 V y de este modo, adaptarse al rango de entrada de la etapa de adquisición que es de 0 a 5 V, antes de su digitalización.

Fig. 2.2 Diseño interior del AD620

Para disminuir el problema del ruido por la línea de alimentación se ha colocado condensadores de tantalio y de cerámica así como inductores en serie a los voltajes de polarización.

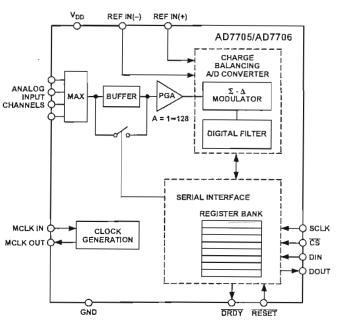

#### 2.2.4.- CONVERTIDOR ANÁLOGO DIGITAL.-

Para la etapa de conversión análogo digital, se uso el convertidor de tipo Sigma-Delta, el AD7706 de la Analog Device. Este dispositivo trabaja con una resolución de 16 bits y tiene un filtro pasabajos digital. Posee además del filtraje digital, de un proceso de autocalibración al encenderse, un pórtico serial

<sup>&</sup>lt;sup>1</sup> ANALOG DEVICE INC, AD620 Data Sheet, Pag. 10, USA 1999

sincrónico para comunicaciones bidireccional con el microcontrolador y la memoria de almacenamiento de parámetros de configuración. Su consumo de corriente es de 320 uA.

El convertidor AD7706 tiene 3 canales de entrada. El primero de ellos se utiliza en la señal sísmica, el segundo canal está libre para que se pueda digitalizar una señal de voltaje de propósito general como la que viene de un inclinómetro y; el tercer canal se ha destinado a medir el voltaje de la batería que alimenta al sistema.

#### 2.2.4.1.- Registros del AD7706.-

El AD7706, posee ocho registros de encendido de 8 bits, la programación enviada a estos registros permiten la configuración de los diferentes parámetros, la programación para cada registro se indicará en el siguiente capítulo y a continuación se detallará cada uno de los mismos:

#### 2.2.4.1.1.- Registro de Comunicaciones.-

Toda operación que se realiza en el AD7706 empieza con escribir operaciones a este registro, luego de polarizar; el integrado espera que se escriba a este registro, pues es el encargado de controlar el modo stand by, seleccionar el canal, decide cual es el siguiente registro a escribir o leer, si la siguiente operación a realizar es escritura o lectura, y muestra el estado del DRDY, esta bandera cuando esta en bajo indica que una nueva palabra esta en la salida del data register y retorna a 1 cuando se completa la lectura. Su estructura es:

bit7 bit0

| DRDY RS2 RS1 RS0 R/W STBY CH1 CH0 |

|-----------------------------------|

|-----------------------------------|

siguientes 7 bits van a ser cargados al registro de comunicaciones porque se ha indicado la operación de escritura. Si tiene un 1 indica una operación de lectura y provee el estado de la bandera DRDY del AD7706, tomando los mismos valores que ésta.

RS2-RS0 Son los bits de selección de registro. Estos tres bits indican cual de los ocho registros ha sido seleccionado para la próxima operación de lectura o escritura de acuerdo a la tabla No.2.1. Cuando la operación de lectura o escritura en el registro seleccionado ha finalizado, el AD7706 espera por una nueva instrucción de escritura al Registro de Comunicaciones.

DRDY Para indicar una operación de escritura debe estar en 0, entonces los siguientes 7 bits van a ser cargados al registro de comunicaciones porque se ha indicado la operación de escritura. Si tiene un 1 indica una operación de lectura y provee el estado de la bandera DRDY del AD7706, tomando los mismos valores que ésta.

RS2-RS0 Son los bits de selección de registro. Estos tres bits indican cual de los ocho registros ha sido seleccionado para la próxima operación de lectura o escritura de acuerdo a la tabla No.2.1. Cuando la operación de lectura o escritura en el registro seleccionado ha finalizado, el AD7706 espera por una nueva instrucción de escritura al Registro de Comunicaciones.

| RS2 | RS1 | RS0 | Registro                  | Tamaño  |

|-----|-----|-----|---------------------------|---------|

| 0   | 0   | 0   | Registro de               | 8 Bits  |

|     |     |     | Comunicaciones            |         |

| 0   | 0   | 1   | Registro de Configuración | 8 Bits  |

| 0   | 1   | 0   | Registro de Reloj         | 8 Bits  |

| 0   | 1   | 1   | Registro de Datos         | 16 Bits |

| 1   | 0   | 0   | Registro de Prueba        | 8 Bits  |

| 1   | 0   | 1   | No Operación              |         |

| 1   | 1   | 0   | Registro de Calibración   | 24 Bits |

| 1   | 1   | 1   | Registro de Ganancia      | 24 Bits |

Tabla No. 2.1 Selección de Registros para el AD7706

R/W Indica si la siguiente operación a llevarse a cabo en los registros es lectura (1) o escritura (0).

STBY Escribiendo 1 en este bit, el AD7706 permanece en estado dormido consumiendo solamente 10uA, sin perder su estado de calibración y

control de información. Escribiendo 0 en este bit el AD7706 permanece en operación normal

CH1-CH0 Selecciona el canal para la conversión de datos, de acuerdo a la Tabla No.2.2

| CH1 | CH0 | AIN   | Referencia |

|-----|-----|-------|------------|

| 0   | 0   | AIN1  | COMUN      |

| 0   | 1   | AIN2  | COMUN      |

| 1   | 0   | COMUN | COMUN      |

| 1   | 1   | AIN3  | COMUN      |

Tabla No. 2.2 Selección de canales para el AD7706

#### 2.2.4.1.2.- Registro de configuración.-

Determina el modo de operación, calibración, ganancia, selección de operación bipolar / unipolar, y modo de preamplificación interna. Cuando se realiza cualquiera de las calibraciones posibles, y una vez terminadas las mismas el AD7706 regresa al modo normal de operación. El DRDY se pone en alto cuando empieza la calibración y retorna a bajo cuando esta se ha completado disponiendo de una nueva palabra en el registro de datos. La estructura del registro de configuración es:

| bit7 |     |    |    |            |     |     | DitU  |

|------|-----|----|----|------------|-----|-----|-------|

| MD1  | MD0 | G2 | G1 | <b>G</b> 0 | B/U | BUF | FSYNC |

MD1-MD0 Selecciona el modo de operación de acuerdo a la tabla No. 2.3.

| MD1 | MD0 | Modo de Operación                                                                                                                                                                                                                                                        |

|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | Es el modo normal de operación                                                                                                                                                                                                                                           |

| 0   | 1   | Activa la autocalibración en el canal seleccionado en el registro de comunicaciones.                                                                                                                                                                                     |

| 1   | Ō   | Activa la calibración del cero en la escala en el canal seleccionado por el registro de comunicaciones. Esta calibración se realiza para el voltaje de entrada en el momento que es seleccionada, por lo cual este voltaje debe permanecer estable durante su ejecución. |

| 1   | 1   | Realiza la calibración de escala completa, se requiere que el voltaje de entrada permanezca estable durante su ejecución.                                                                                                                                                |

Tabla No. 2.3 Modos de Operación para el AD7706

**G2-G0** Estos bits seleccionan la ganancia a la cual trabajara el AD7706 de acuerdo a la tabla No. 2.4

| G2 | G1 | G0 | Ganancia Configurada |

|----|----|----|----------------------|

| 0  | 0  | 0  | 1                    |

| 0  | 0  | 1  | 2                    |

| 0  | 1  | 0  | 4                    |

| 0  | 1  | 1  | 8                    |

| 1  | 0  | 0  | 16                   |

| 1  | 0  | 1  | 32                   |

| 1  | 1  | 0  | 64                   |

| 1  | 1  | 1  | 128                  |

Tabla No. 2.4 Selección de Ganancia para el AD7706

B/U Con un 0 en este bit se selecciona la operación Bipolar. Con un 1 se selecciona la operación Unipolar

BUF Buffer de Control. Con un 0 en este bit, el buffer de entrada esta desconectado de la entrada análoga, la corriente en la línea del VDD es reducida. Con un 1 en este bit, el buffer de entrada esta en serie con la entrada análoga teniendo una fuente de alta impedancia.

FSYNC Filtro de Sincronización. Cuando este bit es alto, el nodo del filtro digital, el control del filtro, la calibración y el modulador análogo están en un estado de reinicio. Cuando este bit esta en bajo, el modulador y filtro empiezan a procesar los datos y una palabra valida esta disponible. El bit FSYNC no afecta la interface digital, y tampoco a la salida DRDY si esta en bajo.

#### 2.2.4.1.3. - Registro de Reloj. -

Permite seleccionar el valor de los filtros cambiando la frecuencia de muestreo, así como bits para determinar la frecuencia de reloj a la que trabaja. Su estructura es la siguiente:

| bit7 |      | bit0 |        |        |     |     |     |

|------|------|------|--------|--------|-----|-----|-----|

| ZERO | ZERO | ZERO | CLKDIS | CLKDIV | CLK | FS1 | FS0 |

**ZERO** Para que la operación del AD7706 sea correcta estos bits deben estar en bajo.

CLKDIS Bit deshabilitador del reloj master. Cuando este bit es 1, se deshabilita el reloj del pin MCLKOUT, forzando a este a permanecer en bajo. Cuando se utiliza el reloj en el pin MCLKIN, el AD7706 continua trabajando con su reloj interno, cuando se activa este bit. Cuando se usa el reloj entre MCLKIN y MCLKOUT el AD7706 deja de funcionar cuando este bit esta en alto.

CLKDIV Bit divisor de reloj. Cuando esta en 1 la frecuencia de reloj que esta en MCLKIN es dividida para dos. Cuando el bit es 0, la frecuencia presente en MLCKIN es la frecuencia de trabajo para el AD7706.

Bit de reloj. Este bit debe configurarse de acuerdo al CLKDIV. Por ejemplo si el reloj master es 2.4576 MHz (CLKDIV=0) o 4.9152MHz (CLKDIV=1) este bit debe estar en 1. Si el reloj master es de 1MHZ (CLKDIV=0) o 2MHZ (CLKDIV=1) este bit debe estar en 0. Este bit además proporciona la tasa de datos de salida conjuntamente con FS1 y FS0, si no esta configurado correctamente el AD7706 no trabaja.

FS1, FS0 Bits de selección de filtro. Conjuntamente con el CLK, seleccionan la tasa de salida de datos, así como fijan el nodo de -3dB de acuerdo a la tabla No. 2.5. El punto de - 3dB es determinado de acuerdo a la relación:

Filter-3dB frecuencia = 0.262 x primer nodo de frecuencia.(ec 2.2<sup>2</sup>)

| CLK* | FS1 | FS0 | Tasa de datos de salida | Punto de – 3dB |

|------|-----|-----|-------------------------|----------------|

| 0    | 0   | 0   | 20 Hz                   | 5.24 Hz        |

| 0    | 0   | 1   | 25 Hz                   | 6.55 Hz        |

| 0    | 1   | 0   | 100 Hz                  | 26.2 Hz        |

| 0    | 1   | 1   | 200 Hz                  | 52.4 Hz        |

| 1    | 0   | 0   | 50 Hz                   | 13.1 Hz        |

| 1    | 0   | 1   | 60 Hz                   | 15.7 Hz        |

| 1    | 1   | 0   | 250 Hz                  | 65.5 Hz        |

| 1    | 1   | 1   | 500 Hz                  | 131 Hz         |

Tabla No.2.5 Tasa de datos de salida para el AD7706

<sup>&</sup>lt;sup>2</sup> ANALOG DEVICES. AD7706 Data Sheet. Pag.13. 1998

#### 2.2.4.1.4.- Registro de Datos.-

Es un registro solo de lectura, que contiene el resultado de la conversión de datos cuando se enciende o se reinicia el componente, este registro tiene el valor 00Hex. Su estructura es:

RS2,RS1,RS0 = 0,0,1

#### 2.2.4.1.5.- Registro de Prueba.-

Es un registro solo de lectura y se usa para poder probar el componente AD7706, cuando se enciende o se reinicia, este registro tiene el valor 00Hex. Su estructura es:

RS2,RS1,RS0 = 1,0,0

#### 2.2.4.1.6.- Registros de Calibración.-

Existen dos registros para calibración, el primero es el registro de calibración de escala cero que como indica su nombre calibra el nivel cero cuando se enciende o se reinicia el componente, este registro tiene el valor 14F000Hex y su estructura es:

RS2,RS1,RS0 = 1,1,0.

El segundo es el registro de calibración de escala completa, que permite calibrar el máximo de la escala, cuando se enciende o se reinicia el dispositivo este registro tiene el valor 5761AB Hex y su estructura es: RS2, RS1, RS0 = 1,1,1.

Normalmente se realizan las dos calibraciones juntas para cada uno de los canales.

#### 2.2.4.2.- Ventajas del uso del AD7706

En los VCOs comerciales, se observa que la señal sísmica está directamente conectada al oscilador después de una etapa amplificadora, en este caso se hace la adquisición de la señal luego que pasa por una etapa preamplificadora e inmediatamente se la digitaliza, obteniendo varias ventajas que nos permite el dispositivo AD7706 entre ellas tenemos:

#### 2.2.4.2.1. - Mejoramiento de la Resolución. -

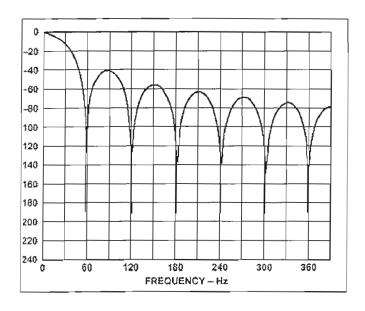

El convertidor mejora la resolución mediante "decimación", que es un tratamiento matemático que obtiene un valor de alta precisión a partir de varios valores de menor precisión (equivalente a obtener un promedio). Esta tecnología lleva implícito un nivel de filtrado que tiene la forma  $\left(\frac{\sin x}{x}\right)^3$ . La forma del filtro es función de la tasa de muestreo de los datos en bruto y la tasa de salida de los datos filtrados. Además es función de la relación entre estas dos tasas. Este parámetro es fijo para el convertidor, por lo que al seleccionar una tasa de salida de datos se especifica toda la forma del filtro. La forma del filtro es:

$$H(f) = \left| \frac{1}{N} \cdot \frac{\sin\left(N \cdot \pi \cdot \frac{f}{f_s}\right)}{\sin\left(\pi \cdot \frac{f}{f_s}\right)} \right|^3 \qquad \text{(ec. 2.3)}^3$$

Donde N es la relación entre la tasa de muestreo y la tasa de datos procesados y es un parámetro fijo. Los nodos del filtro ocurren en la frecuencia de salida y en sus múltiplos como se observa en la Figura No. 2.3.

<sup>3</sup> ANALOG DEVICE INC, AD 7706 Data Sheet, USA 1998

Fig. 2.3 Respuesta del filtro digital AD7706 para una tasa de muestreo de 60Hz

# 2.2.4.2.2.- Frecuencia de muestreo.-

Para la señal sísmica del VCO se han contemplado 4 frecuencias de muestreo como se indica en la tabla 2.6:

| Modo | Tasa          | Frecuencia de corte |  |

|------|---------------|---------------------|--|

|      | [Muestras por | (-3dB)              |  |

|      | segundo]      |                     |  |

| 0    | Sin señal     | -                   |  |

| 1    | 184           | 48 Hz               |  |

| 2    | 92            | 24 Hz               |  |

| 3    | 46            | 12 Hz               |  |

| 4    | 23            | 6 Hz                |  |

Tabla 2.6. - Frecuencia de muestreo

Debido a la frecuencia de corte, esta opción nos permite implementar un filtro pasabajos en los valores de 48, 24, 12 y 6 Hz; de manera similar al VCO comercial desarrollado por la Kinemetrics.

#### 2.2.4.2.3. - Ganancia. -

El AD7706 nos permite establecer ganancias que varían entre 1 a 128 es decir de 0 a 42 dB, a través de la programación requerida en el registro de seteo de acuerdo a la tabla 2.7:

| G2 | G1 | G0 | Ganancia |

|----|----|----|----------|

| 0  | 0  | 0  | 1        |

| 0  | 0  | 1  | 2        |

| 0  | 1  | 0  | 4        |

| 0  | 1  | 1  | 8        |

| 1  | 0  | 0  | 16       |

| 1  | 0  | 1  | 32       |

| 1  | 1  | 0  | 64       |

| 1  | 1  | 1  | 128      |

Tabla No. 2.7 Configuración de ganancia para el AD7706

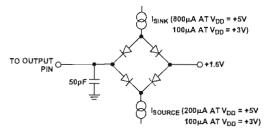

## 2.2.4.2.4.- Interface Serial.-

El AD7706 dispone de un interfaz serial compuesta de cinco señales de control que son:

CS Habilitación del componente

SCLK Reloj de entrada para transferir datos

DIN Ingresar datos al AD7706

DOUT Sacar los datos desde el componente

DRDY Nos permite conocer si hay un dato para lectura en el AD7706

A través de este interfaz serial es posible comunicarse con los registros del AD7706 para escribir o leer sus valores. Dicho interfaz en este diseño se encuentra comunicándose directamente con el Microcontrolador.

#### 2.2.5.- MICROCONTROLADOR.-

En el presente trabajo se utilizó el microcontrolador MC68HC705C8A, de fabricación Motorola Inc., que tiene de las siguientes características:

- Tecnología CMOS

- CPU de 8 bits

- 340 bytes de memoria RAM interna

- 240 bytes de memoria ROM interna

- 8 Kbytes de memoria programable EPROM

- 24 líneas de entrada / salida programables

- 7 líneas para el puerto de interfaz serial estándar y el interfaz de comunicación serial sincrónico

- Oscilador interno

- Contador interno de 16 bits

En el diseño descrito, el microcontrolador MC68HC705C8A cumple con varias funciones que se irán describiendo conforme se analiza su conexión en la tarjeta, así tenemos:

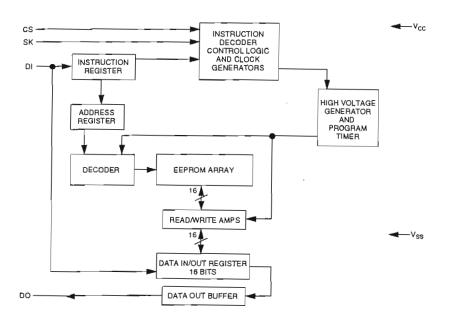

Las ocho líneas del pórtico A y las seis líneas del pórtico B se utilizan para comunicarse con el generador de señal sinusoidal. El microcontrolador lee desde la memoria EEPROM 96C53 el valor de la frecuencia central, los valores de gariancia de hardware que asigna al AD7706, el de ganancia de software que realiza por sí mismo, el período de control de batería, el período de transmisión de pluviometría, el período de transmisión de inclinometría o de otro sensor

conectado al canal análogo libre del AD7706 y el período de tiempo para pruebas de VCO e interrupción de la transmisión telemétrica.

Una vez que conoce el valor de la frecuencia central, el microcontrolador va leyendo los datos del AD7706 y va sumando el valor de la frecuencia correspondiente a la desviación guardando relación con 2.5 V para un máximo de 125 Hz, y escribiendo instantáneamente este valor hacia el generador de la señal sinusoidal. Es decir va realizando la modulación de frecuencia. El control del proceso de modulación mediante software del microcontrolador impide también que la señal se salga del canal asignado y permite limitar las saturaciones de un modo seguro.

La relación de ±2,5 V a ±125 Hz puede modificarse mediante software. Cambiar esta relación equivale a tener una ganancia adicional, estos nuevos valores de ganancia han sido denominados ganancia por software y varía entre 0 y 42 dB.

Las dos líneas restantes del pórtico B se comunican con la memoria EPROM donde se almacena la tabla de valores de la función sinusoidal para ubicar los valores de amplitud de la misma en caso de tener una, dos o tres componentes de señales sísmicas, en la memoria se han almacenado cuatro tablas de la función senoidal con diferentes amplitudes.

La primera línea del pórtico C (PC0) activa la memoria EEPROM 93C56A de la tarjeta para poder escribir o leer los valores a los cuales se ha configurado la tarjeta.

Las líneas PC1, PC2, y PC3 se comunican con el AD7706 para escribir en él los valores de ganancia, filtros, dan el valor necesario para la autocalibración cuando se inicia el funcionamiento o cuando se ha cambiado la configuración el VCO y leen los datos digitalizados del sensor cuando está en funcionamiento.

La línea PC4 activa el relé de entrada desconectando el sensor para realizar pruebas de funcionamiento de la tarieta de VCO.

Las líneas PC5 y PC6 activan el relé para interrupción de funcionamiento del radio de transmisión, en caso que se quiera mandar datos intermitentes. El microcontrolador con su reloj interno suspende momentáneamente la adquisición de la señal sísmica para dar paso a los valores de monitoreo del voltaje de baterías como también activa el relé para pruebas de transmisión, y de comprobación del VCO.

La línea PC7 enciende intermitentemente el led como comprobación de que el microcontrolador este trabajando.

El interfaz de comunicación serial, se comunica tanto con el AD7706 como con la memoria EEPROM 93C56 para escribir y leer los datos de funcionamiento.

Las líneas PD7, TDI y TDD se comunican con el integrado MAX232 para la salida de comunicación serial a la que tiene acceso el usuario.

Por último la línea TCAP sirve para contar los pulsos generados por un sensor pluviométrico en caso de requerirlo, suspende la adquisición de la señal sísmica y transmite el valor almacenado en el contador interno.

En el siguiente capítulo se describirá detalladamente el programa que permite su funcionamiento.

#### 2.2.6.- GENERADOR DE LA ONDA SINUSOIDAL.-

Antes de tratar el diseño que se realizó para el generador sinusoidal se requiere anotar varios conceptos teóricos como son osciladores, osciladores controlados

por voltaje y la teoría de phase look looped (PLL), que se han aplicado en el presente diseño.

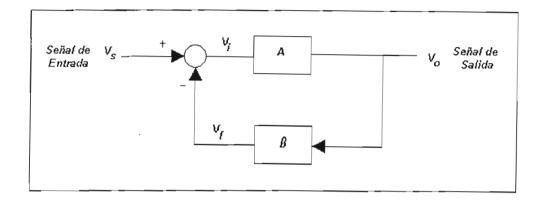

## 2.2.6.1- Operación del Circuito Realimentado como un Oscilador.-

El uso de realimentación positiva puede traducirse en que un amplificador realimentado tenga ganancia de lazo cerrada Af mayor que 1 y satisfaga las condiciones de fase que resultan en una operación como un circuito oscilador. Un circuito oscilador entonces proporciona una señal de salida variable en el tiempo. Si la señal de salida varia sinusoidalmente, se denomina oscilador sinusiodal. Si el voltaje de salida sube rápidamente a un nivel de voltaje y posteriormente cae rápidamente a otro nivel de voltaje, el circuito generalmente se denomina un oscilador de pulso o un oscilador de onda cuadrada.

Para explicar su funcionamiento consideremos el circuito realimentado de la Fig. 2.4, cuando el interruptor en la entrada del amplificador está abierto, no ocurren oscilaciones.

Consideremos que tenemos un voltaje ficticio a la entrada del amplificador ( $V_i$ ). Este se traduce en un voltaje de salida  $V_o$ =A $V_i$  después de la etapa amplificadora de base y en un voltaje  $V_i$ = $\beta(AV_i)$  después de la etapa de realimentación. Así tenemos, un voltaje de realimentación  $V_i$ = $\beta(AV_i)$ , en donde  $\beta A$  se conoce como ganancia de lazo. Si los circuitos del amplificador básico y la red de realimentación proporcionan  $\beta A$  en la magnitud correcta y fase adecuada,  $V_i$  puede hacerse igual a  $V_i$ . Entonces, cuando el interruptor se cierra y se retira  $V_i$ , el circuito continuará operando puesto que el voltaje de realimentación es suficientemente alto para excitar al amplificador y los circuitos de realimentación obteniéndose un voltaje de entrada adecuado para sostener la operación de lazo. La forma de onda de salida existirá después de que el interruptor es cerrado si la condición  $\beta A$ =1 se cumple. Esto se conoce como el Criterio de Barkhausen para oscilación.

En realidad no se necesita señal de entrada para que comiencen las oscilaciones. Solamente la condición  $\beta A=1$  debe satisfacerse para mantener las oscilaciones.

Fig. 2.4.- Circuito realimentado utilizado como oscilador

En la práctica  $\beta A$  se hace mayor que 1, y el sistema arranca a oscilar por el ruido que amplifica y que siempre se encuentra presente. Los factores de saturación en un circuito práctico proporcionan un valor promedio para  $\beta A$  de 1. Las formas de onda resultantes no son nunca exactamente sinusoidales. Sin embargo, entre más cercano este el valor de  $\beta A$  a la unidad más sinusoidal es la forma de onda.

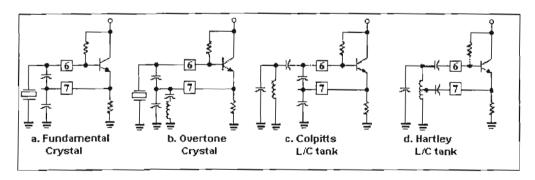

Algunos de los circuitos mas utilizados se muestran en la figura 2.5.

Fig No. 2.5.- Osciladores más comunes para la construcción de referencias.

## 2.2.6.2.- Oscilador Controlado por Voltaje.-

Un oscilador controlado por voltaje o VCO es un circuito que produce una señal de salida, generalmente una onda cuadrada, cuya frecuencia es proporcional al valor de un voltaje continuo aplicado en su entrada de control. Es decir, un VCO es un convertidor de voltaje a frecuencia. En condiciones normales un VCO opera a una frecuencia específica llamada frecuencia central fo. El VCO tiene un oscilador donde el principal elemento de sintonía es un diodo varactor, el voltaje de es aplicado directamente a este diodo cambiando la capacitancia del circuito y esto permite la sintonía a la frecuencia central.

El diseño de estos circuitos es relativamente fácil para algunos casos sencillos, sin embargo el mismo se complica en mayor o menor grado según la alternativa seleccionada y la tolerancia deseada en distorsión, rango dinámico, estabilidad, amplitud etc.

El VCO tiene gran aplicación en los sistemas de radiocomunicación generalmente forman parte de los circuitos osciladores de radio frecuencia RF y también en los circuitos osciladores de frecuencia intermedia FI.

# 2.2.6.2.1.- VCO con Oscilador Colpitts

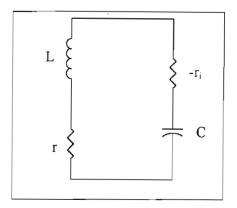

Uno de los circuitos osciladores más utilizados comúnmente es el Oscilador Colpitts, y por ello se desarrollarán sus expresiones a modo de ejemplo. Existe un método que se basa en el hecho de que un tanque LC con factor de calidad Q infinito, una vez excitado, oscilará de forma indefinida porque no hay una resistencia de perdidas que disipe la energía. En el caso actual donde el inductor tiene un factor Q finito, las oscilaciones desaparecen porque existe una resistencia que disipa la energía. Esta es la función del amplificador, mantener la oscilación suministrando una cantidad de energía igual a la disipada. Ésta fuente de energía se puede interpretar como una resistencia negativa r/ en serie con el circuito sintonizado, tal como se muestra en la figura 2.6. Si la resistencia total

es positiva, las oscilaciones desaparecerán, mientras que la amplitud aumentará si la resistencia es negativa. Para mantener la oscilación las dos resistencias deben ser iguales. Para ver como realizar una resistencia negativa, se derivará la impedancia de entrada de la figura 2.7.

Fig. 2.6. Circuito resonante con una resistencia negativa incluida.

Fig. 2.7. Circuito para generar una resistencia negativa.

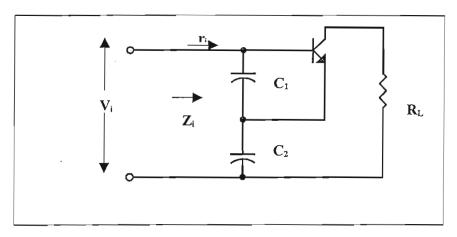

Si la impedancia del transistor es suficientemente grande, el circuito equivalente se muestra en la figura 2.8 y analizando las corrientes y tensiones del circuito se deducen las expresiones:

$$V_{i} = I_{i} (X_{C1} + X_{C2}) - I_{b} (X_{C1} - \beta X_{C2})) \text{ (ec. 2.4)}$$

$$0 = -I_{i} (X_{C1}) + I_{b} (X_{C1} + r_{\Pi}) \text{ (ec. 2.5)}$$

De las expresiones 2.4 y 2.5 se puede extraer la impedancia de entrada como:

$$Zi = \frac{Vi}{Ii} = \frac{(1+\beta)X_{C1}X_{C2} + r_{\Pi}(X_{C1} + X_{C2})}{X_{C1} + r_{\Pi}} \text{ (ec. 2.6)}$$

Si  $X_{CI} << r_{II_1}$  la impedancia de entrada es aproximadamente igual a:

$$Z_{i} \approx \frac{1+\beta}{r_{\Pi}} X_{C1} X_{C2} + X_{C1} + X_{C2} \approx \frac{-gm}{w^{2} C_{1} C_{2}} + \left[ jw \left( \frac{C_{1} C_{2}}{C_{1} + C_{2}} \right) \right]^{-1} \text{(ec.2.7)}$$

ccEsta es, la impedancia de entrada del circuito mostrado en la figura 2.7.

$$ri = \frac{-gm}{w^2 C_1 C_2}$$

(ec. 2.8)

$$Ci = \frac{C_1 C_2}{C_1 + C_2}$$

(ec. 2.9)

Fig. 2.8. Circuito en pequeña señal para el mostrado en la figura 2.7

Volviendo a la figura 2.6, con una inductancia L (con resistencia asociada r), la condición para que las oscilaciones se mantengan es que la resistencia r sea:

$$r = \frac{gm}{w^{-2}C_{-1}C_{-2}}$$

(ec. 2.10)

y la frecuencia de oscilación es:

$$f_o = \left[ 2\pi \left( L \frac{C_1 C_2}{C_1 + C_2} \right)^{1/2} \right]^{-1} \text{ (ec. 2.11)}$$

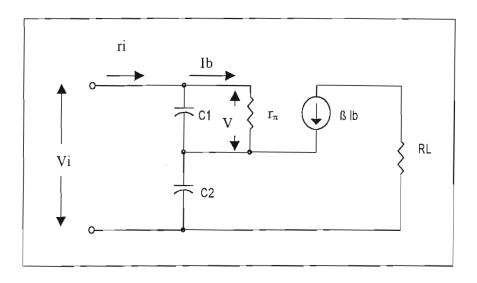

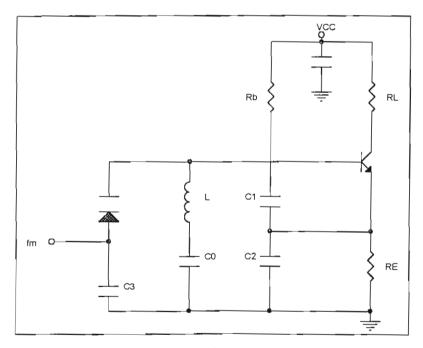

En el caso de desear una frecuencia de salida variable en función de una tensión de control  $f_m$ , sólo basta con realizar un montaje como el de la figura 2.9. La señal de control suele variar lentamente en el tiempo en comparación con la onda de salida, así que  $f_m$  se considera como contínua y en consecuencia el valor de la capacidad del varactor se considera constante.

Pudiendo aplicar el mismo análisis se llega a la conclusión de que la frecuencia de salida es:

$$W_o = \frac{1}{\sqrt{L \frac{(C + C_s)C_o}{C + C_s + C_o}}}$$

(ec. 2.12)

siendo

C<sub>s</sub> el paralelo de C<sub>1</sub> y C<sub>2</sub>.

Cola capacidad del varactor.

Fig. 2.9. Circuito de un VCO basado en un oscilador Colpitts

En los módulos comerciales para RF como parte del VCO se utiliza comúnmente el circuito oscilador Colpitts. Este oscilador es usado para un amplio rango frecuencias de operación, desde IF a RF.

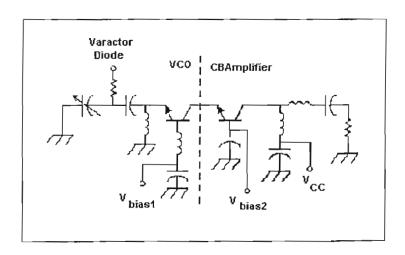

#### 2.2.6.2.2. - VCO con Osciladores de base - común

Los VCO's basados en amplificadores de base - común eran bastante utilizados hasta hace pocos años, estos circuitos tienen relativamente alta eficacia y un conveniente pero limitado ancho de banda. El inconveniente principal de estos osciladores es su tendencia a cambiar la frecuencia con cualquier variación en la carga, reflejado en una desviación de frecuencia. Un ejemplo de estos osciladores se muestra en la figura 2.10:

Fig. 2.10 VCO con amplificador base - común

# 2.2.6.2.3.- VCO con Oscilador de relajación (multivibradores acoplado en emisor)

Este VCO es el más usado en los diseños de Cl, el circuito oscila al cargar y descargar continuamente un condensador entre dos niveles de voltaje. Se

controla con un voltaje de control que suministra la corriente para cargar y descargar el condensador (fig. 2.11).

Aunque el multivibrador es relativamente simple y requiere de pocos dispositivos, la frecuencia de oscilación es parcialmente dependiente del capacitor, y este es bastante sensible a los efectos de la temperatura debido a la configuración de voltaje de acople por emisor.

Estos circuitos pueden presentar bastante rapidez, algunos presentan picos de hasta 7.4 Ghz

Fig. 2.11 VCO con oscilador multivibrador

Esta configuración acoplada en emisor es no saturada y contiene solo transistores NPN además dentro del circuito son pequeñas las variaciones de

voltaje. Aunque el circuito típicamente debería operar a altas frecuencias, la frecuencia utilizable es bastante limitada debido a un corrimiento de la frecuencia central por variaciones de la temperatura que se vuelven más grandes a frecuencias más altas. Esta sensibilidad a la temperatura se debe principalmente a las características de operación de los transistores y a la resistencia del circuito.

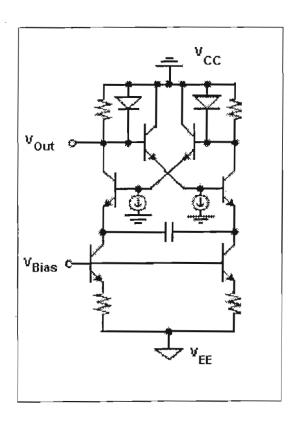

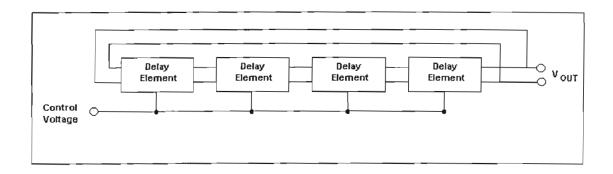

## 2.2.6.2.4.- VCO con Osciladores del anillo

El oscilador de anillo es diferente al multivibrador. El bloque principal del circuito básico es una celda de retraso no constante que está controlada por voltaje.

Al unir varios elementos de retardo el circuito oscilará con una frecuencia proporcional al voltaje de control, las celdas multiplican por dos el número de estados de retardo (el signo se cambia y debe pasar entonces dos veces por el mismo lugar para volver a su valor original).

Fig. 2.12 Oscilador de anillo básico controlado por voltaje

## 2.2.6.2.5.- VCO con Multiplicador de cuadratura

Es un multivibrador diferente. Los osciladores de anillo controlados por voltaje no son muy sensibles a los cambios de temperatura o cambios en los valores del condensador, por esto se crean los VCO de anillo con rendimientos de cuadratura múltiple que se usan para duplicar las frecuencias.

Este método permite tener dos señales fuera de fase 90° y consigue multiplicarlas para obtener dos veces la entrada en frecuencia.

Este método es utilizado en muchos PLL. El rendimiento de estos VCO hace posible multiplicaciones de factores de 4 e incluso más altos.

Para describir matemáticamente la multiplicación cuadrática de frecuencia considere un señal  $A = sin(w \ t)$ , y otra  $B = sin(w \ t + p \ / 2)$  que están 90° fuera de fase. Multiplicando las señales tenemos:

$$A*B = \sin(w t)*\sin(w t+p/2)$$

$$= \sin(w t) \cos(w t)$$

$$= \frac{1}{2} \sin (2w t) (ec. 2.13)$$

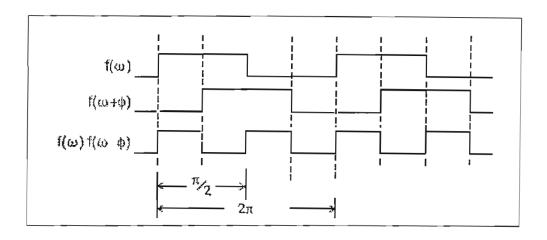

En la figura 2.13 se da una explicación más gráfica donde dos señales tienen la misma frecuencia pero una fase cambia 90°.

Cada señal tiene un valor alto o bajo solo en la mitad del ciclo, esto correspondería a un ¼ de 360°, por consiguiente las dos señales tienen el mismo valor a ¼ del periodo.

Se utiliza un circuito excluyente XOR y así se genera una frecuencia 2w.

Fig. 2.13.- Señales desfasadas 90°

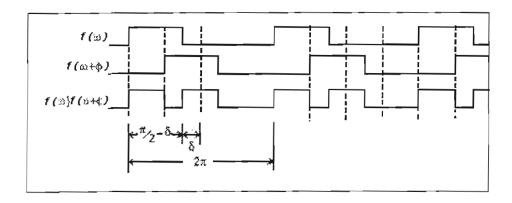

Se nota que para el primer impulso los dos ciclos están en fase, y tienen la misma frecuencia, el VCO está preparado para proporcionar una compensación de frecuencia ya que cualquier cambio en el ciclo será debido a un cambio de señal, el rendimiento de la señal se reduce a 2w en favor de la frecuencia más baja, cuando este es el caso. En la figura 2.14 vemos como en el primer ciclo se ha acortado por  $\delta$  mientras en el próximo ciclo aumenta por la misma cantidad. El problema es que las dos señales de entrada tienen ciclos diferentes

Fig. 2.14 Doblamiento de ciclo

Para generar una señal para los cuatro tiempos, la frecuencia del oscilador debe ser doblada de nuevo. Estos solo es posible cuando los las dos señales están dentro de la cuadratura de la frecuencia 2w.

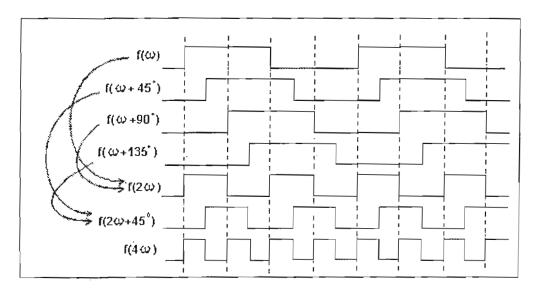

En la figura 2.15 se muestra un ejemplo de esto, las señales cuadradas del centro (0° y 90°, 45° y 135°) son separadas por una fase de retraso del oscilador. La señal tiene que pasar dos veces por los elementos de retraso para completar un ciclo que represente ½ (n/4), o 45°, entonces de un ciclo de 90° la fase se doblo y se combinó para generar una señal ahora de 4X de la frecuencia central.

Fig. 2.15. Oscilador de anillo con frecuencia de 2Xy 4X

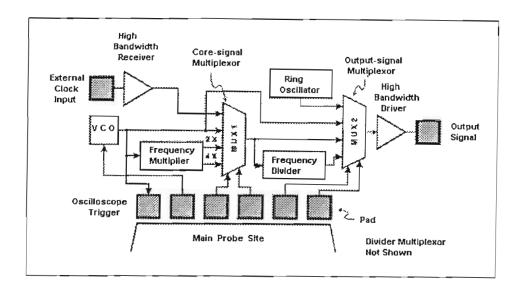

## 2.2.6.2.6.- VCO de alto nivel

Este es el nuevo avance en osciladores de alto rendimiento, está compuesto de un oscilador de anillo de retraso variable, el corazón de este VCO es un multiplicador y un divisor de frecuencia. Se alimenta de la señal central y aprovecha la naturaleza del oscilador cuadrático de anillo que genera signos a dos y cuatro tiempos respecto a la frecuencia central. El divisor toma una frecuencia central de la señal de entrada y la divide en múltiplos de 2, 4 u 8, además el VCO utiliza un oscilador de anillo de 24 estados.

Fig. 2.16 VCO de alto nivel

Tres multiplexores se incluyen para proporcionar varios caminos, como las oscilaciones externas pueden presentar problemas, se proporcionan en el Cl diversos puntos de chequeo de la señal.

El mutiplexor es el encargado de seleccionar un divisor adecuado para la frecuencia central, utilizando una señal de reloj que le permite elegir entre las señales de 2X y 4X.

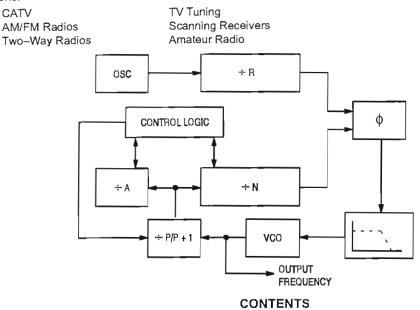

# 2.2.6.3.- Oscilador enganchado en fase PLL.-

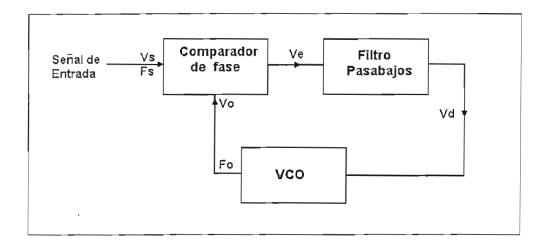

Un oscilador enganchado en fase también llamado lazo de amarre en fase o PLL (Phase Locked Loop), es un sistema de control de frecuencia constituido por un comparador o detector de fase, un filtro pasabajos y un oscilador controlado por voltaje VCO, interconectados como se indica en la Fig. No 2.17. El sistema opera en términos generales como sigue:

Fig No. 2.17 Estructura de un sistema PLL básico

En condiciones normales, sin señal de entrada, los voltajes de salida del comparador de fase (Ve) y el filtro pasabajos (Vd) son iguales a cero y el VCO oscila a una determinada frecuencia (Fo) llamada frecuencia central o frecuencia libre de oscilación determinada generalmente por circuito RC externo.

Cuando se aplica una señal de entrada, el detector de fase compara la frecuencia y fase de esta última (Fs) con la frecuencia del VCO y genera un voltaje de salida cuya magnitud es proporcional a la diferencia de fase de las dos señales. Este voltaje se denomina voltaje de error y controla, a través de un filtro pasabajo, la frecuencia del VCO. De esta manera, la tensión de control Vd(t) fuerza a que la frecuencia de oscilación del VCO varíe de manera que reduzca la diferencia de fase entre fo y la señal de entrada fs.

Como consecuencia de la existencia de un voltaje de error, se inicia un proceso de captura altamente complejo que tiene por objeto enganchar a la frecuencia del VCO con la de la señal de salida, es decir, hacerlas iguales. Para que esto suceda, la frecuencia de la señal de entrada debe estar dentro del rango de captura del PLL.

El rango de captura es una banda de frecuencias alrededor de la frecuencia central del VCO dentro de la cual el PLL puede engancharse con una señal de entrada.

Una vez enganchado un PLL, la frecuencia del VCO será idéntica a la de la señal de entrada y el voltaje de error será igual a cero. Si por alguna circunstancia la frecuencia de entrada cambia, el VCO variará automáticamente su frecuencia hasta conseguir el enganche. Esto será posible mientras la nueva frecuencia se mantenga dentro del rango de enganche del PLL.

El rango de enganche es una banda de frecuencias alrededor de la frecuencia central del VCO dentro de la cual un PLL puede permanecer enganchado con una señal de entrada previamente capturada. Por regla general, el rango de enganche es siempre mayor que el rango de captura.

# 2.2.6.3.1.- Enganche y captura.-

Considerando el caso de que el bucle no este enganchado el comparador de fase mezcla nuevamente las señales de entrada y del VCO produciendo componentes suma y diferencia de frecuencia. Sin embargo la componente diferencia puede caer fuera del ancho de banda del filtro pasa bajos y anularse al mismo tiempo con la componente de frecuencia suma. Si este es el caso, no se transmite ninguna información al VCO y este permanece en su frecuencia libre inicial.

Cuando la frecuencia de entrada se aproxima a la del VCO, la componente diferencia de frecuencias disminuye y se acerca el borde de la banda del filtro pasa bajo. Ahora alguna componente de la diferencia de frecuencias pasará, haciendo que la frecuencia del VCO se acerque a la frecuencia de la señal de entrada. Esto producirá, a la vez, que disminuya la componente de la frecuencia diferencia lo que permite que pase más información a través del filtro pasa bajo

hacia el VCO. Esto es esencialmente un mecanismo de realimentación positiva que provoca que el VCO se enganche con la señal de entrada.

Entonces se puede definir el término gama de captura como la gama de frecuencias alrededor de la cual, la frecuencia inicial del VCO puede enganchar con la señal de entrada. La gama de captura es una medida de que frecuencias de señal de entrada debemos tener para enganchar al VCO. Esta gama de captura puede llegar a tener cualquier valor dentro de la gama de enganche y depende en primer lugar del flanco del ancho de banda del filtro pasa bajo y en segundo lugar de la ganancia de lazo cerrado del sistema.

Es este fenómeno de captura de señal, el que le da al bucle, las propiedades selectivas de frecuencia. Es importante distinguir entre gama de captura y gama de enganche que puede nuevamente definirse como la gama de frecuencias normalmente centradas alrededor de la frecuencia inicial libre del VCO por el que el lazo puede encaminar la señal de entrada una vez logrado el enganche.

Cuando el lazo esta enganchado, la componente diferencia de frecuencia a la salida del comparador de fase (voltaje error) es un nivel de voltaje continuo y pasará siempre a través del filtro pasa bajo. Así, la gama de enganche estará limitada por la gama de voltaje de error que puede generarse y la correspondiente desviación de frecuencia producida por el VCO. La gama de enganche es esencialmente un parámetro DC y no está afectada por el ancho de banda del filtro pasa bajo.

#### 2.2.6.3.2.- Captura transitoria

A continuación se presenta una descripción cualitativa del mecanismo de captura. Sabiendo que la frecuencia es la derivada de la fase con respecto al tiempo, los incrementos (variaciones) de la frecuencia y de la fase en el bucle pueden relacionarse como df=dFe/dt donde, df es la variación de la frecuencia

instantánea entre las frecuencias de la señal del VCO, y Fe es la diferencia de fase entre la señal de entrada y la señal del VCO.

Si el lazo de realimentación del PLL se abriera entre el filtro pasa bajo y la entrada del VCO, entonces para una condición determinada de fo y fi la salida del comparador de fase sería un batido sinusoidal de una frecuencia fija df. Si fo y fi se acercaran suficientemente en su frecuencia, este batido aparecería a la salida del filtro con insignificante atenuación.

Supongamos ahora que el lazo de realimentación se cierra conectando la salida del filtro pasa bajo a la entrada del control del VCO. La frecuencia del oscilador VCO, estará modulada por este batido de frecuencia. Cuando esto sucede, df será una función de tiempo. Si, durante este proceso de modulación, la frecuencia del VCO se desplaza acercándose a fi (es decir, disminuyendo df), entonces dFe/dt disminuye y la salida del comparador de fase variará lentamente en función del tiempo. Del mismo modo, si el VCO se modula lejos de fi, dFe/dt aumenta y el voltaje de error, es decir, la salida del comparador de fase variará rápidamente en función del tiempo. Bajo esta condición la forma de onda de la nota de batido no será sinusoidal; sino que estará formado por una serie de picos aperiódicos.

A causa de su asimetría, esta nota de batido contiene una componente DC finita cuyo valor medio hace tender la frecuencias del VCO hacia fi y se establece el enganche. Entonces df vale cero y el voltaje de error DC permanece constante.

El tiempo total que tarda el PLL en establecer el enganche se llama el pull in time. Dicho tiempo depende de las diferencias de fase y frecuencia inicial entre las dos señales, así como también de la ganancia total de lazo y del ancho de banda del filtro pasa bajo. En determinadas condiciones, el pull in time puede ser más corto que el período del batido y el bucle puede cerrar sin ninguna oscilación transitoria.

# 2.2.6.3.3.- Efecto del Filtro Pasa Bajo

En la manera de comportarse el lazo. El filtro pasa bajo efectúa una doble función. La primera, atenuar y rechazar las componentes de alta frecuencia a la salida del detector de fase, mejorando las características de rechazo a interferencias, la segunda, proporcionar durante corto tiempo (memoria del filtro) al PLL asegurando un rescate rápido de la señal si el sistema se sale del enganche debido a algún ruido transitorio. Disminuir el ancho de banda del filtro pasa bajo tiene los efectos siguientes sobre el rendimiento del sistema (constante de tiempo grande):

- El proceso de captura llega a ser mas lento, y el pull in time aumenta.

- La gama de frecuencias de captura disminuye.

- Las propiedades de rechazo a interferencias del PLL mejoran ya que el voltaje de error ocasionado por una frecuencia perturbadora adicional se atenúa por el filtro pasa bajo.

- La respuesta transitoria del bucle (la respuesta del PLL a los cambios súbitos de la frecuencia de entrada dentro de la gama de captura) llega a ser muy amortiguado.

## 2.2.6.3.4.- Procedimiento general de diseño del filtro.

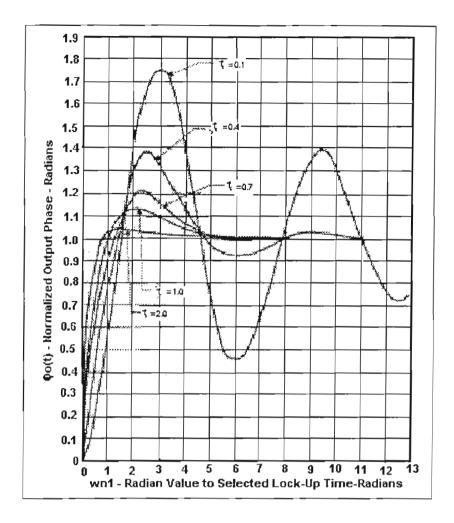

Tomando como base la respuesta del PLL a un escalón se determinarán el factor de amortiguación, la frecuencia natural y el tiempo de estabilización. La figura x2.18 muestra diversas curvas de respuesta para la función de transferencia del PLL. Como se puede observar un valor pequeño del factor de amortiguación hace aumentar el rizado, y un factor de amortiguamiento mayor disminuye las oscilaciones y por tanto el tiempo de estabilización.

Fig. 2.18 Respuesta a un escalón de un sistema PLL normalizado.

Para diseñar un sistema basado en PLL's,  $\xi$  se escoge primero. Luego de la curva de respuesta se extrae el valor de Wn.t al cual la respuesta está dentro de los márgenes del 5% del valor final. Posteriormente Wn.t se divide por el tiempo deseado de enganche para así determinar la frecuencia natural Wn. Los siguientes pasos deberían seguirse.

- (1)  $\xi$  es una medida de estabilidad y normalmente  $\xi$  es escoge entre 0.6 y 0.8.

- (2) Asumir ξ un valor de 0.7

- (3) El valor de Wn.t de la gráfica de la respuesta se determina como 4.5

- (4) El valor del tiempo de establecimiento to depende de los requerimientos del sistema.

- (5) La frecuencia natural Wn es por lo tanto:

$$W_n = \frac{W_n t}{t_s} = \frac{4.5}{t_s} (rad/s)$$

(ec. 2.14)

el criterio varia dependiendo de la aplicación. Es apropiado escoger o diseñar el sistema para que la frecuencia natural ( $fn=Wn/2\pi$ ) sea unas centenas superior a la frecuencia de referencia, fref.

- (6) El factor de división se determina de acuerdo con la frecuencia de referencia y la frecuencia deseada.

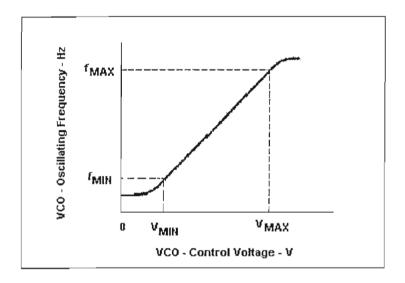

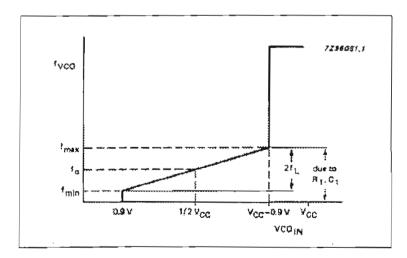

- (7) Determinar la ganancia, Kv del VCO. Un ejemplo de una característica de oscilación de un VCO se muestra en la figura 2.19:

Fig. 2.19 .Respuesta de un VCO.

De esta curva se extrae de forma simple la ganancia como:

$$K_{V} = \frac{f_{MAX} - f_{MIN}}{V_{MAX} - V_{MIN}} x2\Pi(rad/sec/V)$$

(ec. 2.15)

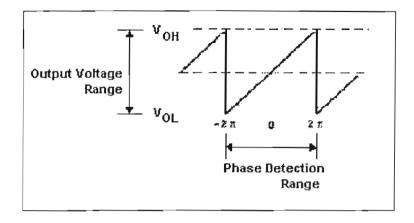

(8) Determinar la ganancia del detector de fase, Kp

Fig. 2.20. Respuesta del detector de fase.

Según la característica de salida del detector de la figura 2.20, la ganancia se puede expresar como:

$$K_p = \frac{V_{OH} - V_{OL}}{4\Pi} [V / rad]$$

(ec. 2.16)

Para otro tipo de detectores la ganancia Kp se determina de la misma forma

(9) Los parámetros del filtro se determinan sustituyendo cada uno de los valores determinados en los pasos del 1 al 8 en las correspondientes ecuaciones.

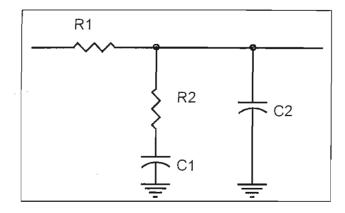

Para el filtro pasa bajo, sustituyendo Wn,  $\xi$ , Ny K, los parámetros del filtro se pueden encontrar fijando un valor apropiado de C1.

Para un filtro practico se suele usar un filtro de segundo orden añadiendo un segundo condensador C2, como se muestra en la figura 2.21. Se usa para eliminar señales no deseadas en la entrada del VCO.

Fig. 2.21. Filtro pasa bajos de segundo orden.

El valor de C2 debe ser inferior a C1/10 para que no afecte la característica del filtro pasa bajos, mientras se añade un filtro adecuado para ruido.

El condensador adicional C2 se usa para compensar la respuesta de R2 en alta frecuencia. La frecuencia de corte, Wc de C2 y R2 se escogerá de la siguiente forma:

$$W_C = \frac{1}{(C_2 * R_2)} \cong 10W_n \text{ (ec. 2.17)}$$

## 2.2.6.4.- Aplicaciones

El PLL puede utilizarse en una amplia variedad de aplicaciones, que comprenden: Demodulación de frecuencias, síntesis de frecuencia, decodificadores FSK, etc.

# 2.2.6.4.1.- Demodulacion de frecuencia.-

La demodulación de frecuencia o detección puede lograrse directamente utilizando el circuito PLL. Si la frecuencia central del PLL es seleccionada o diseñada como la frecuencia de portadora FM, el voltaje de salida filtrado en el circuito de la Fig 2.22 es el voltaje demodulado deseado, que varia proporcionalmente en relación a las variaciones de la frecuencia de la señal. El circuito PLL opera así como un conjunto completo de frecuencia intermedia (FI) limitador y demodulador como se utiliza en los circuitos FM.

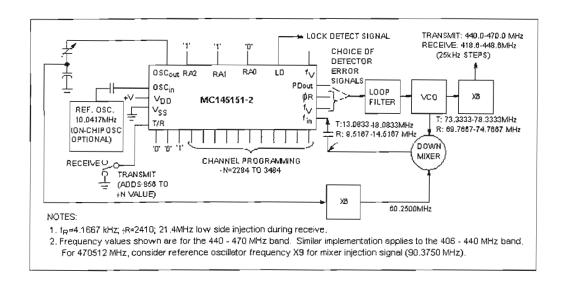

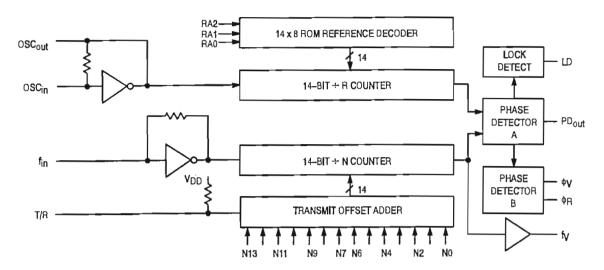

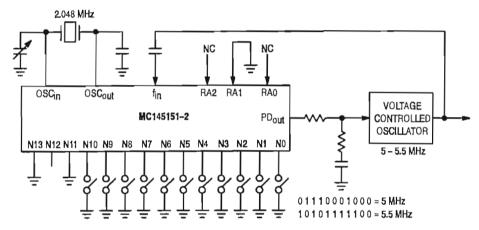

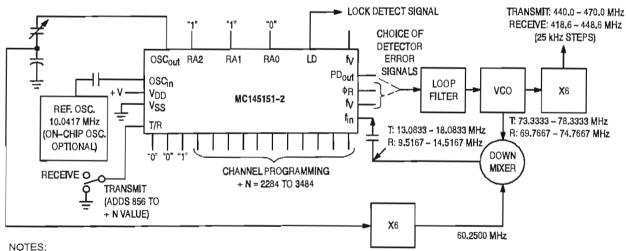

Fig. No. 2.22 Sintetizador para radio móvil UHF (Aplicaciones del MC145151-2)

#### 2.2.6.4.2. - Síntesis de Frecuencia

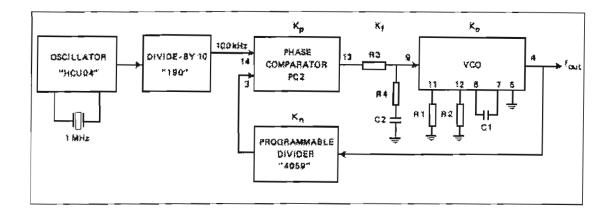

El término sintetizador de frecuencia se aplica a un dispositivo electrónico que acepta alguna referencia de frecuencia y se vale de esta para generar una o mas mediante una variable de control. La calidad de la frecuencia de salida se juzga mediante muchos factores, incluyendo la degradación que sufre el cristal de referencia a lo largo de la síntesis, pero para considerarse un buen sintetizador tendría que haber una perfecta correlación entre la referencia y la salida en cuanto a estabilidad y precisión

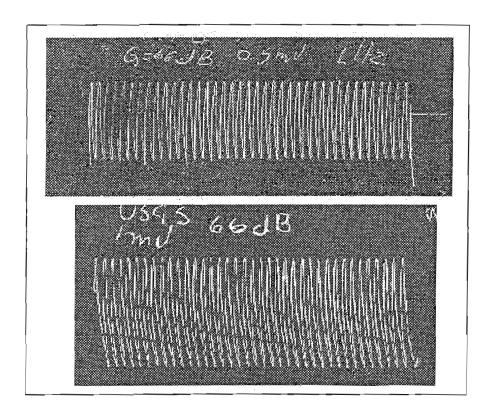

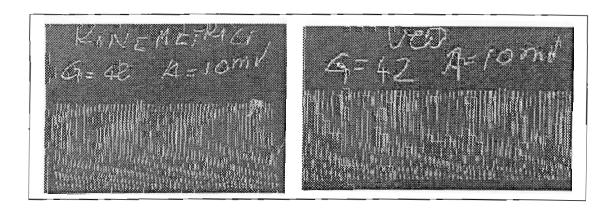

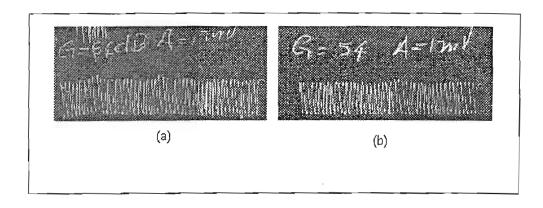

Los sintetizadores indirectos están diseñados en base a Phase lock loop o PLL's, comparan la salida de un oscilador controlado por tensión (VCO) con alguna referencia. Cuando la salida se desplaza se produce un error y se provoca una correlación sobre el VCO, el cual responde adecuadamente. La detección del error se lleva a cabo en el detector de fase, el cual introduce ruido de fase muy cercano a la portadora sobre todo cuando se pretende una precisión muy alta. Mediante este método se pueden alcanzar frecuencias muy altas, pero la conmutación entre frecuencias no es todo lo rápido que se quisiera